AXI总线详解-总线、接口以及协议

judy 在 周一, 08/31/2020 - 09:35 提交

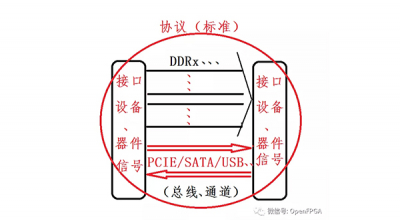

总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。总线是一组传输通道,是各种逻辑器件构成的传输数据的通道,一般由由数据线、地址线、控制线等构成。接口是一种连接标准,又常常被称之为物理接口。

总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。总线是一组传输通道,是各种逻辑器件构成的传输数据的通道,一般由由数据线、地址线、控制线等构成。接口是一种连接标准,又常常被称之为物理接口。

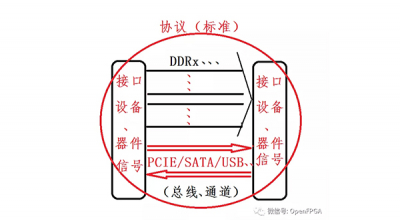

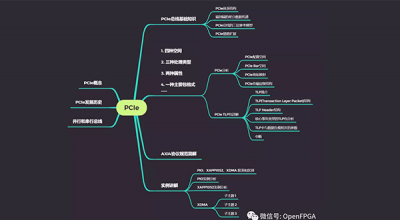

本来是在写PCIe,怎么突然又出现AXI了?不要急,先看下PCIe涉及到的知识点(初版),其中AXI协议也是PCIe知识体量中的一部分,所以先花一部分篇幅把AXI知识总结一下,具体如下:

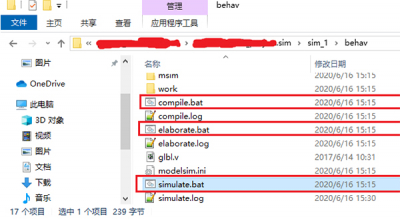

芯片设计从RTL代码一直到最后流片的GDSII文件,都是文本文件,因此,掌握文本分析处理语言是集成电路设计的一项重要的基本功。本文是孙义雯同学采用Python语言实现的Vivado和Modelsim联合仿真的自动化脚本,已经在实际项目中经过较长时间的检验,今天开源出来,供大家学习,欢迎留言交流心得体会和改进建议

PS 和外部接口之间的通信主要是通过复用的输入 / 输出( Multiplexed Input/Output,MIO)实现的,它提供了可以做灵活配置的 54 个引脚,这表明外部设备和引脚之间的映射是可以按需定义的。这样的连接也可以通过扩展 MIO (ExtendedMIO,EMIO)来实现

想成为一名FPGA工程师,对FPGA的结构是必须要掌握的。FPGA芯片主要是:可编程I/O单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块这六部分组成。

Python 是一种代表简单思想的语言,其语法相对简单,很容易上手。不过,如果就此小视 Python 语法的精妙和深邃,那就大错特错了。本文精心筛选了最能展现 Python 语法之精妙的十个知识点,并附上详细的实例代码

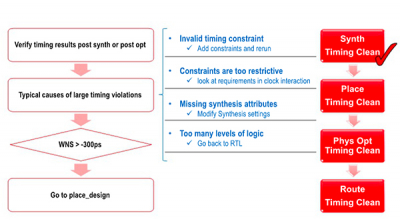

首先,我们要知道的是,Hold Time违例,是因为时钟绕的太远,到达时间太晚。而且综合之后给出的时序报告都是估计值,因此综合之后可以不考虑Hold Time,只考虑Setup Time;即便此时Hold Time违例,我们也不需要去理会

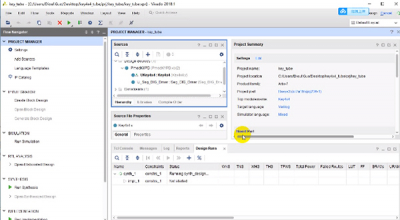

EDF文件可以直接导入Vivado,而无需Verilog源文件。

好处:

(1) 避免沙雕队友修改源代码,则可以直接提交EDF网表文件。

(2) 避免用户剽窃劳动成果,保护自己的知识产权。

(3) 对于无需更改的设计复用,直接用EDF网表会贼方便。

本文整理自Xilinx公开课:Vivado时序收敛技术。有些知识在公开课中讲的并不是很细,因此我又对其进行了整理,分为了几篇文章。

每次创建vivado工程时都会生成大量的文件,这样一方面导致占用的磁盘空间很大,另一方面也不利于vivado工程的copy和github上传等操作。这里教大家一个简单又实用的方法,将工程保存成xxx.tcl,只保留ip ,verilog/vhdl和xdc等必要文件即可。