AXI总线详解-不同类型的DMA

judy 在 周三, 09/23/2020 - 09:33 提交

几个常用的 AXI 接口 IP 的功能(上面已经提到):

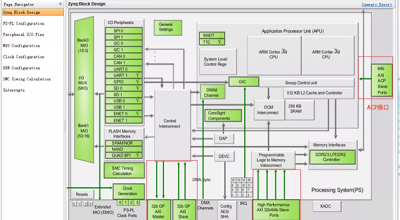

AXI-DMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换

AXI-FIFO-MM2S:实现从 PS 内存到 PL 通用传输通道 AXI-GP<----->AXI-Stream 的转换

几个常用的 AXI 接口 IP 的功能(上面已经提到):

AXI-DMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换

AXI-FIFO-MM2S:实现从 PS 内存到 PL 通用传输通道 AXI-GP<----->AXI-Stream 的转换

在ZYNQ的体系结构中定时器太丰富了,而大量的教程中基本就只玩了私有定时器,可以中断就OK了。其实在ZYNQ中定时器资源很丰富,每个CPU有自己的私有定时器和看门狗,有一个所有CPU共享的全局定时器和看门狗,两个三路定时器还有AXI_TIMER的IP可用,不过好像很少有博客把这些测试完。

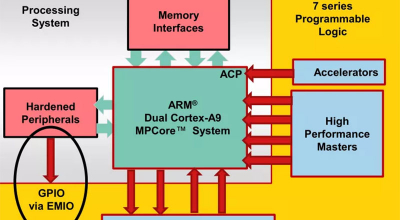

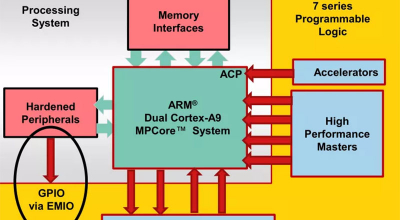

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI-Lite或AXI4转接。PS与PL之间的物理接口有9个,包括4个AXI-GP接口和4个AXI-HP接口、1个AXI-ACP接口

这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG的IP Core挂在Microblaze下,用很简单的程序就可以进行DDR3的测试。

这里主要介绍三种跨时钟域处理的方法,这三种方法可以说是FPGA界最常用也最实用的方法,这三种方法包含了单bit和多bit数据的跨时钟域处理,学会这三招之后,对于FPGA相关的跨时钟域数据处理便可以手到擒来

glitch:毛刺,glitch-free clock switching circuit:无毛刺时钟切换电路,今天讨论的主题就是如何实现时钟的无毛刺切换,本文将从有毛刺的时钟切换电路、无毛刺的源同步时钟切换电路、无毛刺的异步时钟切换电路三方面展开

AXI4协议基于猝发式传输机制。在地址通道上,每个交易有地址和控制信息,这些信息描述了需要传输的数据性质。主从设备间的数据传输有两种情况,一种是主设备经过写通道向从设备写数据(简称写交易),另一种是主设备经过读通道从从设备那里读取数据(简称读交易)

上面介绍了AMBA总线中的两种,下面看下我们的主角—AXI,在ZYNQ中有支持三种AXI总线,拥有三种AXI接口,当然用的都是AXI协议。其中三种AXI总线分别为:

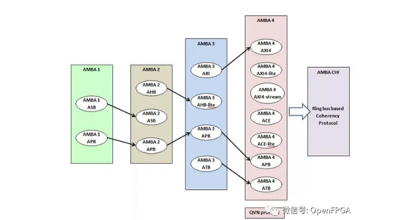

在基于IP复用的SoC设计中,片上总线设计是最关键的问题。为此,业界出现了很多片上总线标准。其中,由ARM公司推出的AMBA片上总线受到了广大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标准片上结构。AMBA规范主要包括了AHB(Advanced High performance Bus)系统总线和APB(Advanced Peripheral Bus)外围总线。

对 Vivado 和它的前一代设计套件,ISE 做一个组件功能上的平行比较和总结是很有用的。其目的是让那些具有在 ISE 下工作经验 (但是不具有 Vivado 下经验)的人能够更快的适应新工具的各个特性。详细信息见下表。