FPGA图像处理(8)常用算法:中值滤波去噪

judy 在 周二, 04/28/2020 - 09:13 提交

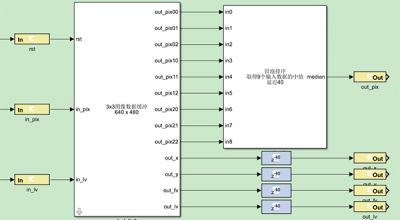

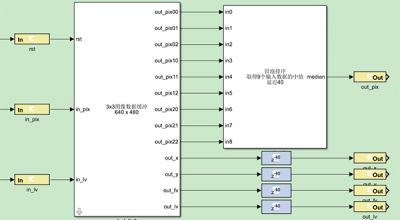

中值滤波是一种算法简单,效果较好的“高性价比”去噪算法。算法原理是使用图像内二维滑窗的中值(全部像素点数值排序位于中间位置的数值为中值)代替当前像素点值。如下图的 3×3滑窗内,处于滑窗中心的当前像素点值为 8,滑窗内全部 9 个像素点的中值为 5

中值滤波是一种算法简单,效果较好的“高性价比”去噪算法。算法原理是使用图像内二维滑窗的中值(全部像素点数值排序位于中间位置的数值为中值)代替当前像素点值。如下图的 3×3滑窗内,处于滑窗中心的当前像素点值为 8,滑窗内全部 9 个像素点的中值为 5

很多工程师都会选择多个jobs进行编译,以为这样会更快一些,而且这个jobs的数量跟本地CPU的线程数是一致的,这就更加让工程师们认为这个选项就是多线程编译了。但对Vivado更加熟悉的工程师,肯定会知道,Vivado中的多线程是通过tcl脚本去设置的,而且目前最大可使用的线程数是8个,那这个jobs跟多线程有什么关系呢?

前面我们实现了FPGA板卡接收以太网的数据,但是里面的数据比较乱,而且可能出现无效帧,即便是有效帧,也不是所有数据都是我们要的,必须对数据进行筛选。本篇博客详细记录一下以太网数据的校验和筛选。

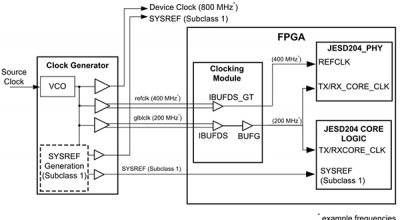

本篇参考xilinx官方JESD204 IP核的数据手册PG066,具体介绍基于该IP核的JESD204B数据传输实现方法~

电脑上位机将一幅 1024*768 图片通过双绞线(网线),发送给板卡网口(RJ45接口),RJ45接口将数据传输给网卡(PHY芯片),PHY 芯片将差分信号转换成双沿数据,IDDR将双沿数据转换成单沿数据传输给 FPGA

一直想移植高版本的ubuntu系统,但都是文本终端的,安装桌面操作总是出问题,没办法折腾一顿只能回来安装网上常用的12版本的。

本篇参考xilinx官方JESD204 IP核的数据手册PG066,具体介绍基于该IP核的JESD204B数据传输实现方法~

如上一篇最后提到的,最初接触PetaLinux也不懂,只能去尝试去找资料。我是通过用ZCU102的一个BSP去生成工程时,读到了其中的README,找到了如何去配置相应的开发板,只介绍Ultra96的相关配置问题。

经常听人说,Verilog或VHDL与HLS相比,就好比是几十年前的汇编语言与C语言,HDL迟早会被HLS取代的。这些话已经讲了有一二十年了,还是没有看到HLS取代HDL。本文翻译自2019年TCAD杂志上一篇综述,调研和对比了近年已发表论文中采用HLS和HDL的各种使用情况,值得一看。

在开发板上移植Linux系统,才能完整的实现嵌入式软硬件协同。之前对Linux开发没怎么接触过,只会点简单的操作。但对于移植Linux基本够了。PetaLinux的学习跟操作主要是依照手册ug1144和ug1157。