作者:咸鱼FPGA,文章来源:FPGA开源工作室

一、项目概况

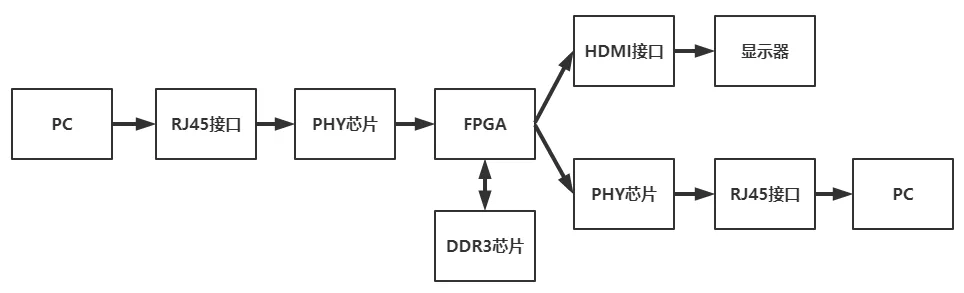

1、项目流程图

2、模块说明:

PC:个人电脑,有网线插槽的即可

RJ45接口:板卡上的网线插槽

PHY芯片:板卡上的以太网芯片,输入4对差分信号,转换为输出双沿4bit数据信号

FPGA:现场可编程逻辑门阵列,主控制器

DDR3芯片:第三代同步动态随机存取内存芯片,之前学过了

HDMI接口:高清多媒体接口,之前学过了

3、项目说明:

电脑上位机将一幅 1024*768 图片通过双绞线(网线),发送给板卡网口(RJ45接口),RJ45接口将数据传输给网卡(PHY芯片),PHY 芯片将差分信号转换成双沿数据,IDDR将双沿数据转换成单沿数据传输给 FPGA,FPGA 处理完成后将图像数据缓存到DDR3 中,DDR3 中的图像数据使用 UDP 协议传回 PC 机,同时将 DDR3 中数据使用 HDMI 传输到显示器上。

二、PHY芯片

详情参考 VSC8601-DS-r41-VMDS-10210 文档,该文档可以在 Xilinx 官网中下载。

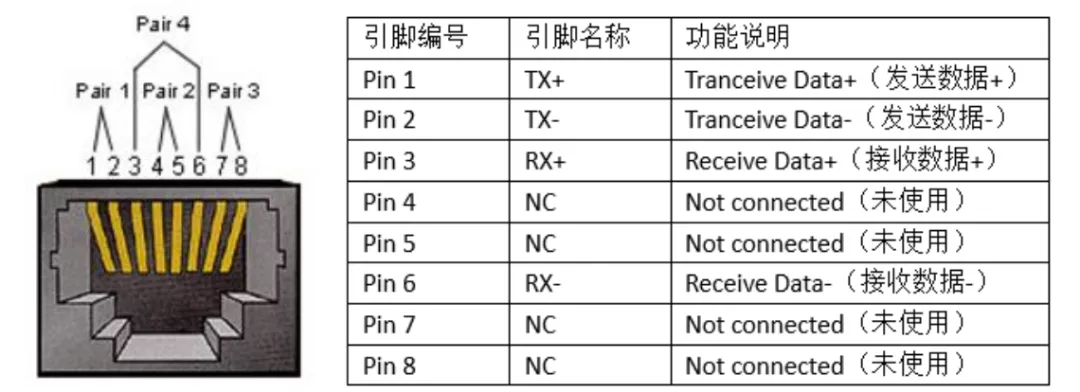

1、以太网和 RJ45 接口

以太网是一种产生较早,使用相当广泛的局域网。分类标准有标准以太网(10Mbit/s),快速以太网(100Mbit/s)和千兆以太网(1000Mbit/s)。随着以太网技术的飞速发展,市场上也出现了万兆以太网其技术支持10Gbit/s的传输速率。以太网连接端口:常见的以太网接口类型有RJ45接口,RJ11接口。SC光纤接口等。其中RJ45接口是我们常见的网络设备接口。

RJ45接口定义以及各引脚功能说明如下图所示,在以太网中只使用了1、2、3、6这四根线,其中1、2这组负责传输数据(TX+、TX-),而3、6这组负责接收数据(RX+、RX-),另外四根线是备用的。

总的来说,这一块部分知道即刻,不需要我们自己设计代码。

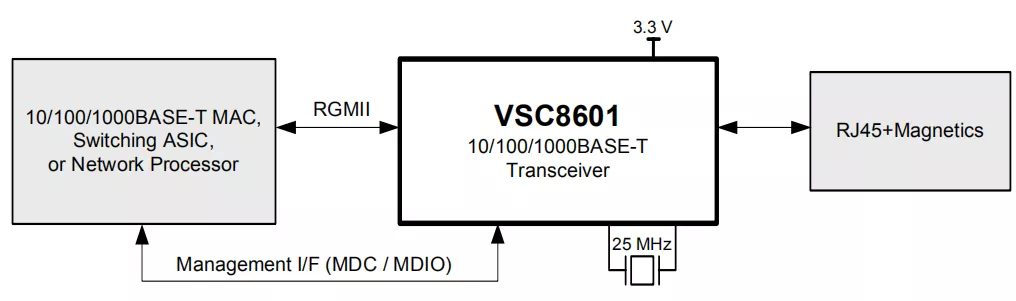

2、PHY 芯片介绍:

本项目使用 VITESSE VSC8601 网卡芯片,该芯片支持 10/100/1000 BASE-T,常用的网卡芯片有 VITESSE、高通等公司产品,该芯片通称为 PHY 芯片。该芯片与我们电脑、FPGA、MCU 等微处理器通信必须遵循 RGMII 协议。

3、PHY 芯片配置

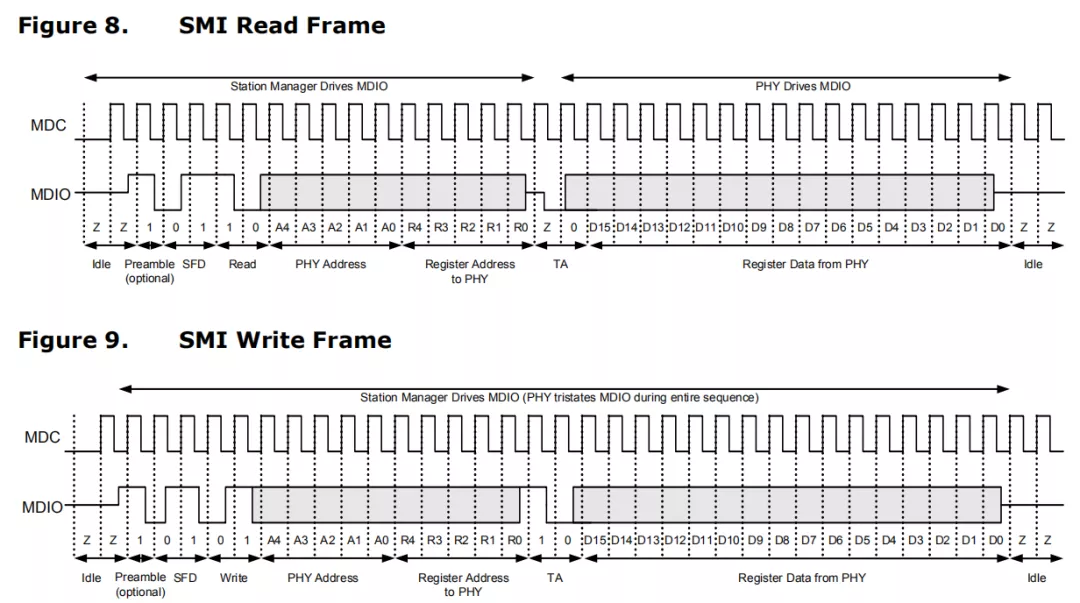

①SMI串行管理接口

VSC8601 设备包含一个 IEEE 802.3 兼容的串行管理接口(SMI),其中 MDC 和 MDIO 可对该芯片进行控制。SMI 提供了访问权限设备控制和状态寄存器。控制 SMI 的寄存器集由 32 个 16 位寄存器组成,包括所有需要的 IEEE 指定寄存器。此外,通过设备寄存器 31 可以访问寄存器的附加寄存器。SMI 是一个同步串行接口,其配置方式和 IIC 类似,MDIO 引脚具有有双向数据,在 MDC 信号的上升边缘上采集。MDC 采集速度应在 0 MHz 到 25mhz。数据通过 SMI 使用具有可选和任意长度前导的 32 位帧传输,下图(文档26页)显示了用于读操作和写操作的SMI框架格式。

由图可以看到 PHY Address 有 A0 - A4 共 5 bit,故一个处理器最多可以挂载这样的 PHY 芯片 2^5=32 个。用户可通过配置 PHY Address 或 Resgister Address 将该芯片按需配置。

②配置引脚和设备功能表(文档64页)

③相关引脚的功能,用于解释上表(文档65页)

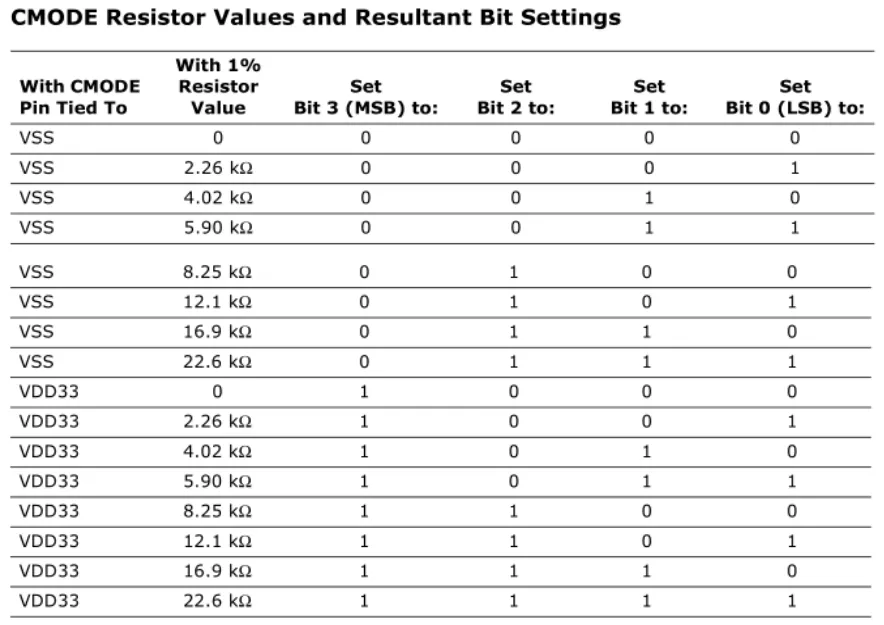

④电阻对应 Pin 值表(文档66页)

⑤PHY芯片配置

结合上面的表和 PHY 芯片的板卡原理图,即可确定出 CMODE Pin 的具体值了。

三、PHY芯片的初始化和RGMII协议

1、PHY 芯片初始化

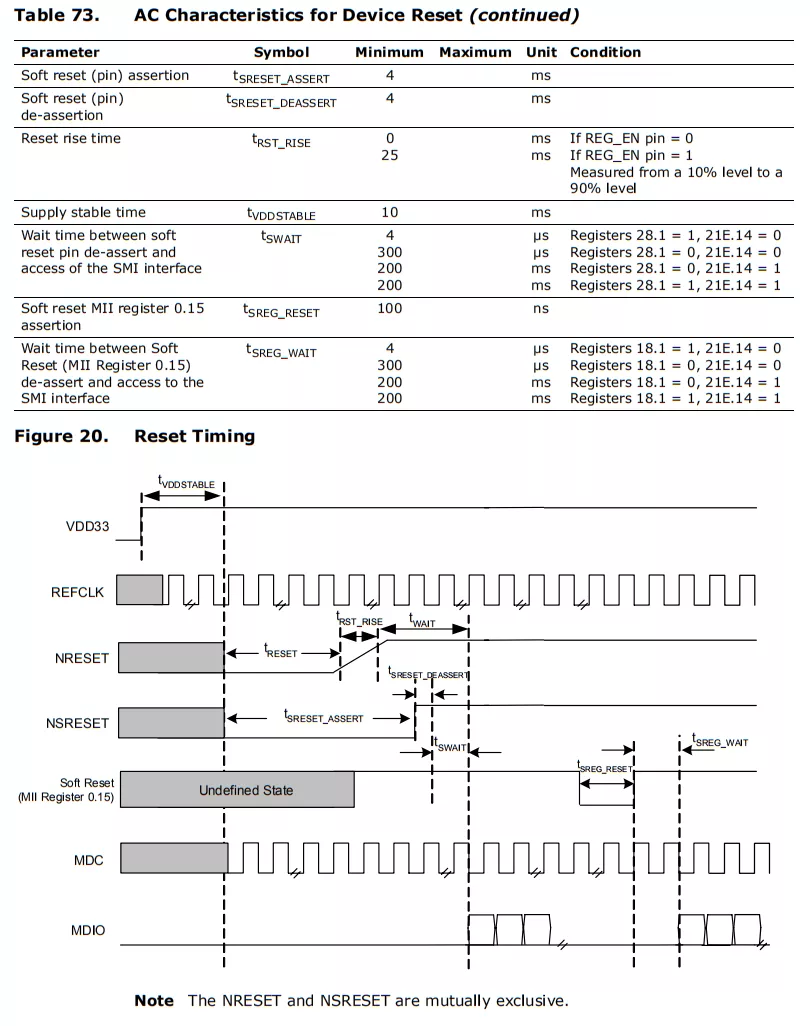

VSC8601 芯片上电后需要进行复位配置,该芯片复位信号需要在上电保持一段时间后才能将复位信号置为高,否则 PHY 芯片不会工作,其配置过程如图(文档79页)所示。PHY 的复位信号引脚和 FPGA 相连,当上电后至少经过 4ms 以上才可以将 PHY 芯片复位引脚置高,这样就完成 PHY 芯片初始化了,还是蛮简单的。

2、PHY芯片的RGMII协议

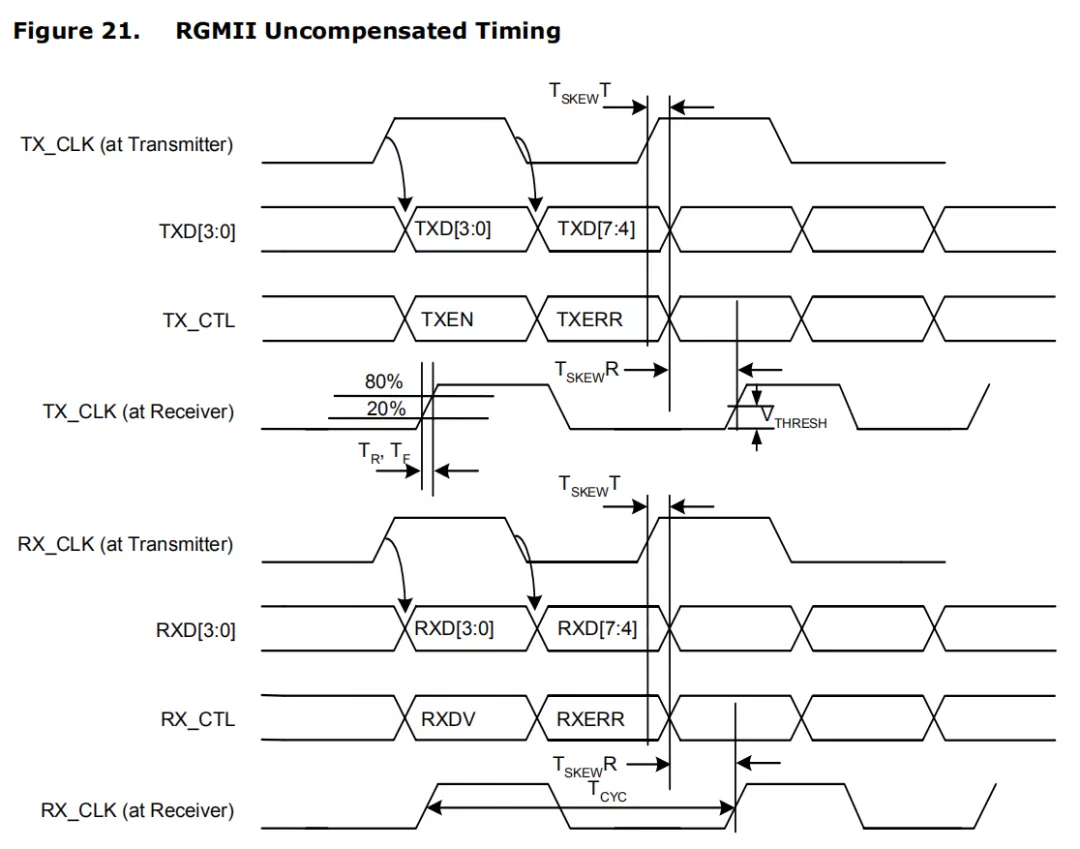

RGMII协议是PHY芯片和FPGA芯片之间的传输协议。RGMII 是 Reduced GMII(吉比特介质独立接口)。RGMII 均采用 4bit 数据接口,工作时钟 125MHz,并且在上升沿和下降沿同时传输数据,数据传输速率可以达到4*125*2=1000Mbps。同时兼容 MII 所规定的 10/100 Mbps 工作方式,支持传输速率:10M/100M/1000Mb/s ,其对应 clk 信号分别为:2.5MHz/25MHz/125MHz。RGMII 数据结构符合 IEEE 以太网标准,接口定义见 IEEE 802.3-2000。

PHY 芯片与 FPGA 数据交互的端口有:发射端、接收端及HPY 的复位端口。发射端和接收端分别有 6 个引脚与 FPGA 相连,分别有一个时钟引脚、一个数据控制使能引脚,四个数据引脚。而我们想要达到 1.0Gb/s 带宽,HPY 对应时钟为 125MHZ,若为单沿采样那么带宽为 125M/s*4=500Mb/s,及达不到 1.0Gb/s,在原有的硬件基础上想要使用 125M 时钟产生带宽为 1.0Gb/b,那么需要双沿控制采样数据,及时钟上升沿 4bit 下降沿 4bit,带宽为125M/s*4*2=1000Mb/s=1.0 Gb/b。该协议为 RGMII(Reduced Gigabit Media Independent Interface)。RGMII 均采用 4 位数据接口,工作时钟 125MHz,并且在上升沿和下降沿同时传输数据,因此传输速率可达 1000Mbps。RGMII 无补偿工作时序如图(文档81页)所示。

观察图中 RX_CLK(at Transmitter) 和 RX_CLK(at Receiver),RX_CLK(at Transmitter)为 HPY 时钟,在上升沿时对应输出数据为 RXD[3:0] 和 RXDV,在下降沿时对应出数据为 RXD[7:4] 和 RXERR,及一个时钟周期对应 8bit 数、一个有效使能和一个错误信号。RX_CLK(at Receiver) 是在 RX_CLK(at Transmitter) 的基础上相移 90°左右而得,这样采集到的数据会更加稳定。

四、IDDR原语

PHY 传输的数据为双沿数据,通常 FPGA 处理的为单沿数据,所以FPGA 接收到图像信息包后首先需要使用 IDDR 原语将双沿数据转换为单沿数据。通常情况下 FPGA 处理数据使用的时钟为晶振产生的时钟(FPGA 时钟),而 PHY 传输来的数据以及经过IDDR 原语后转换为单沿的数据都是和 PHY 的时钟同步,所以我们如果想使用 FPGA 时钟作为后续的图像数据处理必须要进行跨时钟域,将 PHY 时钟同步的数据转换为 FPGA 时钟同步的数据。此处双沿转单沿数据采用 Input DDR 原语,简称 IDDR,将双沿 4bit 数据转换为单沿 8bit 数据。

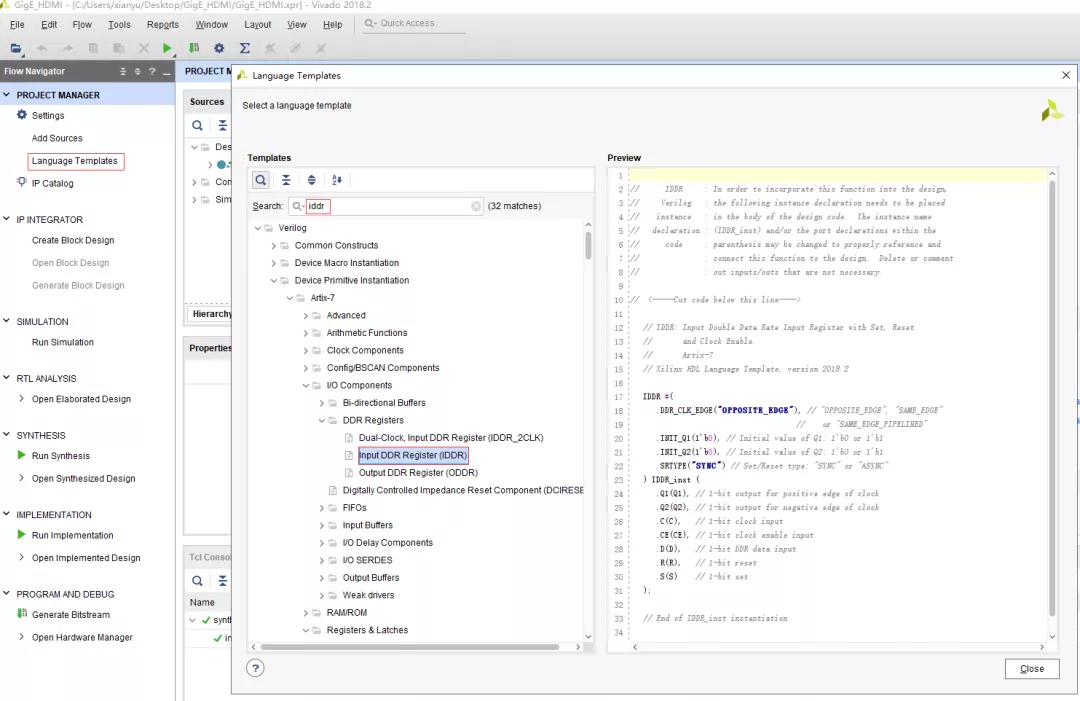

IDDR原语参考 7 Series FPGAs SelectIO Resources 文档和 Xilinx 7 Series FPGA Libraries Guide for HDL Designs 。

1、IDDR原语获取途径

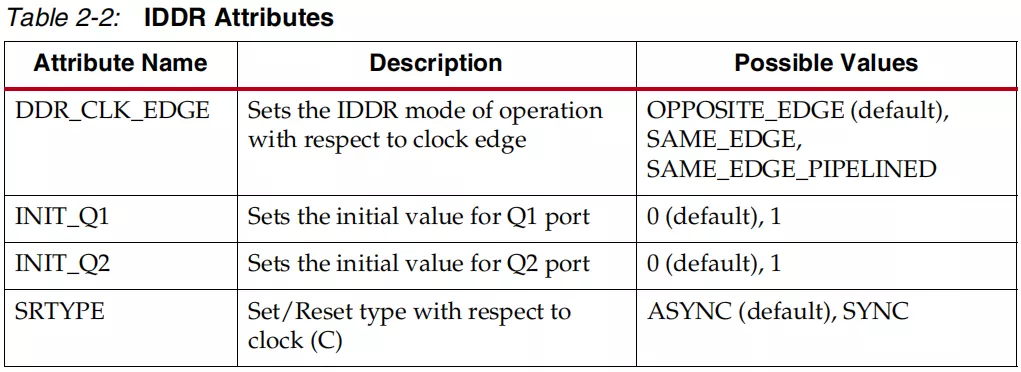

2、IDDR原语接口和属性(文档111页)

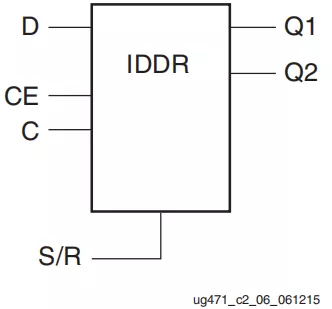

D 为数据输入,CE 为 IDDR 工作使能,C 为时钟,S 和 R 分别为置位和复位。

3、IDDR原语工作模式(文档110页)

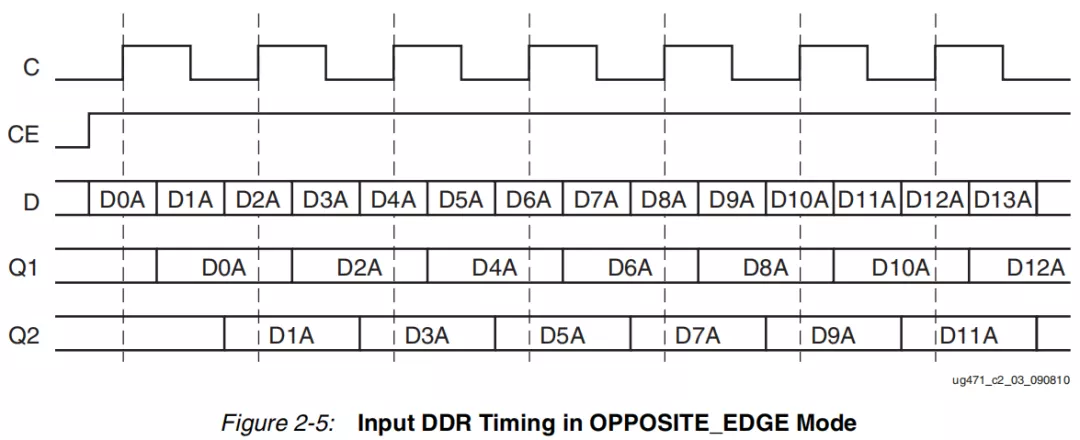

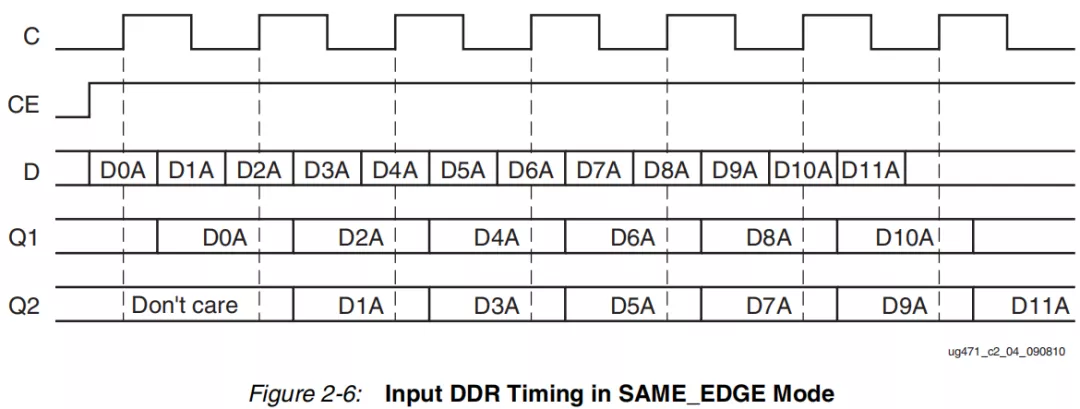

IDDR 有三种工作模式,模式配置如下图所示,分别为:OPPOSITE_EDGE、SAME_EDGE 、SAME_EDGE_PIPELINED。

通过对比三图差异,结合本项目平台选择模式:SAME_EDGE_PIPELINED。因为时钟上升沿和下降沿各对应一个数据,那么千兆以太网数据传输:0bit 和 4bit 为一组,1bit 和 5bit 为一组,2bit 和 6bit 为一组,3bit 和 7bit 为一组。

4、IDDR双沿数据转单沿数据使用方式

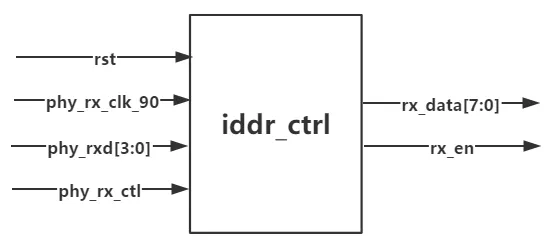

根据硬件电路图,PHY 传输给 FPGA 有一条时钟线、一条使能线和四条数据线,其中使能线和数据线都为双沿数据。一条使能线包含了 DV 和 ERR,其中上升沿传输的是 DV 信号(即数据有效信号),下降沿传输的为 ERR 信号(即数据出错信号,通常情况下不考虑 ERR,ERR 是由硬件引起,和软件无关);四条数据线包含了一个始终 8bit 数据,其中上升沿传输的是 8bit 数据中的[3:0],下降沿传输的是 8bit 数据中的[7:4]。 我们采用 IDDR 原语将双沿 4bit 数据转换为 8bit 数据,同时将 8bit 数据对应有效 DV 信号提取。那么可以建立实现双沿转单沿功能的模块:iddr_ctrl,其中输入与输出关系图如下所示。PHY 芯片传输来的 phy_rxd 和 phy_rx_ctl 都和 PHY 的时钟同步。图中 phy_rx_clk_90 为输入的时钟信号是 PHY 时钟相移90度后形成的,目的是采集 phy_rx_rxd 和 phy_rx_ctl 更稳定,rx_data 和 rx_en 即为该模块输出的单沿 8bit 数据和对应的数据有效使能。

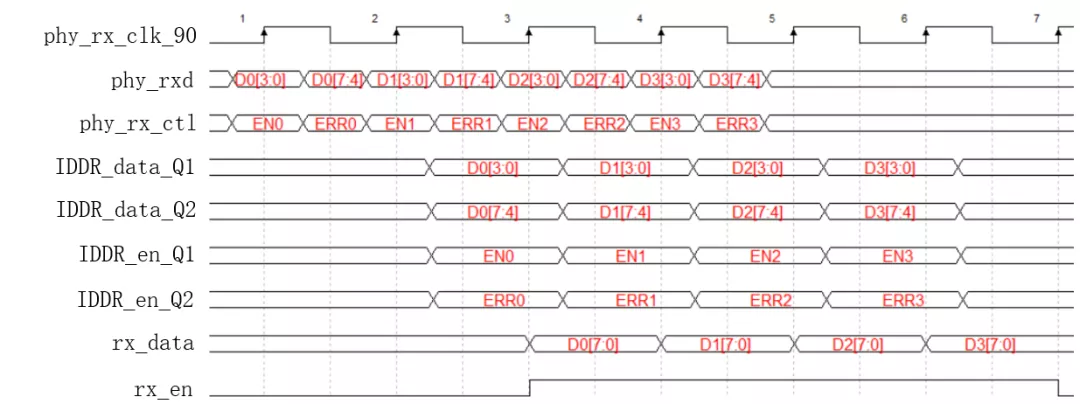

千兆以太网数据传输经过 IDDR 后 8bit 数据 rx_data 与使能 rx_en 对应关系如下图所示。

通过图可以看出,IDDR 时钟上升沿采集的 phy_rx_crl 信号为 EN(DV),代表数据有效,下降沿采集的为 ERR,代表数据错误,本项目此处不考虑错误信号,最终从 IDDR 输出的 rx_en 信号正好和拼接完成后的 rx_data 数据对应,即可作为 8bit 数据有效使能。

五、上板验证

代码写好后注意一下,前面说过 PHY 芯片初始化必须满足当上电后至少经过 4ms 以上才可以将 PHY 芯片复位引脚置高,因此顶层必须设置一下 PHY 芯片的复位引脚,该信号通过延时 4ms 即可产生,有了这个信号,PHY 芯片才能工作起来。

//延时 4ms 后启动 phy_rst_n

always @(posedge sclk) begin

if(rst) begin

phy_rst_cnt <= 'd0;

end

else if(phy_rst_cnt[18]==1'b0) begin

phy_rst_cnt <= phy_rst_cnt + 1'b1;

end

end

assign phy_rst_n = phy_rst_cnt[18];

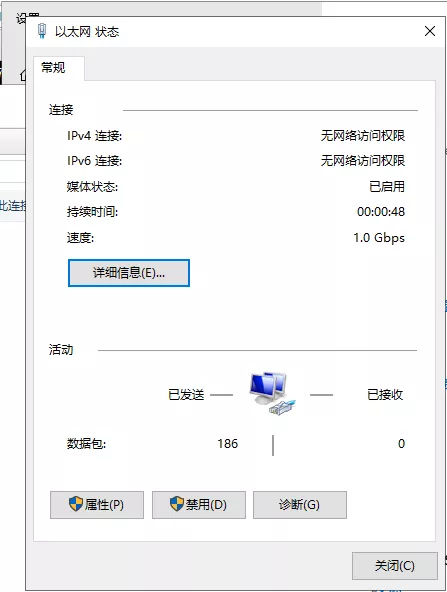

这次实验较简单,看不到任何现象,可以先生成一个 ila,将 rx_data 和 rx_en 放进去以待观察,最后不要忘记绑定引脚哦。生成bit文件后下载到板卡上,板卡上的网口和电脑网口连接,点击电脑中的 以太网设置 --- 更改适配器选项,即可看到网卡正常工作起来。

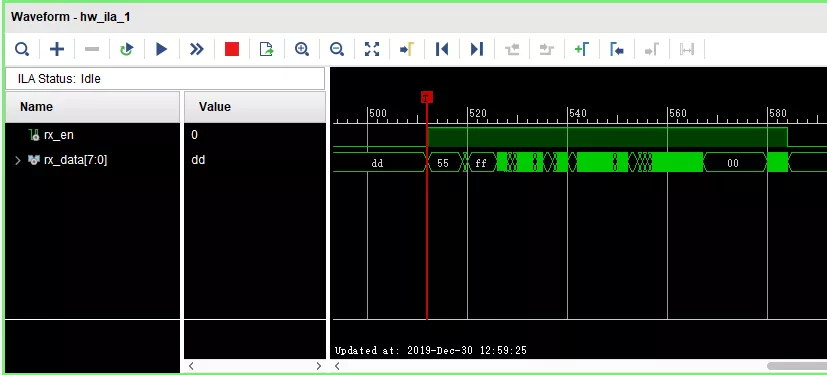

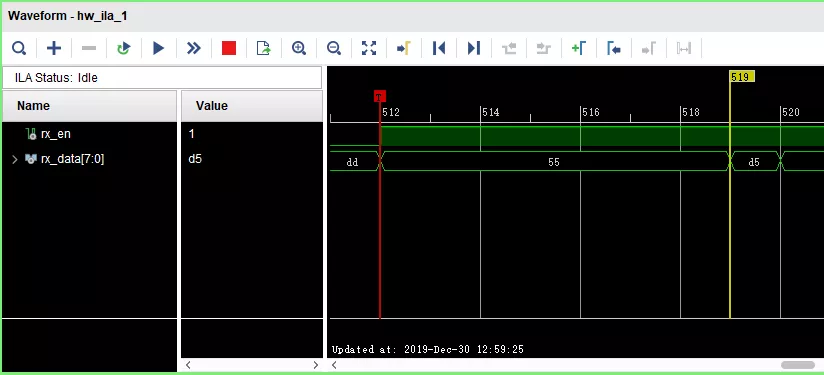

查看 ila,将 rx_en 的上升沿作为触发信号,得到如下波形:

如图可以观察到,千兆以太网数据以包为单位发送,每次发送有一定的数据,并且在每次发送前都会先发送 7 个 0x55 和 1 个 0xd5 作为包的针头,如果是这样的波形,那么表明此次试验设计成功。

参考资料:威三学院FPGA教程