SDSoC+ DVFS on ZC702

judy 在 周四, 05/30/2019 - 09:25 提交

该项目用2018.2版Vivado, SDSoC, Petalinux搭建,只适用于2018.2版本!

搭建环境:

Windows10: Vivado2018.2, SDSoC2018.2(也可以在Ubuntu16.04完成)

Ubuntu16.04: Petalinux2018.2

PYNQ-Z1/Z2, v2.1 img

该项目用2018.2版Vivado, SDSoC, Petalinux搭建,只适用于2018.2版本!

搭建环境:

Windows10: Vivado2018.2, SDSoC2018.2(也可以在Ubuntu16.04完成)

Ubuntu16.04: Petalinux2018.2

PYNQ-Z1/Z2, v2.1 img

说起xilinx的FPGA时钟结构,7系列FPGA的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如图1所示,理解了这张图,咱们就对7系列的FPGA时钟结构了如指掌,下面咱们就聊聊这张图

双核Zynq中共有20个PL到PS的中断。IRQF[15:0]是16个共享外设中断(SPI),可配选择上升沿触发或高电平触发,中断号为61-68和84-91。另外还有4个私有外设中断(PPI)IRQF2P[19:16],每个CPU都有一个来自PL的FIQ(快速中断)和IRQ,其中断敏感类型固定。

赛灵思公司的7系列FPGA根据不同客户的应用需求,分为4个子系列,即Spartan7系列、Artix7系列、Kintex7系列以及Virtex7系列。和前几代FPGA产品不同的是,7系列FPGA采用的是统一的28nm设计架构,客户在不同子系列的使用方式上是统一的,消除了不同子系列切换使用带来的不便

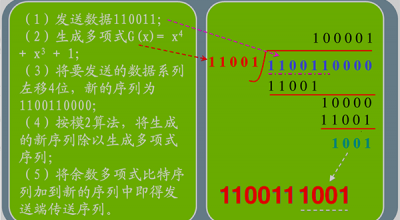

CRC校验的原理非常简单,其中,生成多项式是利用抽象代数的一些规则推导出来的,而模2加(也就是异或),是对应于有限域的除法。

本文简单介绍Zynq的中断系统和中断控制器。Zynq的PS部分基于ARM架构,使用了两个Cortex-A9处理器(CPU)以及GIC pl390中断控制器(单核Zynq则只有一个GIC)。GIC是通用中断控制器(Generic Interrupt Controller)的简称。双核的中断系统框图如下

在图像处理、计算机视觉领域,Lena数字图像被大多数的键盘侠广泛使用,Lena可以说是一张司空见惯的标准图。国外某期刊的主编,曾经说明过以下原因:1.Lena图像混合了各种细节、纹理特征、平滑区域和阴影部分,能够很好的测试图像处理的各种算法;2.Lena是个迷人的美女,做图像处理的研究者或工程师,大部分都是男的,不奇怪他们被Lena美女所吸引。

网络通信中的PHY芯片接口种类有很多,之前接触过GMII接口的PHY芯片RTL8211EG。但GMII接口数量较多,本文使用RGMII接口的88E1512搭建网络通信系统。这类接口总线位宽小,可以降低电路成本,在实际项目中应用更广泛。

SDK调试程序时都是通过JTAG,将PL的bit流文件和应用程序的ELF文件下载到Zynq中,运行查看效果。调试验证功能后需要将程序固化到板子上,使板子上电后可以从存储单元中加载程序,而无需SDK的调试环境。Zynq支持多种存储设备,本文将介绍如何将程序固化到常用的SD卡和QSPI Flash中

EMIO就是PS控制PL资源的简单例子。EMIO就是可扩展的MIO,当与PS直接相连的MIO不够用时,可以使用EMIO做“扩展”。使用体会上,感觉就是ARM直接控制了PL部分的管脚。GPIO的bank2和bank3就是通过EMIO接口与PL相连的,本文将先通过PS控制PL部分流水灯的实例感受下EMIO的使用,然后再介绍EMIO相关的基本概念