Xilinx 乘法器IP的使用

judy 在 周四, 04/25/2019 - 13:47 提交

软件工具: Vivado

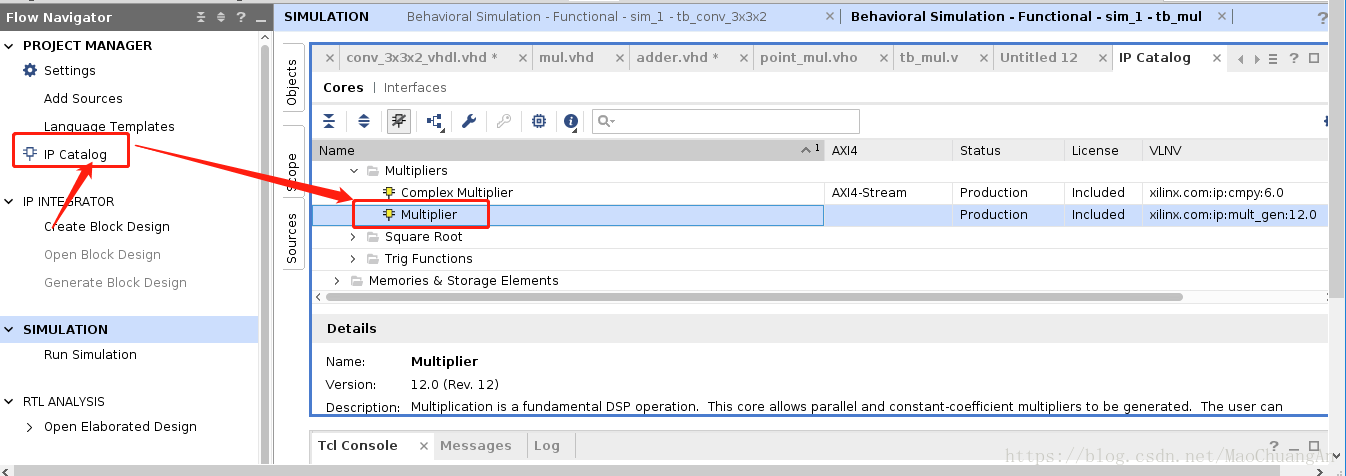

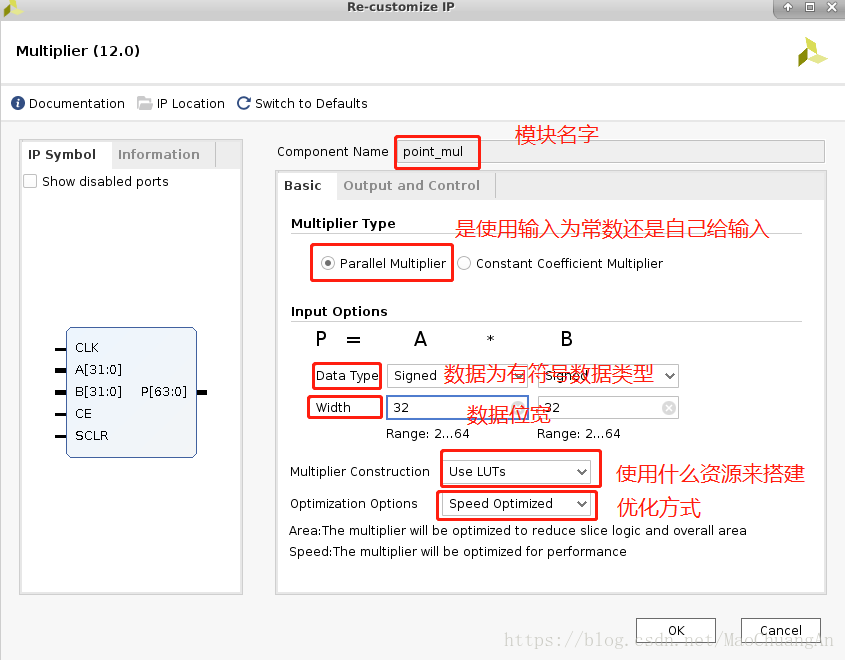

一、配置Multipiler

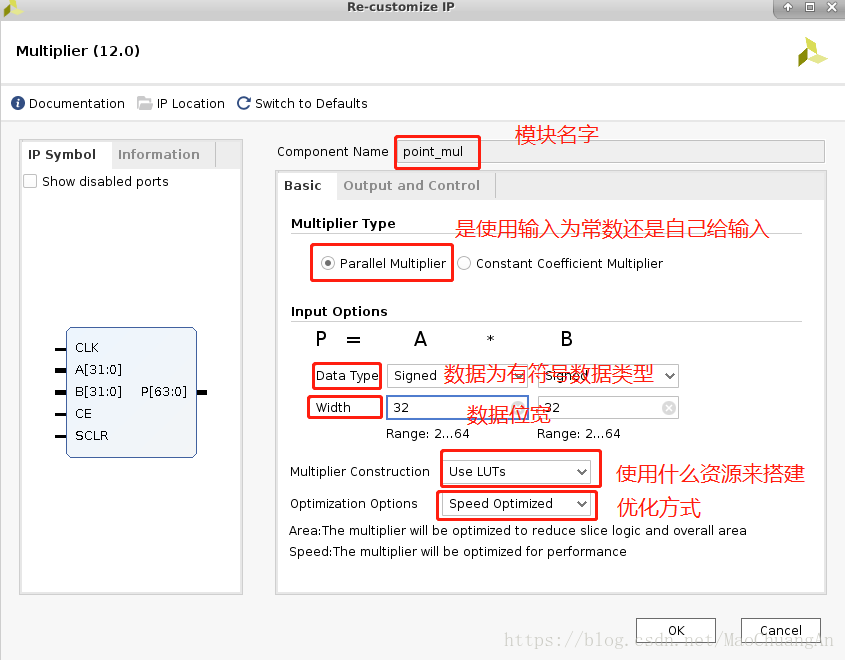

按照以下进行配置。

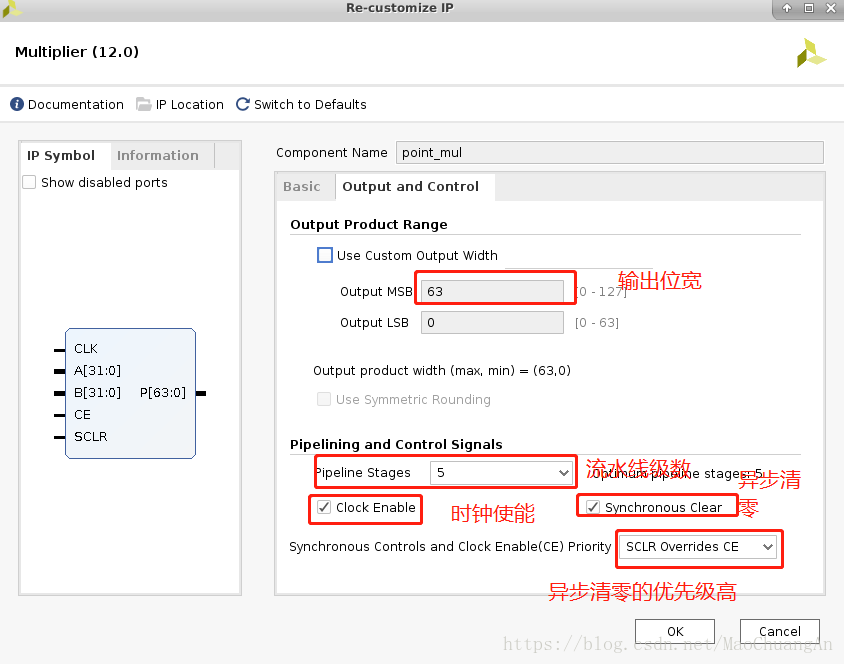

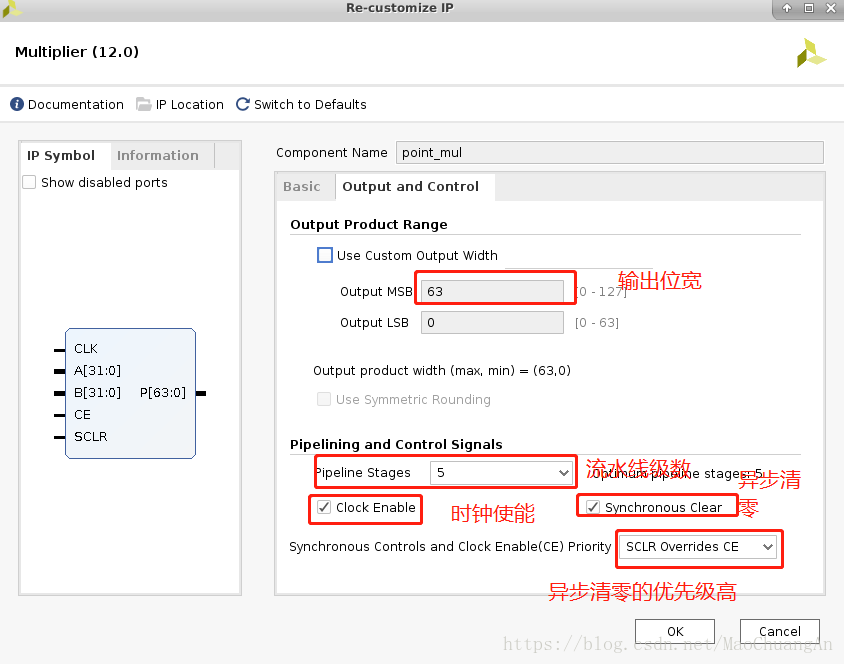

重点说一下流水线级数,这里选择5,说明时钟使能后5个周期可以输出结果。

二、编写代码

生成的模块:

软件工具: Vivado

一、配置Multipiler

按照以下进行配置。

重点说一下流水线级数,这里选择5,说明时钟使能后5个周期可以输出结果。

二、编写代码

生成的模块:

Xilinx的MPSoC系列芯片的部分型号提供了Video Codec Unit,可用于H.264/H.265格式视频的编解码。想要用起来Video Codec Unit需要花一番功夫,大体有三步:硬件层比特流的搭建,驱动层Linux内核+驱动的编译以及rootfs制作,应用层编译

本文将介绍PS部分GPIO中MIO的使用。本文先通过一个控制LED闪烁的实例体会MIO的用法,学习GPIO相关结构体与API函数的使用;然后再系统讲解GPIO的相关概念。

上文提到,进行最小/最大延迟约束时,set_max_delay和set_min_delay命令要设置-from和-to选项。但是如果起点和终点设置的不合理(具体见第33篇),便会导致出现路径分割(Path Segmentation)。

Vivado不支持即时分析有矛盾的时序异常,需要运行report_exceptions进行完整的分析,报告所有时序异常。多周期路径的情况有很多,比较复杂,单独放在第35篇中讲述。本文介绍其余三种时序异常的相关知识。

作者:liuyayong

1、实验方案

图1 实验方案系统框图

2、具体步骤

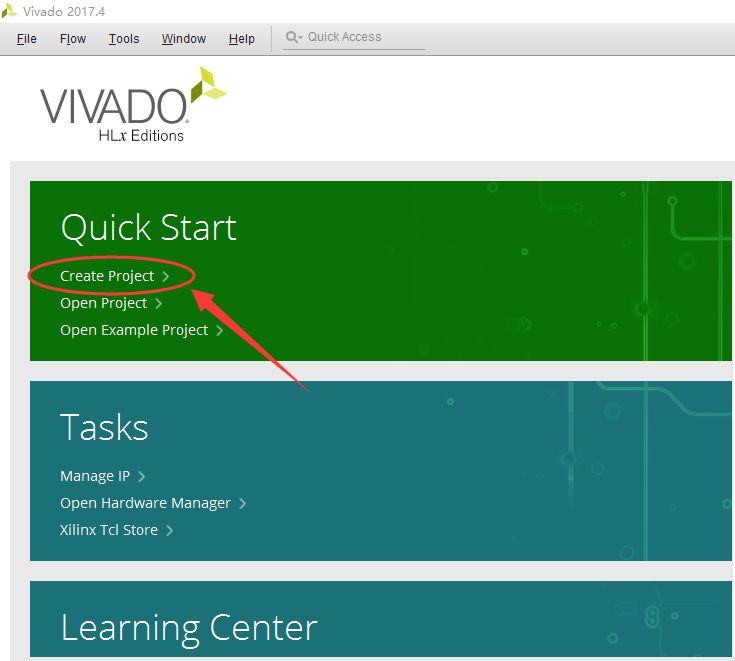

2.1、vivado工程建立

①打开vivado集成开发环境,点击“Create Project”,如下图所示。

②点击“Next”,如下图所示。

上一篇简单解释了Zynq配置的相关概念,本文将对Zynq-7000的软件开发进行简单介绍。如果设计者已经对ARM的开发方法很熟悉,上手Zynq的软件开发也会更快,相关概念理解起来也更快。

上电自复位对FPGA的稳定性及其重要,因为对于某些设计,上电之后需要进行一些状态寄存器的初始化,或者系统自己初始化都需要一个复位信号。在这里我就介绍一个比较好用的方法,大家一起学习一下

上一篇讲述了对时钟的约束方法,时钟不仅对设计很重要,约束情况也很多、很复杂,需要一定的经验。本文将讲述另一种重要的约束:I/O延迟,但与时钟约束相比就简单的多,本文篇幅也相对较少。

本文档系列是我在实践将简单的神经网络LeNet-5实现到Xilinx 的zynq-7z035的FPGA上遇到的问题和解决方法。本文档重点探讨vivado软件的使用。