FPGA Vivado调用IP核详细操作步骤

judy 在 周四, 05/09/2024 - 09:43 提交

今天给大侠带来Vivado调用IP核详细操作步骤,手把手教学,请往下看

今天给大侠带来Vivado调用IP核详细操作步骤,手把手教学,请往下看

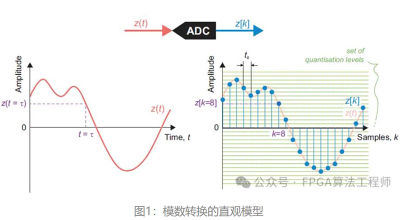

本文系摘录自《RFSoC SDR Book》第四章——DSP Fundamentals,略有改动。下面将介绍采样(Sampling)的基本概念

当使用ram时,width是960bit,depth是16bit,只有15Kb大小, 为什么占用了很多个BRAM?

在使用Vivado进行FPGA设计时,大家是否会遇到中文注释显示乱码的问题,而且在乱码时修改代码,导致文件注释更乱了,且恢复不了,那么如何解决呢?

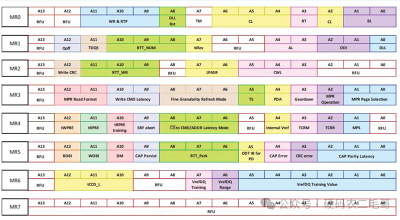

ddr在上电初始化后通过发送MRS命令配置模式寄存器。ddr上电后处于空闲状态时,可以发送MRS命令

本文介绍Xilinx SelectIO资源内部IDELAYE2资源应用

从专用串行数字接口 (SDI) 的点对点连接转到面向媒体内容交换和协作的以太网 IP 网络,这一颠覆整个广播媒体制作供应链的演进趋势仍在继续

本文介绍下Xilinx 7系列FPGA功功能特性、资源特性、封装兼容性以及如何订购器件。

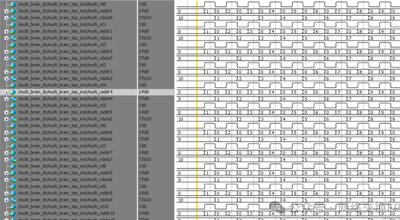

Multiport Ram,即多读多写存储器,本工程实现的是1个口写,同时满足11个口读的BRAM

上一篇介绍了BGA封装PCB层数估计、BGA焊盘设计、过孔设计、信号走线等内容,本文我们介绍下FPGA BGA封装电源管脚布线。