【Vivado那些事儿】使用Python提取ILA数据

judy 在 周三, 04/24/2024 - 09:33 提交

ILA应该是调试AMD-Xilinx FPGA最常用的IP。在调试中,我们希望ILA中的波形能够提供有关设计问题的所有信息,但情况并非如此

ILA应该是调试AMD-Xilinx FPGA最常用的IP。在调试中,我们希望ILA中的波形能够提供有关设计问题的所有信息,但情况并非如此

在工作中,我们接触到的至少90%以上的FPGA项目,它的的资源/时序都有很大的优化空间,为啥这么说?

Xilinx®Versal®体系结构、UltraScale™体系结构、7系列和6系列设备有多种封装,旨在实现最大性能和最大灵活性

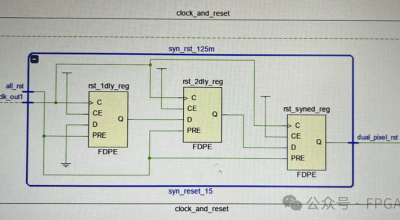

最近一个朋友私信我说,看了以前的写的复位设计,在自己的项目中设计了复位同步器用来实现异步复位同步解复位

DDR完成上电初始化后,将数据写入DDR要经过如下过程:ACT->WR->PRE

这篇文章我们看下Vivado的安装包中,到底哪些东西最占空间?

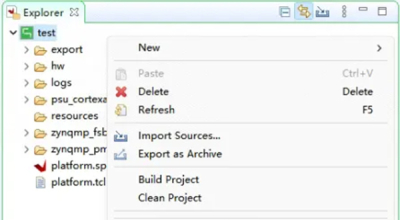

在使用Vitis开发时,当硬件设计发生变化时,这时就需要更新xsa文件。

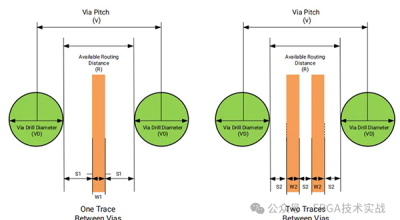

基于K7+C665x为核心的电路板中用到了DDR3存储芯片,现将FPGA外接DDR3时硬件设计中的一些心得做一个简单的分享

了解FPGA器件何时适合实现所需的系统功能是理解FPGA技术的关键要素。

本文将详细介绍vivado仿真功能,包括如何使用、测试激励文件的撰写,以及如何调用第三方仿真测试软件。