从FPGA说起的深度学习(三)

judy 在 周三, 02/15/2023 - 10:12 提交

在这篇 C++ 实现的第一篇文章中,我们开始针对卷积层的 C++ 实现

在这篇 C++ 实现的第一篇文章中,我们开始针对卷积层的 C++ 实现

本文主要介绍关于RF数据转换器的ADC状态指示函数的相关使用方法。

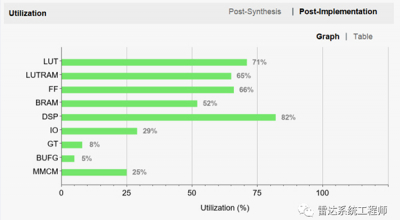

众所周知,中高端FPGA的电源中有两大耗电大户

AXI4 STREAM DATA FIFO也是一种先入先出形式的数据缓存队列

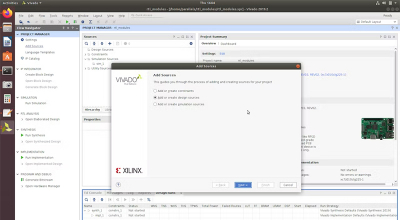

使用Vivado Block Design设计解决了项目继承性问题,但是还有个问题

在FPGA开发调试阶段,经常遇到这样的情况,需要临时添加信号,观察信号变化

本文主要介绍关于RF数据转换器的系统配置函数的相关使用方法。

本文介绍使用 FPGA 实现深度学习的技术

Vivado在打包IP核的时候提供了AXI4-Stream的接口,接下来分别例化两个IP

本文将解释“什么是深度学习”和“使用 FPGA 进行深度学习的好处”