RFSoC应用笔记 - RF数据转换器(11):RFSoC关键配置之其他功能(二)

judy 在 周二, 01/10/2023 - 16:59 提交

本文主要对RFSOC的时钟结构以及相关配置进行介绍,并简单介绍了关于复位的操作。

本文主要对RFSOC的时钟结构以及相关配置进行介绍,并简单介绍了关于复位的操作。

本节我们介绍FPGA收发器RX以下相关内容:RX字节和字对齐,RX弹性缓冲器。

今天就通过一个简单的工程来看下如何在vivado软件中查看时序报告

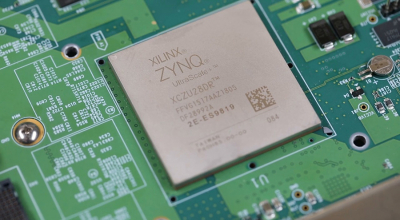

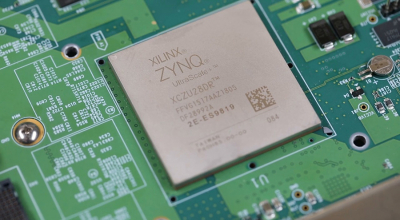

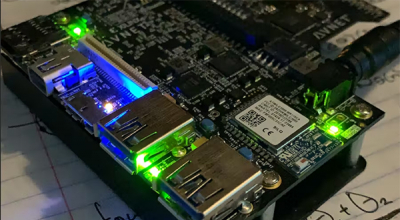

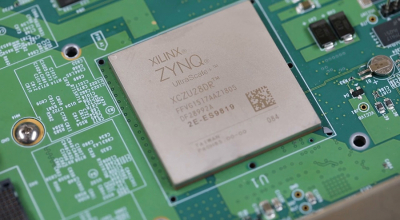

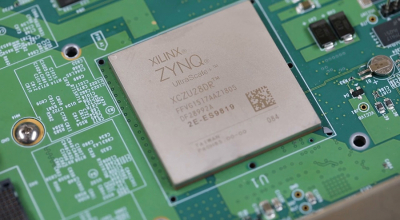

本文介绍如何使用Xilinx DDS Compiler IP并把它运行在 Ultra96 板上的可编程逻辑中

本文主要对正交调制器校正、粗延迟设置、动态更新配置、PLL以及中断处理操作进行介绍

本文我们继续介绍7系列FPGA收发器架构的RX部分内容

衍生时钟约束必须指定时钟源,在对衍生时钟进行约束时,并不指直接对其周期

本文主要对高采样率模式、多频带操作以及IP的数据接口进行介绍。

在设计过程中,各个阶段的生成的文件都是.dcp,Vivado使用的是通用的模型贯穿在设计。

主时钟约束,就是我们对主时钟(Primary Clock)的时钟周期进行约束