Petalinux实现qt程序输出

judy 在 周四, 08/04/2022 - 09:28 提交

本教程涉及到linux版本下安装vivado(vitis)、qt和petalinux的安装。

本教程涉及到linux版本下安装vivado(vitis)、qt和petalinux的安装。

传统的C语言数据类型 以8为边界,即数据宽度为8的整数倍,比如32bit,64bit等,相比之下RTL数据的位宽即比较灵活

数据同步一般是指数据从不同时钟域之间传递的过程,是FPGA设计中的基础。数据同步中最常见的问题就是数据在同步过程中被改变

在设计代码的时候,大部分人都是习惯于使用外部的编辑器进行设计,而不是使用vivado自带的编辑器

通常对FPGA下载程序时,会采用JTAG口下载,完成好HDL设计,并且验证无误后,对设计文件进行综合,布局布线以及生成比特流文件

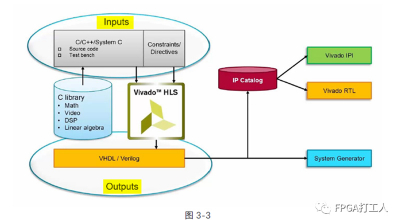

HLS现在应该算是比较成熟了,其最大的吸引力就是可以采用纯C/C++或者System C来对FPGA进行编程,相对于VHDL和Verilog更加容易上手

AXI 协议是一种高性能、高带宽、低延迟的片内总线,具有如下特点

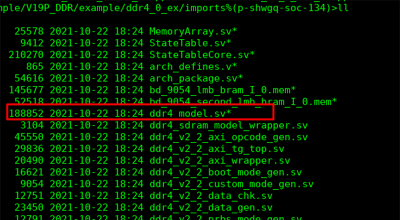

首先新建ddr的IP,具体每个参数的含义,可以参考之前写的《Virtex7 Microblaze下DDR3测试再右键》,打开IP的Example Design

本节介绍基于 MicroBlaze 的自定义 IP 核封装实验,实验任务是通过自定义一个呼吸灯 IP 核,来控制 LED 呈现呼吸灯的效果

这里重点介绍下FIFO和RAM不一样的地方,以及在工程使用中的一些问题。