数字信号处理(二):Xilinx FFT IP核详解(一)

judy 在 周一, 09/05/2022 - 11:15 提交

Xilinx LogiCORE IP快速傅立叶变换核实现了Cooley-Tukey-FFT算法,这是计算离散傅立叶变换(DFT)的有效方法

Xilinx LogiCORE IP快速傅立叶变换核实现了Cooley-Tukey-FFT算法,这是计算离散傅立叶变换(DFT)的有效方法

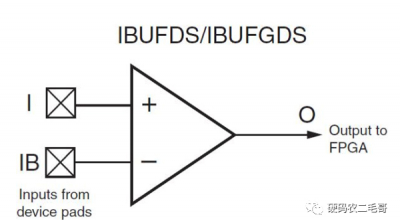

FPGA开发中经常会用到LVDS信号,本文分别介绍intel fpga和xilinx fpga的LVDS信号处理方法。

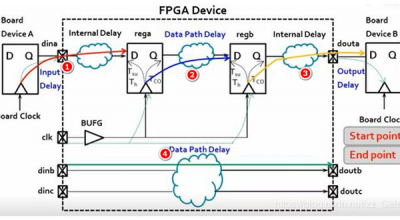

数字电路根据逻辑功能的不同特点,可以分成两大类:组合逻辑电路与时序逻辑电路

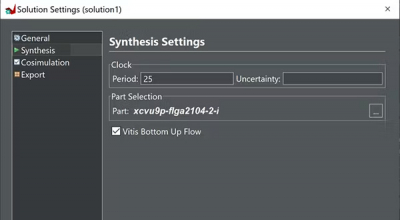

Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

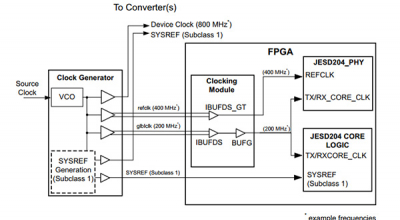

JESD204B 标准中定义的确定性延迟机制要求多帧大小大于链路上的最大可能延迟。

在HLS中使用ap_fixed数据类型,可以结合硬件特性,很好的控制位宽

如果遇到使用多个中断的情况该如何处理中断函数呢?下面以dma和axi gpio为例进行说明。

同步FIFO中的一些关键信号说明

最近看到很多人问FPGA如何入门,或者如何学习的问题,突然想起自己刚工作的时候,部门的培养还是做的很不错的

在Xilinx和Intel平台的FPGA中提供了给我们各种各样的IP核,这些IP核都是厂家的成熟设计,使用起来也非常的方便