首先要知道DDR3的一些时钟含义:

1.DDR3接口时钟:也就是DDR3接口传输速率

2.等效时钟:因为数据在接口双沿采样,因此等效时钟为接口时钟的两倍。

3.DDR3芯片内核工作时钟:DDR3存储芯片内部存储阵列的时钟。

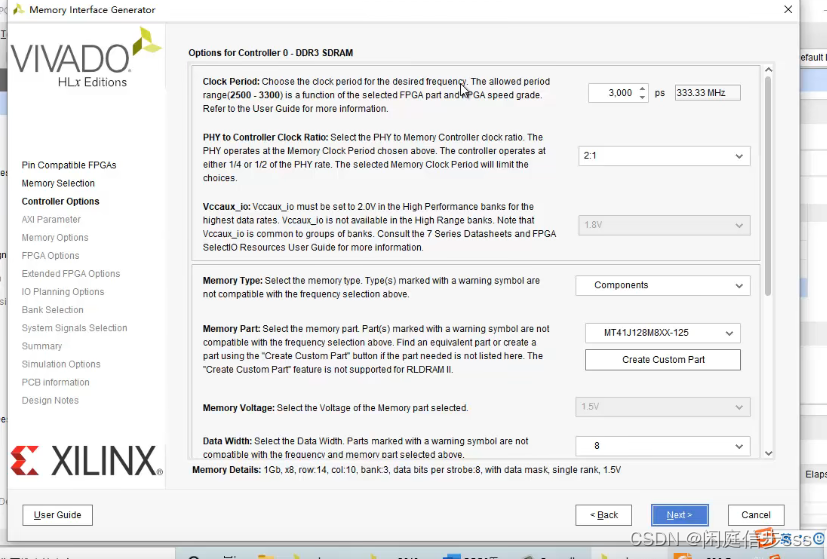

clock period这里就是DDR3接口时钟频率。

PHY to Controler CLock Ratio:2:1或者4:1;

4:1:接口时钟频率为400MHZ,那么读写的数据到用户逻辑测,工作时钟就是100MHZ.

ui数据接口位宽:同时这个比例会影响到ui接口的数据位宽;

2:1时,ui位宽是物理层位宽的4倍,4:1时,ui位宽是物理层位宽的8倍。

从时钟频率和数据匹配的角度也能得出这个计算关系是正确的。

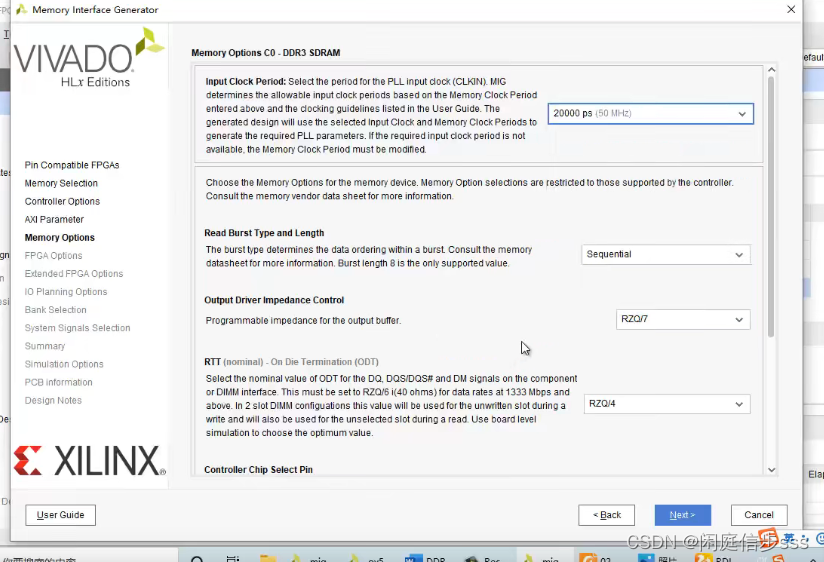

input clock period:输入时钟频率,这是输入给MIG 核的时钟,IP核内部会自己调用pll和MMCM 来产生自己的工作时钟

————————————————

版权声明:本文为CSDN博主「闲庭信步sss」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/spx1164376416/article/details/123460702