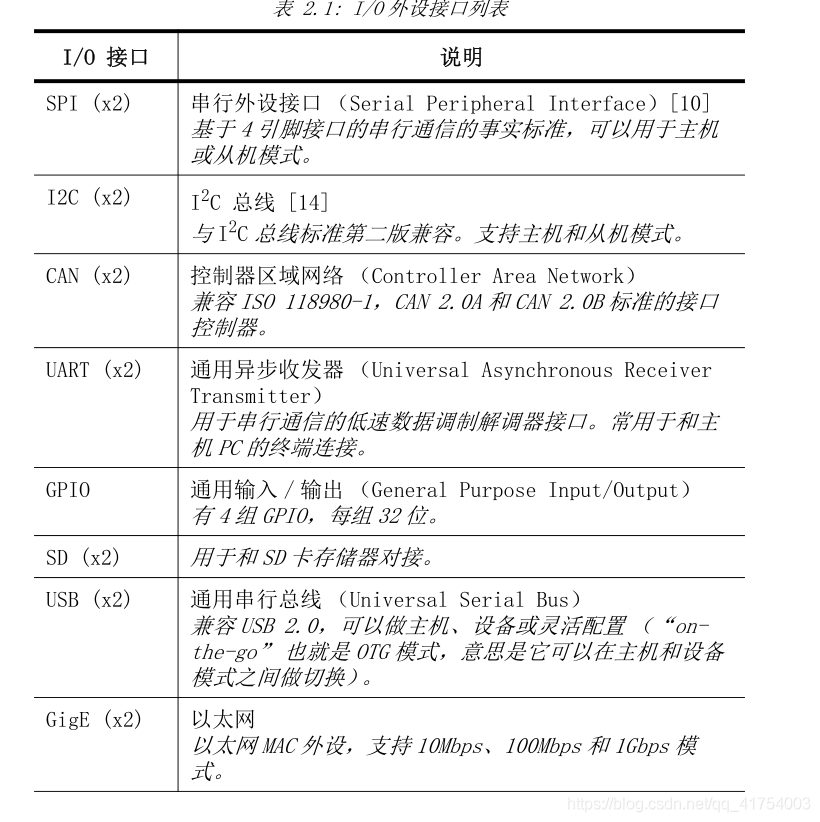

Zynq PS 实现了众多接口,既有 PS 和 PL 之间的,也有 PS 和外部部件之间的。。PS 和外部接口之间的通信主要是通过复用的输入 / 输出(Multiplexed Input/Output,MIO)实现的,它提供了可以做灵活配置的 54 个引脚,这表明外部设备和引脚之间的映射是可以按需定义的。这样的连接也可以通过扩展 MIO (Extended MIO,EMIO)来实现,EMIO 并不是 PS 和外部连接之间的直接通路,而是通过共用了PL 的 I/O 资源来实现的 [30]。这些都出现在图 2.2 的左侧。当需要扩展超过 54 个引脚的时候可以用 EMIO,而当 PL 中实现了一个 IP 包的时候,这也是 PS 和 PL 中的IP 包接口的一种方法。可用的 I/O 包括标准通信接口和通用输入 / 输出 (General Purpose Input/Output,GPIO),GPIO 可以用做各种用途,包括简单的按钮、开关和 LED。表 2.1总结了全部 I/O 外设接口,左侧列中标着的名字对应了 Xilinx 开发工具中用的缩写。注意每种通信接口都有两个。这里每个接口的丰富而深入的数据在 《Zynq-7000 Technical Reference Manual (Zynq-7000 技术参考手册)》 中。

通用输入 / 输出

Zynq 上的通用输入 / 输出功能(IOB)合起来被称作 SelectIO 资源,它们被组织成 50 个 IOB 一组。每个 IOB 有一个焊盘,是与外部世界连接来做单个信号的输入或输出的。I/O 组被分类为高性能 (High Performance,HP)或高范围 (High Range,HR),支持各种 I/O 标准和电压,具体见 [24]。HP 接口的电压最高为 1.8V,通常用作连接存储器和其他芯片的高速接口;而 HR 接口允许高达 3.3V 的电压,适合做各种 IO 标准的连接。两类接口都支持单端和差分信号,单端需要一个 IOB 连接,而差分则需要两个。每个 IOB 还包含一个 IOSERDES 资源,可以做并行和串行数据的可编程转换(串行化和反串行化),数据可以是 2 位到 8 位的。

通信接口

更准确地说,Zynq 芯片里含有嵌入在逻辑部分里的 GTX 收发器和高速通信接口块 。这些是专用的硅片块 (“ 硬 IP” 块),能支持一些标准接口,包括 PCI Express、串行 RapidIO、SCSI 和 SATA。要实现 PCI Express,除了 GTX 收发器本身之外,还需要另一个硬 IP 包(一个 PCI Express 块 [22],也存在于相应的 Zynq 芯片)和块 RAM。GTX 收发器是以 “ 四元组 ” 的形式实现的,就是说一组有四个独立的通道,每个通道包括一个那个通道专用的锁相环 (Phase Locked Loop,PLL)、一个发送器和一个接收器。根据具体的 Zynq 芯片和封装的不同,最高可以支持 12.5Gbps 的速率。这个接口可以用来实现与像是网络设备、硬盘和其他 FPGA 或 Zynq 芯片这样的独立的外部芯片的连接。要使用这些 GTX 块,需要通过一个 Wizard 工具的支持,它能自动创建所需的接口的核 。从用户的角度看,就是把一个块引入系统,选择所需的协议和硬件选项,然后设置参数就可以了。

其他可编程逻辑扩展接口

最后我们来总结一下剩下的 PL 的外部接口。模拟 - 数字转换 — PL 还具有其他的硬 IP 部件:XADC 块。这是一个专用的模拟 - 数字转换器(Analogue to Digital Converter,ADC)混合信号硬件,具有两个独立的 12 位 ADC,每个可以以 1Msps 对外部模拟输入信号采样。对 XADC 的控制是用位于 PS 内的 PS-XADC 接口控制块实现的,而且 PS-XADC 控制块本身可以由 APU上所执行的软件来编程。

时钟 — PL 接收来自 PS 的四个独立的时钟输入,另外还能产生和分发它自己的与 PS 无关的时钟信号 。这个独立的 PL 资源与 7 系列 FPGA 里的是等价的,

编程与调试 — 在 PL 部分实现了一组 JTAG 端口来实现对 PL 的配置和调试。尽管在部署的时候通常倾向于更安全的方法,在开发阶段还是常用 JTAG来做配置。ARM 和 Xlinx 工具都支持通过 JTAG 来做调试。

——以上文章摘自《The Zynq Book》

————————————————

版权声明:本文为CSDN博主「MTIS」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/qq_41754003/article/details/112904205