课时3:Vitis HLS设计流程(实例演示)——Vitis HLS教程

judy 在 周五, 05/13/2022 - 15:30 提交

本文我们通过一个具体的实例,演示HLS设计流程。

本文我们通过一个具体的实例,演示HLS设计流程。

传统的FPGA RTL设计流程主要是采用VHDL、VerilogHDL或System Verilog进行工程的开发,同时也是通过硬件描述语言来编写测试案例对开发的工程进行仿真验证

FIFO是FPGA设计中最常用的IP,读写时序相对简单,可能正是因为这个原因,通常不会去细读FIFO手册,具体怎么操作大概清楚,上手就写,一般不会出什么问题。最近却遇到读FIFO异常的情况,特意记录一下

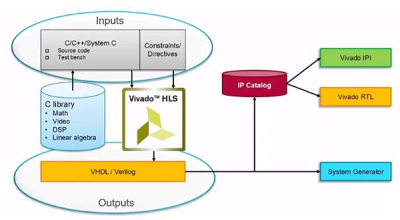

Vitis HLS是一个高级综合工具。用户可以通过该工具直接将C、 C++编写的函数翻译成HDL硬件描述语言,最终再映射成FPGA内部的LUT、DSP资源以及RAM资源等。

本文使用zynq7045实现SRIO枚举功能,PL端有SRIO IP,只需要将AXI维护端口挂到AXI-GP接口上,PS软件就可以通过AXI总线访问SRIO IP实现枚举自动分配ID功能。

在进行MIPI摄像头开发时,经常用到Xilinx的MIPI CSI-2 Receiver Subsystem IP,下面对该IP使用方法进行简单介绍。

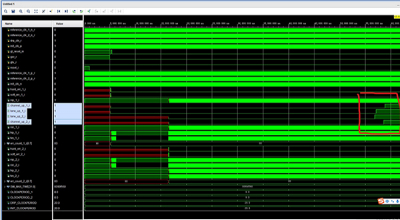

report_clock_interaction矩形框内的不同颜色表征了不同时钟域之间的路径所呈现的约束状态而非Slack(时序裕量)的恶化程度

本文主要讲述了如何避免FSM输出毛刺。

Xilinx的技术生态做的非常好,基本上所有常用的IP核都有官方例程供开发者学习,咱不用白不用,今儿咱就一起白嫖他一手----从官方例程开始学习如何具体使用这个IP核。

阅读本文将有助于你的FPGA选型和设计过程,并且有助于你规避许多难题。