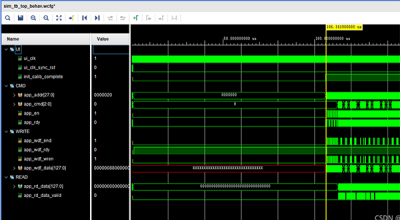

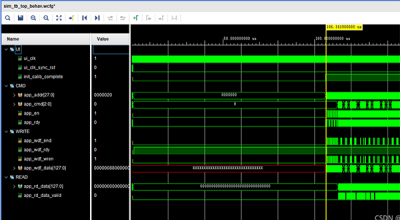

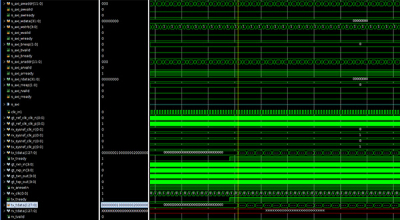

快速上手Xilinx DDR3 IP核(2)——MIG IP核的官方例程与读写测试模块(Native接口)

judy 在 周五, 02/25/2022 - 09:20 提交

在我心中,Xilinx是一家完美的公司,技术生态支持实在是做的太好了。Xilinx也知道我们不会用DDR3,所以提供了一个example design给你学习,怎么样?惊不惊喜?意不意外?

在我心中,Xilinx是一家完美的公司,技术生态支持实在是做的太好了。Xilinx也知道我们不会用DDR3,所以提供了一个example design给你学习,怎么样?惊不惊喜?意不意外?

对于xilinx移位寄存器IP的使用而言,其内部为SLR16/SRL32实现。当位深小于32时,其可变延迟是正确的。当大于32,其可变延迟为相同延迟加1。

系统主要采用官方JESD_PHY(免费),JESD_RX(评估版),JESD_TX(评估版)三个IP核做测试,采用自发自收,外部GT引脚回环方式。其中,PHY采用4个LANE接收和发送数据,一般线速率为参考时钟的40倍

DDR3 SDRAM 简称 DDR3,是当今较为常见的一种储存器,在计算机及嵌入式产品中得到广泛应用, 特别是应用在涉及到大量数据交互的场合

时钟信号在很大程度上决定了整个设计的性能和可靠性,尽量避免使用FPGA内部逻辑产生的时钟,因为它很容易导致功能或时序出现问题

BEL是最底层的基本元素,也可以叫atomic unit(原子单位),BEL是FPGA中最小、不可分割的组件。BEL有两种:Logic BEL和Routing BEL。

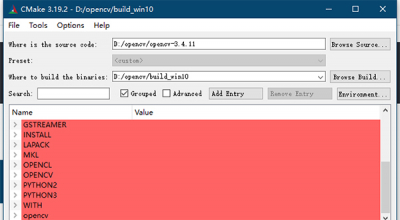

Vitis HLS OpenCV库编译

如图所示, 源文件目录中haha文件夹下有一个hoho.h头文件。本来要包含这个头文件应该写成#include "haha/hoho.h"的,但是如果写成#include

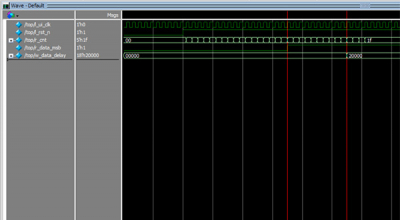

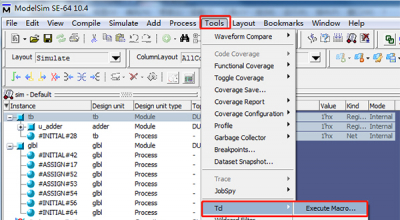

老鸟的姿势学起来,用脚本进行modelsim仿真

先从运行一个创建一个项目开始吧。