在I/O和时钟规划之后,需要验证设计以确保其满足设计需求。Vivado提供了两种验证途径:DRCs用来检查设计违反规则情况;SSN分析用来估计转换噪声等级。本文将介绍DRCs,本系列第16篇介绍了SSN分析。

运行DRCs

DRCs可以说是管脚规划中最严苛的一个步骤,DRCs会使用一套设计检查项(通常称作rule deck),来检查当前设计是否违反这套规则。本文将以运行DRCs检查I/O端口和时钟逻辑为例。

打开某一阶段的设计,点击Tools->Report->Report DRC,或在Flow Navigator中直接点击Report DRC,弹出如下窗口:

Results name规定了显示DRC结果的窗口名称;Output file可以选中一个保存DRC结果的文件。Rule Decks中选择用于DRCs的rule deck,一个rule deck便是一套设计规则。可以同时选择多个rule deck,同一个规则也可以包含在多个rule deck中。

根据运行DRCs所处设计阶段的不同(RTL设计、综合后设计、实现后设计),可以选择的Vivado提供的rule deck如下:

选择了rule deck之后,可以根据需要修改在Rules中使用的设计规则。运行DRCs的Tcl示例如下:

report_drc -ruledecks default -file C:/Data/DRC_rpt1.txt

如果不想使用Vivado提供的rule deck,可以创建一个用户自定义的rule deck并添加到Rule Decks窗口中。该操作需要使用Tcl代码来完成,示例如下:

create_drc_ruledeck ruledeck_1

add_drc_checks -ruledeck ruledeck_1 [get_drc_checks {SYNTH-10 SYNTH-9 SYNTH-8 SYNTH-7 SYNTH-6 SYNTH-5 SYNTH-4}]

交互式DRCs

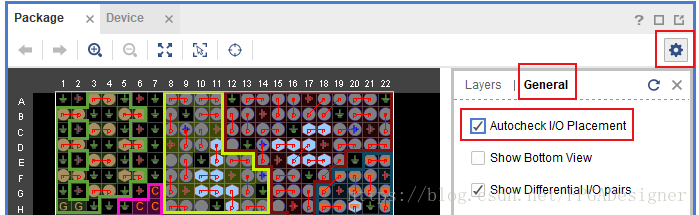

在I/O布局过程中,Vivado IDE会运行一个基本的检查以确保合理的引脚分配,但是只有在实现后设计中的检查才能确保最终引脚分配完全合法。管脚布局时,交互式的I/O布局例行检查会报告常见的错误,这项功能可以在Package窗口或Device窗口的设置中通过Auto check I/O Placement复选框选择是否开启:

交互式DRCs的检查规则如下:

Vivado默认开启交互式DRCs功能(交互式指的是用户每执行操作后都运行相关检查),Xilinx也推荐始终开启这个功能。

查看DRC违规信息

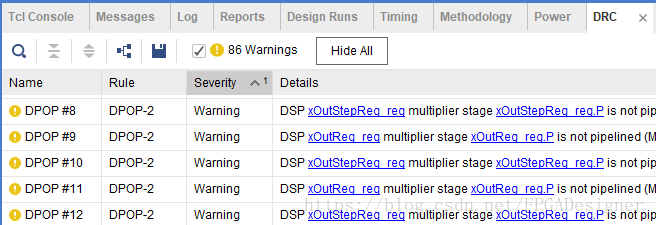

如果找到了违规信息,会打开DRC窗口,如下所示:

违规信息根据严重性分为4个等级,图标显示为不同的颜色:

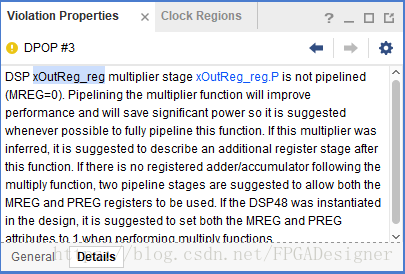

违规信息所包含的内容一般比较长,可以单击选中,在Violation Properties窗口中更方便地查看信息(如果属性窗口没有打开,选中信息右键菜单中打开):

Details信息中给出了具体描述和解决方案,供设计者参考是否要修改设计。有的信息会包含一些蓝色链接,单击可以在其它窗口中交叉探测到产生违规的对象。

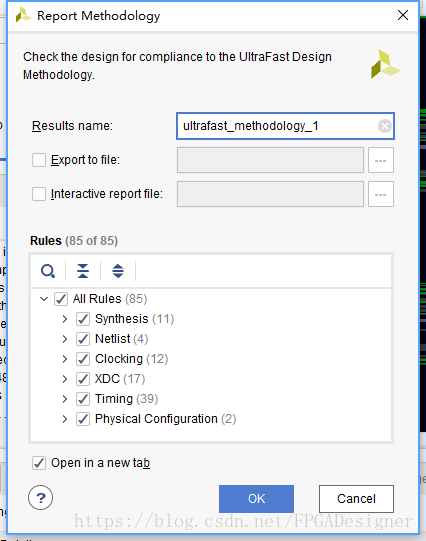

报告Methodology

在Vivado 2016.1之后的版本中,将部分DRC检查组合为一个新功能Report Methodology中,该功能运行一些简化的规则检查来验证设计(比如逻辑映射),遵从UltraFast设计方法。打开某一阶段设计后,在Flow Navigator中点击此功能:

如果有设计违规会显示在Methodology窗口,信息查看方式与DRC相同。最好的做法是在Elaborated Design阶段就运行该功能,可以帮助设计者在早期发现设计问题,节约开发成本。

文章来源:FPGADesigner的博客

*本文由作者授权转发,如需转载请联系作者本人