注意:本文所有内容皆来源于Xilinx工程师,如需转载,请写明出处作者及赛灵思论坛链接并发邮件èï¼æªç»Xilinxåèä½æ人许å¯ï¼ç¦æ¢ç¨ä½åä¸ç¨éã

ç®ä»ä¸è§é¢ç¤ºä¾è®¾è®¡æ¦è§

许å¤è§é¢ IP æ ¸é½é带æ示ä¾è®¾è®¡ãè¿äºè®¾è®¡ç¨äº IP æ¼ç¤ºï¼å¹¶æä¾ç¤ºä¾ä»¥ä¾æ¨å¨èªå·±ç设计ä¸ä½¿ç¨ IP æ ¸æ¶ä½ä¸ºåèã

è¿äº IP 示ä¾è®¾è®¡çä»ç»è¯·åé IPã产åæåã第 5 ç« ã

å¨IP主页ä¸ï¼Document Navigator æè§é¢è®¾è®¡ä¸å¿å å¯æ¾å°ã产åæåãã

HDMI VCU118 示ä¾è®¾è®¡ç®ä»

èµçµæ HDMI IP æ ¸å为两ç§ï¼æºç«¯ (Source) IP æ ¸ (HDMI 1.4/2.0 TX Subsystem) å Sink IP æ ¸ (HDMI 1.4/2.0 RX Subsystem)ã

è¿äº IP æ ¸çä»ç»è¯·åé (PG235) å (PG236)ãã产åæåã第 5 ç« ä¸å å«HDMI 1.4/2.0 示ä¾è®¾è®¡çè¡¨æ ¼ã

éè¿è¯¥è¡¨å¯ä»¥çå°ï¼å ¶ä¸å å« VCU118 示ä¾è®¾è®¡ï¼ä½ä¸å« VCU128 示ä¾è®¾è®¡ã

注æï¼å¦è¯¥è¡¨æ示ï¼ä¼ é模å¼ä¸æ DRU æ¶éå¯ç¨ï¼å 为并æ ä»»ä½æ¯è¡å¨å¼èä¿¡å·è¾åºè³ HDMI æ ¸éè¿ bank ä¸ç gtrefclkã

æç¨

以ä¸æ¯æå° HDMI VCU118 设计移æ¤å° VCU128 å¼åæ¿æ¶æ使ç¨çæ¥éª¤ãè¿äºæ¥éª¤ä» ä½ä¸ºç¤ºä¾ä»¥ä¾åèï¼å¹¶éå¯ä¸æ¹æ³ã

1. 移æ¤è®¾è®¡ç第ä¸æ¥æ¯ç¡®ä¿å·²æ建æ°ç¡¬ä»¶å¹³å°ç¨äºä¸ºè®¾è®¡æä¾æ¯æã

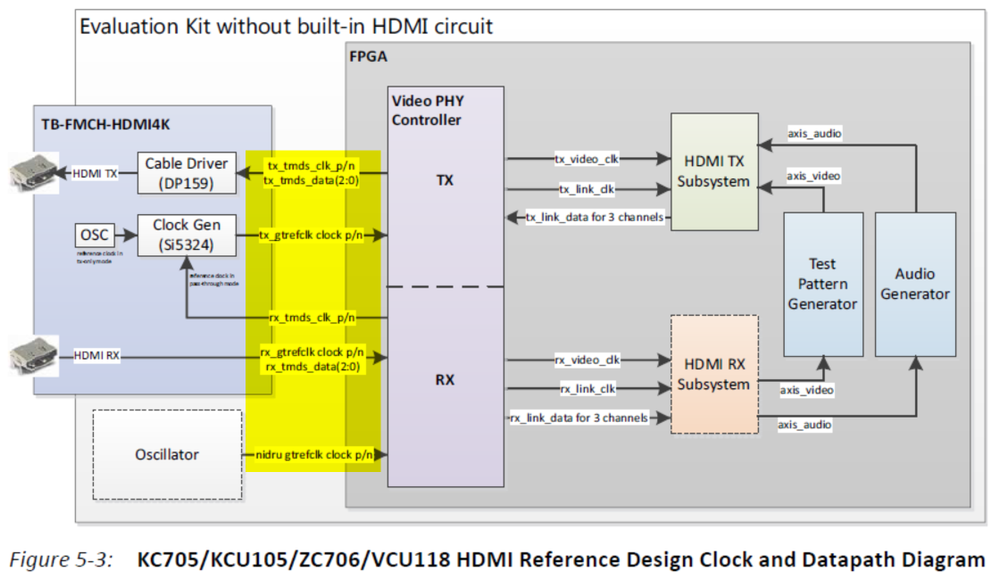

æ好é¦å ç½ååº HDMI 设计è¦æ±ãéè¿ä½¿ç¨ã产åæåãä¸çå¾ 5-3 并èç¦é«äº®ç I/Oï¼è®¾è®¡è¦æ±ä¸ç®äºç¶ã

注æï¼VCU118 ä¸ VCU128 å¼åæ¿é½ä¸å ·æ nidru gtrefclkã

设计è¦æ±å表ï¼

TMDS æ¶éå¼èä¿¡å·å·²è¾åºè³ FMC

å·²éè¿ 3 个 GT å¼èå°åå°å¨æ°æ®å¼èä¿¡å·è¾åºè³ FMC

åå°å¨åèæ¶éå¼èä¿¡å·å·²ä» FMC è¾å

¥

æ¥æ¶å¨åèæ¶éå¼èä¿¡å·å·²è¾åºè³ FMC

æ¥æ¶å¨åèæ¶éå¼èä¿¡å·å·²ä» FMC è¾å

¥

å·²éè¿ 3 个 GT å¼èå°æ¥æ¶å¨æ°æ®å¼èä¿¡å·è¾åºè³ FMC

**è¯·æ ¸å®å¨å´å bank 以确认æ¯å¦åå¨å¯ç¼ç¨ NI-DRU æ¶éæº

2. å·²ç¥è®¾è®¡è¦æ±æ åµä¸å³å¯æ£æ¥ VCU128 以确认æ¯å¦å·²æ»¡è¶³è¿äºè¦æ±ã

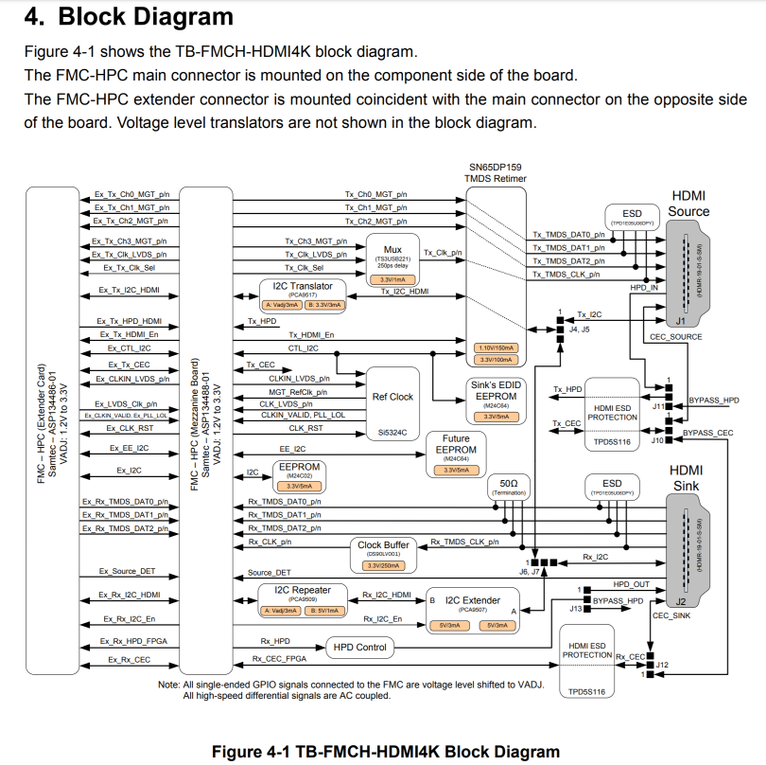

为æ¤ï¼æ们å¯ä»¥æ¥é VCU128 åçå¾ãVCU128 å¼åæ¿ç¨æ·æå以åwikipinout.xml 并对æ¯FMC ææ¡£ï¼å¦ä¸å¾æ示ï¼

éè¿ä½¿ç¨ä¸è¿°ææ¡£å³å¯å°å表转æ¢ä¸ºå¼èå称ã

M2C -> 夹å±å¡å°è½½å¡ï¼FMC -> å¼åæ¿ï¼

C2M -> è½½å¡å°å¤¹å±å¡ï¼å¼åæ¿ -> FMCï¼

TMDS æ¶éå¼èä¿¡å·å·²è¾åºè³ FMC -> LA27_P

å·²éè¿ 3 个 GT å¼èå°åå°å¨æ°æ®å¼èä¿¡å·è¾åºè³ FMC -> DP0_C2M_P è³ DP2_C2M_P

åå°å¨åèæ¶éå¼èä¿¡å·å·²ä» FMC è¾å

¥ -> GBTCLK1_M2C_P

æ¥æ¶å¨åèæ¶éå¼èä¿¡å·å·²è¾åºè³ FMC -> LA00_CC_P

æ¥æ¶å¨åèæ¶éå¼èä¿¡å·å·²ä» FMC è¾å

¥ -> GBTCLK0_M2C_P

å·²éè¿ 3 个 GT å¼èå°æ¥æ¶å¨æ°æ®å¼èä¿¡å·è¾åºè³ FMC -> DP0_M2C_P è³ DP2_M2C_P

**è¯·æ ¸å®å¨å´å bank 以确认æ¯å¦åå¨å¯ç¼ç¨ NI-DRU æ¶éæº

bank124 å¨å´æ å¯ç¨æ¶é

éè¿æ¥ç设计å¯ä»¥åç°ï¼å¨å¾ 5-3 ä¸å¹¶æªæ¾ç¤ºå ¨é¨å¼èã

Si5324 RST

FMC_IIC_SCL

FMC_IIC_SDA

rs232_uart_rxd ->UART0_RXD

rs232_uart_txd ->UART0_TXD

reset -> CPU_Reset

RX_DDC_OUT_scl_io ->LA16_P

RX_DDC_OUT_sda_io ->LA16_N

TX_DDC_OUT_scl_io->29_P

TX_DDC_OUT_sda_io->29_N

TX_EN_OUT ->LA26_P

TX_CLK_SEL_FPGA -> LA18_CC_P

ç¨äºéæ©æ¯å¦ä½¿ç¨ç¬¬ 4 个 GT æ LVDS å¼èä½ä¸º HDMI TMDS æ¶éã

RX_HPD_OUT -> LA20_N

RX_I2C_EN_N_OUT -> LA22_P

RX_DET_IN -> LA03_P

SI5324_LOL_IN ->LA02_N

TX_HPD_IN -> LA31_N

3. é´äºå·²ç¥ I/O å¼èåå¨å¹¶ä¸å·²æ£å¸¸è¿æ¥å° FMCï¼ä¸ä¸æ¥å³å¯æ建 VCU118 示ä¾è®¾è®¡ã

注æï¼è¯¥è¿ç¨çä»ç»è¯·åé ã产åæåã第 5 ç« ã

4. å®æ设计æ建åï¼éè¦æ´æ°ææ VCU118 ç¹å®åæ°ãè¿æ ·å¨æ´æ¹é¨ä»¶å·æ¶ï¼è¿æ¥å°ä¿ææå¼ç¶æã

å¨æ¤è®¾è®¡ä¸ï¼MMCM æ¯ç´æ¥ä»¥ VCU118 为ç®æ çå¯ä¸ IPã

4.1. æå¼ mb_ss_0 å并æå¼æ¶éå导 (clk_wiz)ã

4.2. åå»âClear board parametersâä»¥æ¸ ç©ºå¼åæ¿åæ°ãè¿å°å é¤ VCU ç¹å®åæ°ã

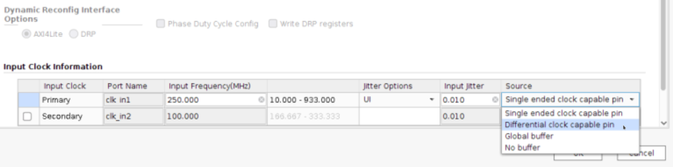

4.3. å°âSourceâæ´æ°ä¸ºâDifferential clock capable pinâï¼ç¶åä¿åå设计

5. 设置æ°é¡¹ç®ç®æ -> VCU128 (XCVU37P-L2FSVH2892E)

6. å° IP æ´æ°å°æ°é¡¹ç®

æå¼ IP éæå¨ãéæ©æ¥å IP ç¶æï¼ç¶åå级ææ IPã

éªè¯å ¶ä¸ä¸åå¨ä»»ä½é误ã

注æï¼ä¸ä¿è¯è¿å¯¹ææ设计æ移æ¤é½ææãå¦ææ¤æ¥éª¤æ æï¼è¯·ä½¿ç¨å åç设计ä½ä¸ºç¤ºä¾å¹¶æå¨æ建æ°é¡¹ç®.

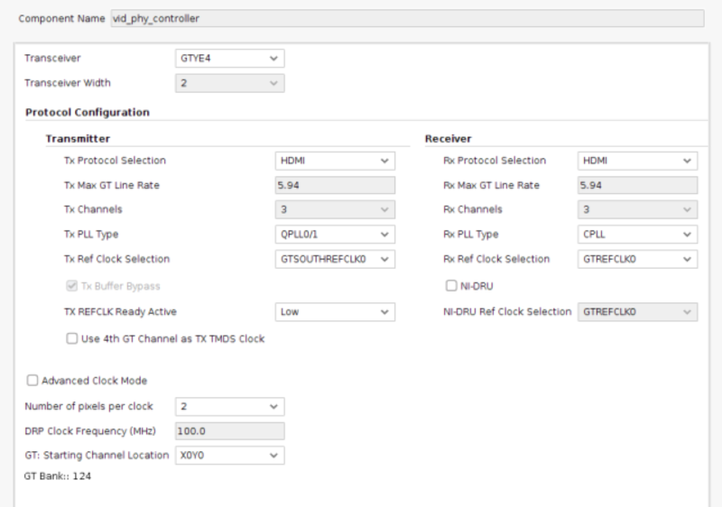

7. é´äºå½å项ç®ç®æ 为 VCU128 å¹¶ä¸ IP å·²å级ï¼æ们éè¦ç¼è¾ VPHYï¼è®¾ç½®æ£ç¡®ç bank ç®æ 并使ç¨æ£ç¡®çæ¶éã

éè¿ VCU128 ææ¡£å¯ç¥ï¼æ使ç¨ç GT ä½äº bank 124 ä¸ãBank 124 为 X0Y0ã

ç±äº GT ä½äº bank 124 ä¸ï¼ä½å½å使ç¨ç TX reference0 æ¶éæ¥èª bank 125ï¼å æ¤éè¦å°åèæ¶é设置为 southrefclk0ã

ç±äºå½å使ç¨çæ¯ North/South refclkï¼å æ¤éæ ¹æ® (PG230) ãVivado PHY æ§å¶å¨äº§åæåãä¸æè¿°æ´æ°ç®¡èã

8. è¯·æ ¸å®è¿æ¥ç¶æï¼ç¡®ä¿ææå¼èåå·²è¿æ¥ï¼ç¶åéªè¯è®¾è®¡å¹¶è¿è¡ç»¼åã

9. å®æ综ååï¼å³å¯æ´æ°çº¦æã

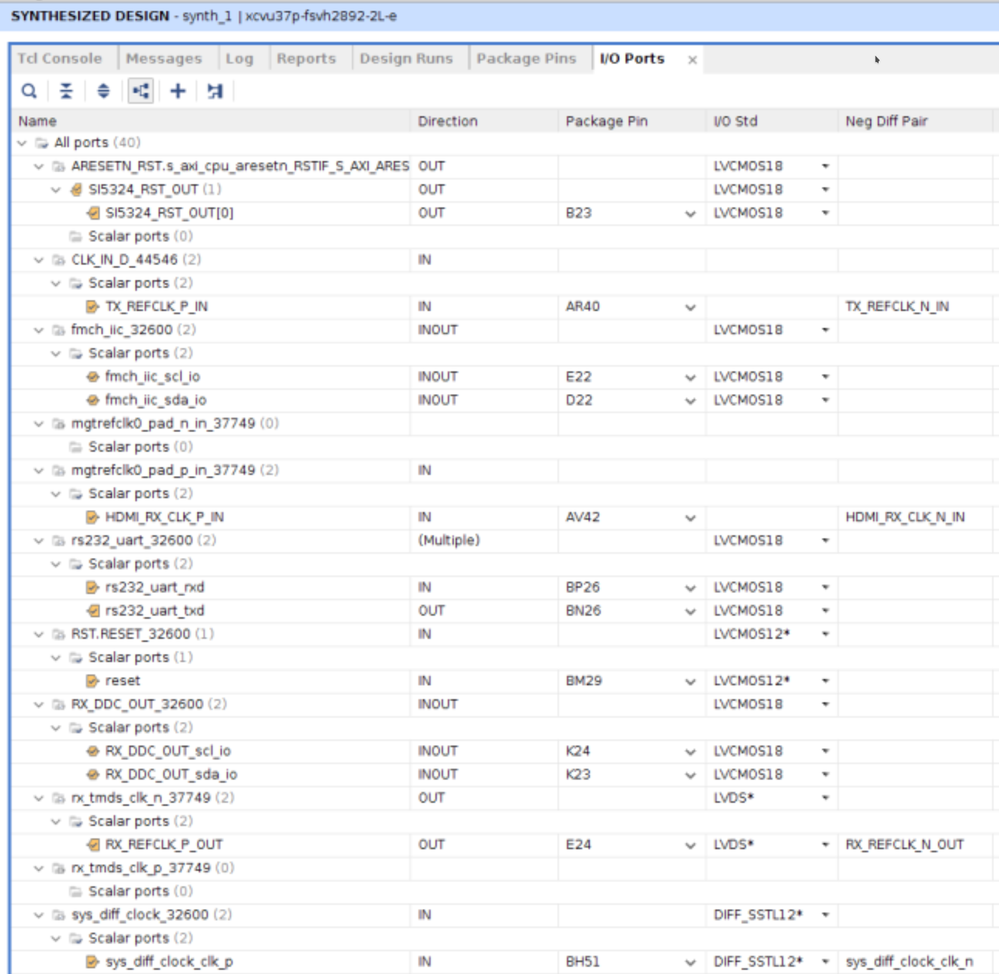

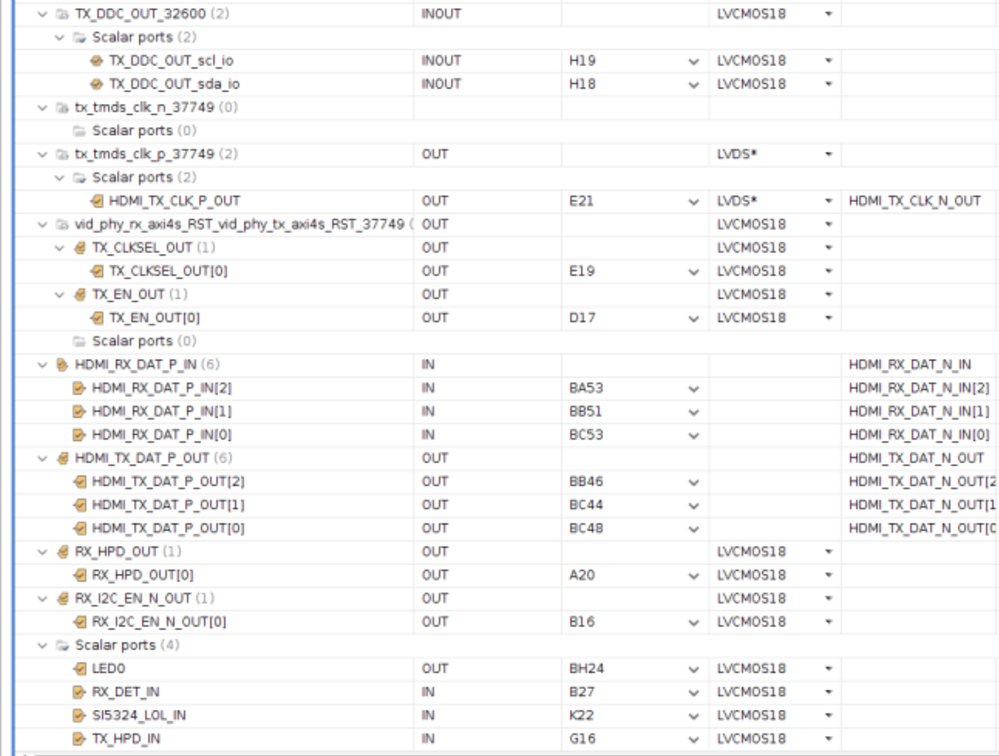

æå¼ Synthesized Designï¼ä¾æ¬¡åå»âlayout -> I/O planningâã

å¨æ¤è§å¾ä¸ï¼éæ© I/O 端å£ï¼ç¶å使ç¨æ°ç®¡èå¯¹å ¶è¿è¡æ´æ°ãï¼GT TX/RX å¼èå°å·²å¡«å å®æï¼

å®ææä½åï¼è¯·ä¿å以便æ´æ°çº¦ææ件 (.xdc)ã

10. 约ææ´æ°å®æåï¼è¯·è¿è¡å®ç°å¹¶çææ¯ç¹æµã

11. 导åºç¡¬ä»¶ç¨äº SDKã

åå»âFile -> Export Hardware

12. æåï¼é对 VCU118 使ç¨ç¸åæµç¨æ¥æ建åºç¨ç¤ºä¾è®¾è®¡ã

æå¼ SDK

æ°å»º BSP (File -> New SDK)

åå» MSS æ ç¾ï¼éä¸ HDMI 1.4/2.0 RX Subsystem 驱å¨ç¨åºï¼ç¶ååå»âImport Examplesâã

å¨æå¼çæ ç¾ä¸ï¼åå»âPassthrough MicroBlazeâã

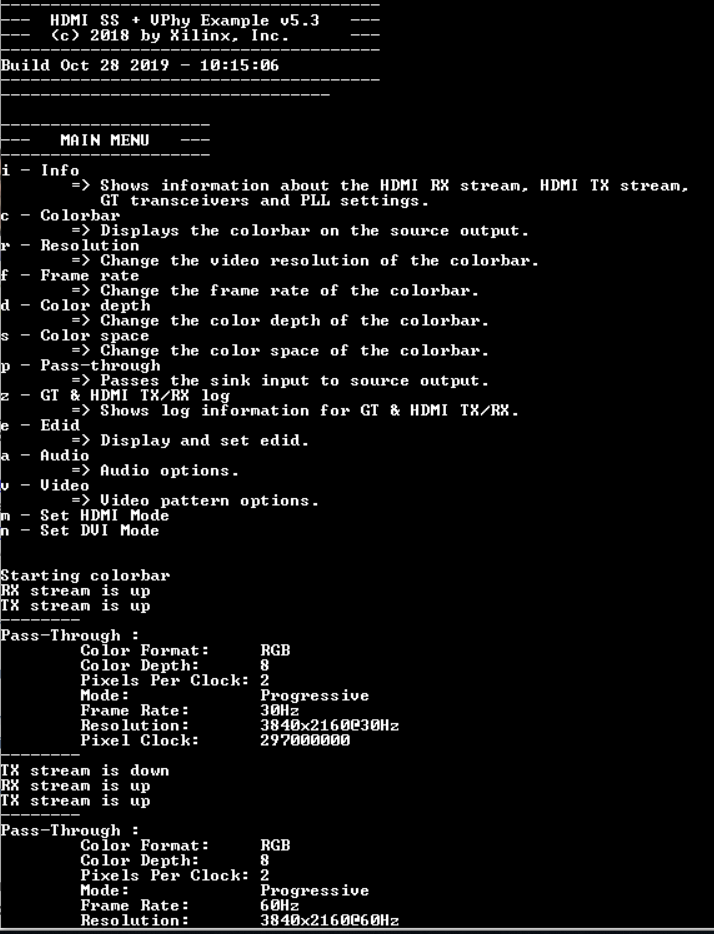

è¿å°çæ软件项ç®ãå¯¹å ¶æ§è¡æ建ï¼è¿æ ·å³å¯å建 ELFã

13. 大ååæï¼å¨ç¡¬ä»¶ä¸æ§è¡æµè¯ä»¥éªè¯ç§»æ¤ç示ä¾è®¾è®¡æ¯å¦æ£å¸¸è¿è¡

æç« æ¥æºï¼Â èµçµæä¸æ社åºè®ºå