作者:Florent Werbrouck,Xilinx工程师

注意:本文来源于赛灵思中文社区论坛,如需转载,请写明出处作者及赛灵思论坛链接并发邮件èï¼æªç»Xilinxåèä½æ人许å¯ï¼ç¦æ¢ç¨ä½åä¸ç¨é

å¼è¨

è¿æ¥ï¼å ä¹æ¯ä¸ªèµçµæ IP é½ä½¿ç¨ AXI æ¥å£ãZynq®ãZynq MPãMicroBlaze⢠åå ¨æ°ç Versal⢠å¤çå¨é½æ ä¸ä¾å¤ä½¿ç¨ AXI æ¥å£ãå æ¤ï¼AXI æ¥å£å·²æ为å ä¹æææ°çèµçµæå¨ä»¶è®¾è®¡ä¸ä¸å¯æ缺çä¸é¨åãå åäºè§£å ¶åºç¡ç¥è¯å¯¹äºèµçµæå¨ä»¶ç设计åè°è¯é½å¾æ帮å©ã

æ¬ç¯åæå°ä»ç»èµçµæå¨ä»¶ä¸ç AXI3/AXI4 çç¸å ³åºç¡ç¥è¯ãé¦å ï¼æ们å°ä»ä¸äºéä¿ææçç¥è¯ãç论åæ¯è¯å¼å§è®²è§£ã

ä½è° AXIï¼

AXI 表示 Advanced eXtensible Interfaceï¼é«çº§å¯æ©å±æ¥å£ï¼ï¼å®æ¯ç±Â Arm å®ä¹çæ¥å£åè®®ï¼å å«å¨“é«çº§å¾®æ§å¶å¨æ»çº¿æ¶æ AMBA”æ åä¸ã

AXI3/AXI4 è§æ ¼å¯éè¿Â Arm ç½ç«å è´¹è·åï¼é¾æ¥ï¼ï¼å æ¤å¦ææ¨å¯¹å ¶æå ´è¶£ï¼æé¼å±æ¨å¡å¿ ä¸è½½ã

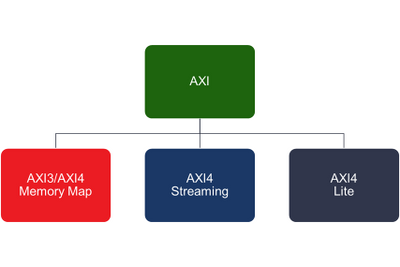

AXI4 æ¥å£ (AMBA 4.0) å 3 ç§ç±»åï¼

注ï¼æ¬æä¸æ¶µç AXI4-Stream ç¸å

³å

容ãæ¤å¤âAXIâ表示 AXI3ãAXI4 å AXI4-Liteã

注ï¼AXI3 æ¥å£ä¸ Full AXI æ¥å£æ¥è¿ã

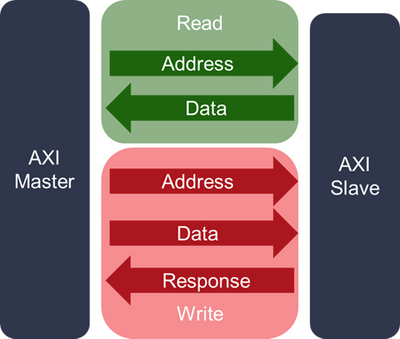

AXI 读åéé

AXI åè®®å®ä¹äº 5 æ¡ééï¼

å ¶ä¸ 2 æ¡ç¨äºè¯»åä¼ è¾äºå¡

å¦ 3 æ¡ç¨äºåå ¥ä¼ è¾äºå¡

éé (channel) æ¯ä¸ VALID å READY ä¿¡å·å ³èç AXI ä¿¡å·çç¬ç«éåã

注ï¼AXI4/AXI3/AXI4-Lite æ¥å£åªè½ç¨äºè¯»åï¼ä» å å« 2 æ¡è¯»åééï¼æè åªè½ç¨äºåå ¥ï¼ä» å å« 3 æ¡åå ¥ééï¼ã

ä»»ä¸ééä¸åå°çæ¯ä¸æ¡æ°æ®é½ç§°ä¸ºä¸æ¬¡ä¼ è¾ (transfer)ãå½ VALID å READY ä¿¡å·åå±

é«ä¸ä¸å¹¶ä¸æ¶éåå¨ä¸å沿æ¶ï¼å°±ä¼åçä¼ è¾ãä¾å¦ï¼å¨ä¸å¾ä¸ï¼å¨ T3 å¤æ£å¨åçä¼ è¾ï¼

AXI 读åä¼ è¾äºå¡

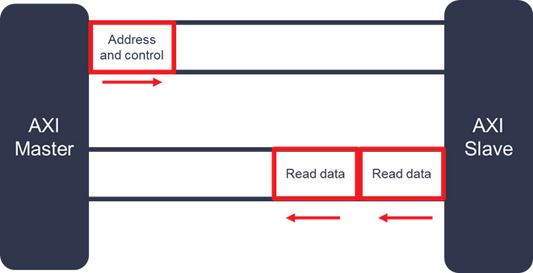

AXI è¯»ä¼ è¾äºå¡éè¦å¨ 2 æ¡è¯»åä¿¡éä¸åçå¤æ¬¡ä¼ è¾ã

é¦å

ï¼å°å读éé (Address Read Channel) ä»ä¸»è®¾å¤ (Master) åéå°ä»è®¾å¤ (Slave)ï¼ä»¥ä¾¿è®¾ç½®å°ååé¨åæ§å¶ä¿¡å·ã

ç¶åï¼æ¤å°åçæ°æ®éè¿è¯»æ°æ®éé (Read data channel) ä»ä»è®¾å¤åéå°ä¸»è®¾å¤ã

请注æï¼æ ¹æ®ä¸å¾æ示ï¼æ¯ä¸ªå°åä¸å¯åçå¤æ¬¡æ°æ®ä¼ è¾ãæ¤ç±»åçä¼ è¾äºå¡ç§°ä¸ºçªå (burst)ã

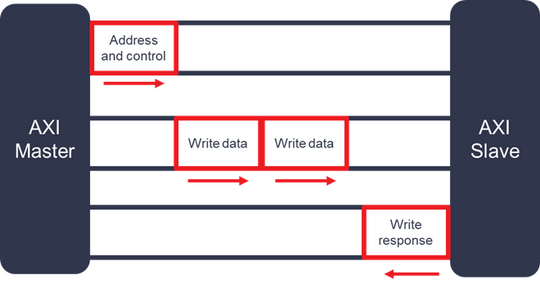

AXI åå ¥ä¼ è¾äºå¡

AXI åå ¥ä¼ è¾äºå¡éè¦å¨ 3 æ¡è¯»åä¿¡éä¸åå¨å¤æ¬¡ä¼ è¾ã

åååºéé (Write Response Channel) ä¸å¯è½çååºå¼å æ¬ï¼

注ï¼è¯»åä¼ è¾äºå¡åæ ·å å«ååºå¼ï¼ä½æ¤ååºéè¿è¯»ååºéé (Read Response Channel) æ¥åå°

AXI4 æ¥å£è¦æ±

å¨ AXI4 è§æ ¼ä¸è®°å½äºé¨åè¦æ±ã

æå¼å¾æ³¨æçæ¯ï¼

ä½æ¯ï¼READY ä¿¡å·çç¶æå¯ä»å±äº VALID ä¿¡å·

å¨ä¸ä¸ç¯ AXI åºç¡ç³»åæç« ä¸ï¼æ们å°ä½¿ç¨ AXI Verification IP (AXI VIP) 对 AXI4 æ¥å£è¿è¡ä»¿çã