作者:Wen Chen,文章来源: 赛灵思中文社区论坛

注意:本论坛博客所有内容皆来源于Xilinx工程师,如需转载,请写明出处作者及赛灵思论坛链接并发邮件èï¼æªç»Xilinxåèä½æ人许å¯ï¼ç¦æ¢ç¨ä½åä¸ç¨é

说起é«å±æ¬¡ç»¼åææ¯ï¼High-level synthesisï¼çæ¦å¿µï¼ç°å¨æå¾å¤åå¦è ç®åå°æå®ç解为å¯ä»¥èªå¨æc/c++ä¹ç±»å°é«çº§è¯è¨ç´æ¥è½¬æ¢æåºå±ç¡¬ä»¶æè¿°è¯è¨ï¼RTLï¼çææ¯ãå ¶å®æ´åç¡®ç表述æ¯ï¼ç±æ´é«æ½è±¡åº¦çè¡ä¸ºæè¿°ç产çµè·¯çææ¯ãé«å±æ¬¡çæ¦å¿µä»£è¡¨çæ¯ç¡¬ä»¶æè¿°è¯è¨éé¢è¾é«çæ½è±¡å±æ¬¡ï¼åªæ¯éç软件硬件è¯è¨çå ±ååå±ï¼è¿æ ·çé«æ½è±¡åº¦çè¡ä¸ºæè¿°è¯è¨æ¥å°äºC/C++/System C è¿æ ·çå±æ¬¡ã

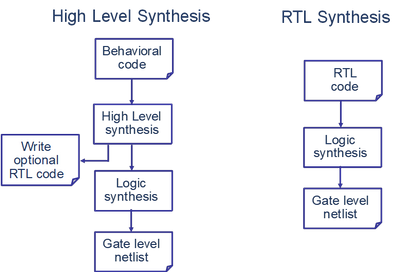

以ä¸æ¯åå å·å¤§å¦çDANIEL D.GAJSKIææå¨1994å¹´åºççæåæ¶å¯¹é«å±æ¬¡ç»¼åææ¯çæè¿°[1]ï¼High-level synthesis systems start with an abstract behavioral specification of a digital system and find a register-transfer level structure that realizes the given behavior. ä¸å¾æ示äºé«å±æ¬¡ç»¼åå·¥ä½çåºæ¬æµç¨ï¼ä»¥åå®äºä¼ ç»çRTL综åæµç¨ç对æ¯ãæ¥ä¸æ¥å°å¯¹è¡ä¸ºæè¿°ï¼è¡ä¸ºç»¼åï¼åæä¸ä¼åä¸ä¸ªä¸»è¦åæµç¨è¯¦ç»æè¿°ã

1ãè¡ä¸ºæè¿°

å½æ们æHLSææ¯çèµ·ç¹ç«ä¸ºä¸ç§è¡ä¸ºæè¿°è¯è¨çæ¶åï¼å°±éè¦è½¯ä»¶è¯è¨éµå¾ªç¹å®çè¡ä¸ºæè¿°è§èï¼å¹¶ä¸åé¤ä¸äºæºèªäºè½¯ä»¶ç³»ç»ççæç»´ç念ãè½ç¶å个HLSå·¥å ·çè¡ä¸ºç»¼åé½æèªå·±çè§èï¼ä½æ¯å ³äºå¨æå ååé ç约ææ¯å ±éçï¼ç¦æ¢éå½åå¨ææéã

å½æ°éå½æå³çéè¦è½å¤å¨æçæçµè·¯æ¨¡åï¼å¨ææéæ¯æè¿è¡æ¶æéå¼å¯ä»¥ä»»æååçæéåéã 硬件ä¸åè½¯ä»¶å ·æ大åç主å åï¼åªæåå¸å¨å±é¨çå åï¼æ以æ¯è¾éå并è¡å®ç°ãå¨ææéè¦æ±ä½ä¸ºå¯¹è±¡ç访é®å®ä½å¨è¿è¡æ¶ååï¼è¶ åºäºæ°åçµè·¯æ¦å¿µçä¸ç§åè½ãåæ ·ï¼è¶ åºäºæ°åçµè·¯æ¦å¿µçè¿æ管çç³»ç»å ååé çç³»ç»è°ç¨å½æ°çï¼å¨æ¤ä¸ä¸ä¸å举äºã

è¡ä¸ºæè¿°çæ¦å¿µï¼è®©æ们æç¡®äºé对æ°åçµè·¯ç¹æ§ä½¿ç¨é«å±æ¬¡è¯è¨å»ç¼åè¡ä¸ºä»£ç çè¿ä¸è®¾è®¡åºæ¬ååãèåæ¢è®¨ä»£ç é£æ ¼ï¼coding styleï¼,ç³»ç»ä¼åé½ç±è¿ä¸åºæ¬åå延ç³ãè¿å°±æ¯ä¸ºä»ä¹æ们åçCè¯è¨ä»£ç ä¼æä¸ç§ä»äºç¡¬ä»¶ä¸è½¯ä»¶è®¾è®¡é£æ ¼ä¹é´çæ ¹æ¬åå ã

è¡ä¸ºæè¿°çåºæ¬å¯¹è±¡æè¾å ¥è¾åºæ¥å£ï¼æ°æ®ä½å®½ï¼å¹¶è¡åæè¿°ççï¼å¨ Vitis HLS ä¸æè¡ä¸ºæè¿°çè§èåæ¨èçåæ³ççï¼å¨å±å¼ä»ç»ä¹åï¼æ们å æç¡®è¡ä¸ºç»¼åçæµç¨ã

2ãè¡ä¸ºç»¼å

å¨è¡ä¸ºç»¼åçè¿ç¨ä¸ï¼è¡ä¸ºæè¿°ä¸ä½¿ç¨çåéï¼æ°ç»ï¼è¿ç®åå«ç¨å¯åå¨(FF,LUT)ï¼å±é¨å å(URAM,BRAM,DRAM)ï¼è¿ç®å¨ï¼DSPï¼ALUï¼çæ°åçµè·¯åå æ¥å®ç°ãè¡ä¸ºæè¿°ä¸çå¤çæµç¨ï¼é¡ºåºæ§è¡, åæ¯ï¼å¾ªç¯å以æéç¶ææºï¼FSMï¼çå½¢å¼æ¥åç°ãéè¿åæè¡ä¸ºæè¿°ï¼å¯ä»¥å°è¿ç®çä¾èµå ³ç³»è¡¨ç¤ºä¸ºæ°æ®æµå¾ï¼DFGï¼ï¼å°æ§å¶æµç¨è¡¨ç¤ºä¸ºæ§å¶æµå¾ï¼CFGï¼ã

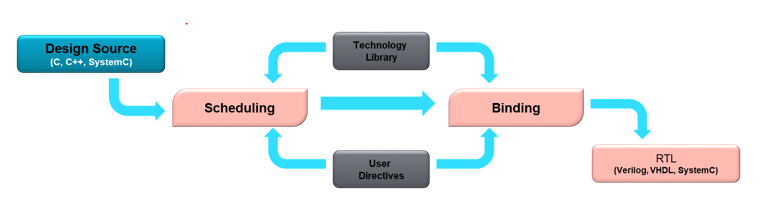

åæå°è¿é两个é常éè¦çè¡ä¸ºç»¼åæ¦å¿µåºç°äºï¼å°±æ¯è°åº¦ï¼schedulingï¼åç»å®ï¼Bindingï¼.

æ ¹æ®æ°æ®æµå¾åæ§å¶æµå¾æ¥å³å®è¿è¡é¡ºåºåè¿è¡é度çè¿ç¨ç§°ä¸ºè°åº¦ã

å°åéåè¿ç®æ å°å°å¯åå¨æè¿ç®å¨çè¿ç¨ç§°ä¸ºç»å®ã

ä¸å¾ç®æ´æäºå°ä»ç»äºä»Cè¯è¨è®¾è®¡å°å¯¼åºRTL设计è¿ç¨ä¸ï¼ä¾æ®HLSåºåç¨æ·æ令è¿è¡è°åº¦åç»å®çè¿ç¨ã

è¿éæ们使ç¨ä¸ä¸ªé常ç®åçä¾åæè¿°ä¸ä¸è¡ä¸ºç»¼åçè¿ç¨

(1) Compilation and Transformation å°ä¸ä¸ªè¡ä¸ºæ述代ç ç转å为æ°æ®æµå¾DFG

æ°æ®æµå¾ç±å¾å¤æ°æ®èç¹ç»æï¼æéè¦çæ¯è¡¨è¾¾åºäºå个èç¹ä¸æ°æ®çä¾èµå ³ç³»ï¼è¿æ¯åé¢è°åº¦åç»å®çåºç¡ã

å¨è¿ä¸ªæ¥éª¤ä¸ï¼ä»£ç é£æ ¼æ¯ä¸ä¸ªæ¯è¾å

³é®çå ç´ ãHLSå¨è½¬åè¿äºç¹å¤é«å±æ¬¡è¯è¨è¡¨è¾¾çæ¶åï¼æ个å«æ

åµä¼æ æ³è¯å«ä¸äºåµå¥é常深ç软件ç®æ³,ä¹ä¼å¢å ç¼è¯æ¶é´. æ以尽éç®æ´ï¼é»è¾ææ°ç硬件å好代ç ä¼æåå¼åæçã

ï¼2ï¼ Scheduling è°åº¦

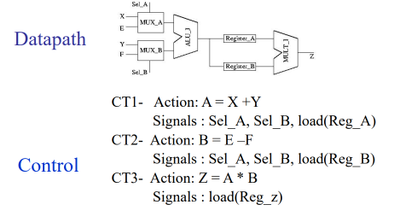

å¨æ°æ®æµå¾ä¸ï¼æ们çå°XYåEFæ°æ®ä¹é´æ²¡æä¾èµï¼ä»ä»¬å¯ä»¥éæ©å¨åä¸ä¸ªControl Stepéé¢å¹¶è¡æ§è¡,æè å¨ä¸¤ä¸ªSTéé¢é¡ºåºæ§è¡.

è¿ä¸ªè¿ç¨ä¸è°åº¦ç并è¡æ§ç±HLSç¼è¯å¨ï¼ç¨æ·æ令å

±åä½ç¨å½±åçï¼æ¯å¦ç¼è¯å¨ä¼ä¸»å¨åç°å¯ä»¥å¹¶è¡çä¼åç¹èªå¨ä¼åï¼ä¹ä¼è¯¯ä»¥ä¸ºæäºè¡¨è¾¾å¼åå¨æ°æ®ä¾èµæ æ³å¹¶è¡ä¼åçï¼æ以ä»éè¦ç¨æ·å å

¥æ令说ææ

åµã å½ç¶è¿½æ±æ´é«ç并è¡æ§å¯¹èµæºä¹ææ´å¤§çéæ±ï¼æ以并ä¸æ¯ä¸åè°åº¦é½ä»¥æ大并è¡æ§ä¸ºç®æ ã

ï¼3ï¼ Binding

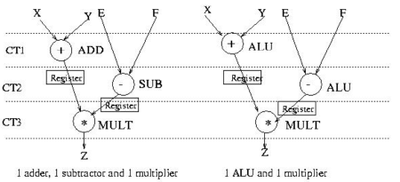

å¨æ©æçHLSç 究ä¸ï¼Allocation å Binding æ¯åå¼ç两个æ¥éª¤ãå ¶ä¸Allocation éå®äºèµæºçæ°éåç±»åï¼Bindingå®æäºè¿ç®å°èµæºçæ å°ãç°å¨æ们就ç»ç§°è¿äºæä½å¨Bindingæ¥éª¤å®æãæ©æFPGAä¸çå«æä¸ç§éæçç®æ³åå ALUï¼å¦ä»DSPè¿æ ·ç硬件模åå·²ç»å å«äºALUåä¹æ³å¨æ¨¡åççã

ä¸å¾åºäºæ©æçALUåå

æ示äºBinding çå¯è½æ§, å°å åæ³æä½æ å°å°å¯åå¨è¿æ¯ALU模åï¼åç°äºä¸¤ç§ä¸åçæ¹æ¡.

以ä¸æ¯éæ©äºä½¿ç¨ä¸ä¸ªALUã两个å¯åå¨ãä¸ä¸ªä¹æ³å¨ç综åç»æã对äºæ¢å®çè°åº¦æ¹æ¡ï¼å¯ä»¥éè¿è¡ä¸ºç»¼åæ¥çæç¸åºçç¶ææºãHLSå¨è¡ä¸ºç»¼åçè¿ç¨ä¸ï¼é¤äºè¾¾å°ç®æ³çåºæ¬åè½ï¼æ´éè¦çæ¯éæ©ä¸åçç»å®åè°åº¦æ¹æ¡å¨èµæºãæ§è½ãååéçå个ææ ä¸åæè¡¡ååèã

3ãåæåä¼å

çµè·¯çè§æ¨¡åè¿è¡æ¶é´åå¨æè¡¡å ³ç³»ï¼æ以产çæä¼åçRTLæè¿°éè¦å¼åè æä¾å¤§è´çä¼åæ¹éï¼çè³æ¯æç¡®çä¼å仿çã

å æ¤Xilinxçé«å±ç»¼åå·¥å ·æä¾äºä¸ç³»åæ§è½è¯ä¼°çåè½ååç¼è¯å¨æåä¼åæ¹å¼çéå¾ãé对è¡ä¸ºæè¿°è¿è¡è¡ä¸ºç»¼å,å¯ä»¥è·åå¦ä¸å¤ç§æ§è½ææ :

â¢é¢ç§¯ï¼çµè·¯è§æ¨¡ï¼ï¼æ ¹æ®èµæºå®æ½è®¾è®¡æéç硬件èµæºé

å¨FPGAä¸å¯ç¨ï¼å æ¬æ¥æ¾è¡¨ï¼LUTï¼ï¼å¯åå¨ï¼Block RAMåDSP48ã

â¢å»¶è¿ï¼å½æ°è®¡ç®ææè¾åºå¼æéçæ¶éå¨ææ°ã

â¢åå§åé´éï¼IIï¼ï¼å½æ°å¯ä»¥æ¥åæ°è¾å ¥æ°æ®ä¹åçæ¶éå¨ææ°ã

â¢å¾ªç¯è¿ä»£å»¶è¿ï¼å®æ循ç¯çä¸æ¬¡è¿ä»£æéçæ¶éå¨ææ°ã

â¢å¾ªç¯å¯å¨é´éï¼ä¸ä¸æ¬¡å¾ªç¯è¿ä»£å¼å§å¤çæ°æ®ä¹åçæ¶éå¨ææ°ã

â¢å¾ªç¯å»¶è¿ï¼æ§è¡å¾ªç¯ææè¿ä»£ç循ç¯æ°ã

è¿äºæ§è½ææ çè¡ä¸ºç»¼åç»æé½ä¼å¨HLSå·¥å ·çæ¥åä¸æåºï¼å¼åè éè¦æ¾åºæ§è½ç¶é¢æè æ§è½è¿å©çé¨åãé对循ç¯çä¼åæ¹å¼ç±æµæ°´çº¿ï¼pipelineï¼æå±å¼(unroll). æ¤å¤è¿ææ示è¿ç®å¨ç并è¡æå ±äº«ï¼æ示æ°ç»çæåï¼partitionï¼å访é®è°åº¦ï¼æ示åè½å½æ°çå èï¼inlineï¼ççãè¿äºä¼åæ令ç¸äºä½ç¨ï¼éè¦ä»å ¨å±åºåç¡®å®ä¼åæ令ã

å½è¿è¡è¯¦ç»çä¼åæ令ä¹æ æ³è¾¾å°é¢æçææ æ¶ï¼å°±éè¦èè代ç æ¬èº«çä¼åãè¿å°±éè¦å¼åè å¨è®¾è®¡æ¨¡åï¼å½æ°ã循ç¯çï¼æ¶çµæ´»è¿ç¨å¹¶è¡ãæµæ°´çº¿çæ¶æï¼å¹¶å¨å åç解è¡ä¸ºç»¼åæºå¶çåºç¡ä¸ç¼åæ´å®¹æçæé«æ硬件è¡ä¸ºæè¿°ç代ç ã

4ãæ¥å£è¿æ¥

è¡ä¸ºæè¿°åç模åéååå ¶ä»æ¨¡å群æ´åï¼æ以就è¿æ¸¡å°èèå¦ä½è®¾è®¡ç«¯å£ç±»åä¸å ¶ä»IPè¿è¡å®ä¾åè¿æ¥äºã

å¨RTL设计ä¸ï¼æ°æ®éè¿ç«¯å£è¿åºIPï¼è¿äºç«¯å£å¯ä»¥ä½¿ç¨åºç¹å®çIPæ¥å£åè®®ï¼AXI-Master/ AXI-liteï¼æ¥è¿è¡æä½. è¿åºIPçæ¯ä¸æ¡æ°æ®ï¼é½åºè¯¥å°å ¶æå®ä¸ºä¸»æºæ件ä¸çä¸ä¸ªç¬ç«å½æ°å®åã该å½æ°å®åå°ä¼è¢«ç»¼å为硬件RTLä¸çä¸ä¸ªç«¯å£ã

æ°æ®ç«¯å£çç±»å大æ¦å为以ä¸ä¸ä¸ªå¤§ç±»ï¼

1ãç´æ¥è¯»åæ°æ®å¼çå¯åå¨å¼

2ãæç §éåæ¶åæ°æ®çæ°æ®æµå¼

3ãæå®å°åè¿è¡è¯»åçå åæ»çº¿æ¨¡å¼

ä¸åæ¥å£è½å¤ä¸ºä¸å设计æä¾æä¼æ§è½ï¼æ¯å¦æ°æ®æµæ¥å£æ´éåäºæ°æ®é©±å¨ååºç¨ï¼ä¸ºäºæ´é«æå°ä¼ è¾æ°æ®ç»å¸¸å¨åéåæ¥æ¶åæ¹ä¹é´æå ¥FIFOç¼å²å¨ãè¿æ ·ç使ç¨è§å为FPGA硬件å¼åè æçç¥ï¼è½¯ä»¶å¼åè ä»éè¦æ·±å ¥ç解ã

ä¸è¡¨ä¸ºVivado Design Flow ä¸çæ¥å£ç±»åå·²ç»åéç±»åçå

³ç³»ã å

¶ä¸æ éï¼æ°ç»ï¼æéåhlsæ°æ®æµæ ¼å¼å¯¹åºçé»è®¤æ¥å£æ¨¡å¼æ 注为Dï¼æ¯æçæ¥å£æ 注为1ï¼ä¸æ¯æçæ¥å£æ 注为3, ï¼æ¯ä¸ä¸ªéè¦ç设计åèè¡¨æ ¼ã

æ¬ç« èéè¿æ示HLSå·¥ä½çåºæ¬æ¦å¿µè®©å¤§å®¶å¯¹ææ¯æäºå®è§ä¸çç解ãè¿ä¸ä»½å®è§ä¸çç解è½ç¶æµ æ¾ææï¼ä½æ¯å®å°åºäºCPUçæ¶æç软件ç¨åºä¸å¨é«å±æ¬¡ç»¼åè¿é¡¹ææ¯ä¸è¡ä¸ºæè¿°è¯è¨ååºäºææ¾çåºåãèµçµæçHLSå®æ¹æåä¸ï¼å¯¹æä¸æå°äºç«¯å£åè®®ï¼ä¼åæ令ï¼æ°æ®ç±»åçé½æé常详ç»ç解éãæ¬ç³»å以åçæç« å°éåHLSå éçåºç¨åºæ¯åºåï¼éç¹è®²è§£æ°æ®ä¼ è¾çæ¶æä¼å以åå¦ä½ç¼åé«æç硬件æè¿°C代ç ã

åå¨æåï¼

"为ç°åºå¯ç¼ç¨é¨éµåçé«å±æ¬¡ç»¼å建ç«çç®æ³åºç¡âæ¾è·IEEE计ç®æºåä¼å¹´åº¦ææ¯æå°±å¥çä¸äº¬çææå¨ASPDAC ä¼è®®ä¸å¯¹é«å±æ¬¡ç»¼åææ¯æªæ¥çå±æï¼

ä¸ä¸ªæ§è½ä¼äºCPUçä¼ç§çé«å±æ¬¡ç»¼å设计çHLS C/C++代ç å¯è½ä¼å¾é¿ï¼çè³ååå§ä»£ç ç¸æ¯é¢ç®å ¨éã类似è¿æ ·å¯¹äºä¸ä¸ªè½¯ä»¶ç¨åºåè¿è¡å¸¸å¹´çHLS C/C++代ç çè®ç»å¹¶ä¸æ¯å¯æ¨å¹¿åææçç模å¼ãä½æ¯å¨å¯å®å¶è®¡ç®ææ¯çé¿æ²³ä¸ï¼ç§å¦å®¶åç 究è 们å¸ææ 论软硬件工ä½äººåï¼é½åªè¦ç»è¿ä¸äºåºæ¬ä¼åç论çè®ç»å°±å¯ä»¥éè¿å软件代ç å¾å°ä¼äºéç¨CPUç设计ãè¿æ ·å¤§å®¶æè½å¹¿æ³ä½ä¼å°å¯å®å¶è®¡ç®è½å¤å¸¦æ¥ç好å¤[4]ã

åèï¼

[1] D. D. Gajski and L. Ramachandran, "Introduction to high-level synthesis," inâ¯IEEE Design & Test of Computers, vol. 11, no. 4, pp. 44-54, Winter 1994, doi: 10.1109/54.329454.

[2] 天éè±æ´, FPGA åçåç»æ

[3] High-Level Synthesis - Saraju P. Mohanty http://www.smohanty.org/Presentations/2001/MohantyHLS2001Talk.pdf

[4] aspdac20_keynote.pdf https://ucla.app.box.com/s/l2l1158ze86h38xj5sglgkcrjqz12cxg