领域专家和硬件工程师运用 MATLAB® 和 Simulink® 开发原型和生产应用程序,以部署到 FPGA、ASIC 和 SoC 设备。

借助 MATLAB 和 Simulink,您能够:

MATLAB 和 Simulink 产品适用于各种应用,如交流电机控制、软件无线电和嵌入式视觉。

“Simulink 环境最适于探索系统级的总体结构。与我们以前的工作流程相比,仿真快了 200 倍,而且 Simulink 模型很容易转换成 C 以及 HDL 代码,实现了高伸缩性和可重用性。”

—— Ken Chen, Faraday

ASIC 设计建模

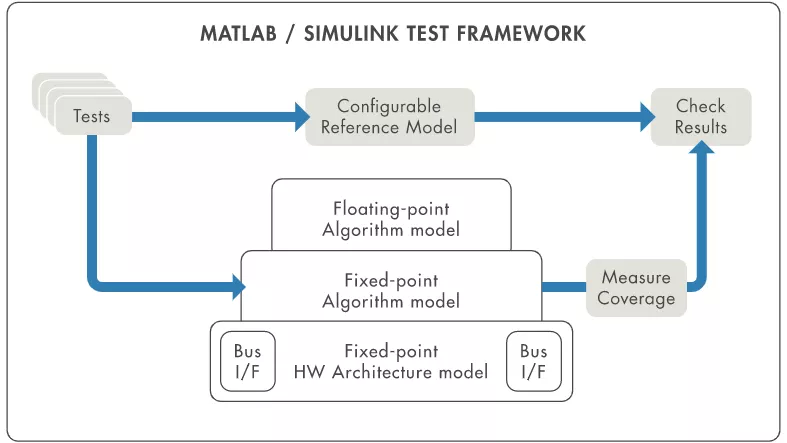

将硬件架构添加到您的数字算法。其中不仅包括定点量化,助您提高资源利用效率;还包括本机浮点代码生成,助您更轻松地在 FPGA 上开发原型。重用您的测试和黄金参考算法可以仿真每次后续优化。

HDL Coder™ 直接使用 HDL 就绪的 Simulink 和 MATLAB 函数块及 Stateflow® 图表生成可综合的 VHDL 或 Verilog。您可以从同一模型生成代码,以进行早期的 FPGA 原型建立和生产实现。此方法可提供硬件设计和验证工作流程的敏捷性和重用性。

片上系统行为仿真

在高抽象级别上综合进行数字、模拟和软件功能建模,以便在实现之前发现并消除系统级错误和性能问题。使用 SoC Blockset™ 仿真内存以及内部和外部连接,以及调度和 OS 效果。

使用 Simulink Test™ 构建并自动执行系统级测试用例;使用 Simulink Coverage™ 报告指标,以期满足您的需求。

优化子系统的同时,持续验证 SoC,确保整个项目的等价性和 SoC 级兼容性。

提前开始验证

HDL Verifier™ 重用 MATLAB 和 Simulink 测试环境来验证您的 FPGA 设计。

采用协同仿真时,您可以自动运行 MATLAB 或 Simulink 测试平台,该测试平台连接到 Mentor Graphics 或 Cadence Design Systems 仿真器中运行的 Verilog 或 VHDL 设计。

将模拟模型或数字模型导出为 SystemVerilog DPI 组件,以便在 Synopsys、Cadence Design Systems 或 Mentor Graphics 的 SystemVerilog 仿真器中用作参考模型、激励模块或快速仿真模型。

生产 ASIC 设计

领域专家和硬件工程师将 MATLAB 和 Simulink 协同用于无线通信、视频/图像处理、电机和功率控制和关键安全应用的生产 FPGA 和 SoC 设计。

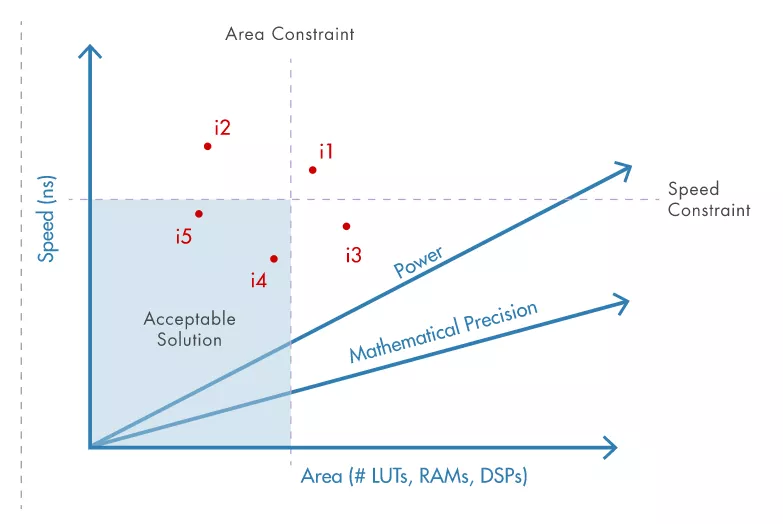

了解各种架构方案,然后使用 HDL Coder 高级综合优化达成实现目标。自动生成可追溯到模型和需求的可读 RTL。除了生成可综合且符合设计规则的 RTL 以外,HDL Coder 还会生成各种 AXI4 接口,以便轻松集成到您的 SoC。

文章来源:MATLAB