作者: Aicheng Tian,文章来源: Comtech FPGA微信公众号

1. 功能简述

随着视频图像和帧率的不断提高,传统的视频处理接口芯片的IO LVCOMS电平不能满足带宽要求。部分视频接收芯片的输出接口采用LVDS电平。LVDS具有高速、超低功耗、低噪声和低成本的优良特性。在实际应用中,采用现场可编程门阵列(FPGA)实现高速LVDS信号接收处理是性价比较高的技术途径。

随着半导体工艺的进步,FPGA的性能和集成度的不断提高,在Xilinx FPGA芯片中集成SelectIO资源,通过配置逻辑资源和I/O,可以生成支持LVDS标准的接口,实现高速LVDS 7:1数据接口互联通信。Xilinx® UltraScale™和Ultrascale+™ FPGA包含ISERDESE3和OSERDESE3组件模式基元,具有高速数据解串能力,差分LVDS信号的数据传输速度可以高达1600Mbps(Native模式)。

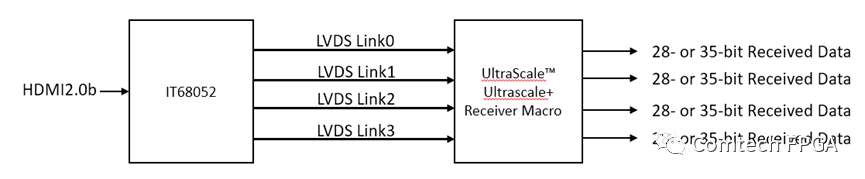

HDMI2.0b的接口芯片IT68052输出LVDS7:1串行化数据(图1),其单个差分对可以达到数据传输速度为415Mb/s-1100Mb/s,视频处理接口芯片RGB数据和控制数据经过编码后加嵌到LVDS的数据中传输,并有一路分频的同步时钟伴随。

本文介绍Xilinx® UltraScale FPGA实现LVDS 1:7接收数据解串,重点对系统组成、BUFGCE_DIV、时钟采样、数据恢复单元、时钟约束等关键技术进行了描述,并参考XAPP1315基于Xilinx FPGA进行了验证。

图 1: 1:7 接收端模块

2. 数据接收实现介绍

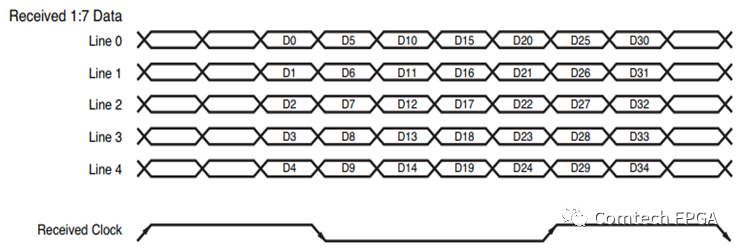

图2可以看到6个Line LVDS差分对,其中1个Line为时钟,5个Line为差分数据。其中Received clock为像素时钟,每个周期内共可发送5*7=35bits的数据,RGB 10bit所需的30bits外,另外的5bits可以⽤于传输DE、Vsync和HSync。由于Received clock和各个数据Lane的特殊的相位关系RGB 10bit,使得其并不需要去传输同步字。

Received clock对于FPGA接收端来讲是输入时钟,图2可以看到,它的占空⽐为3:4,⼀个时钟周期每条线传输7个bit的数据,对⽐正常的信号传输,1个clock 只能传1个bit的数据,所以传输RGB 8bit或者RGB 10bit数据只需要4个Line或者5个Line。

图 2: 1:7 接收数据

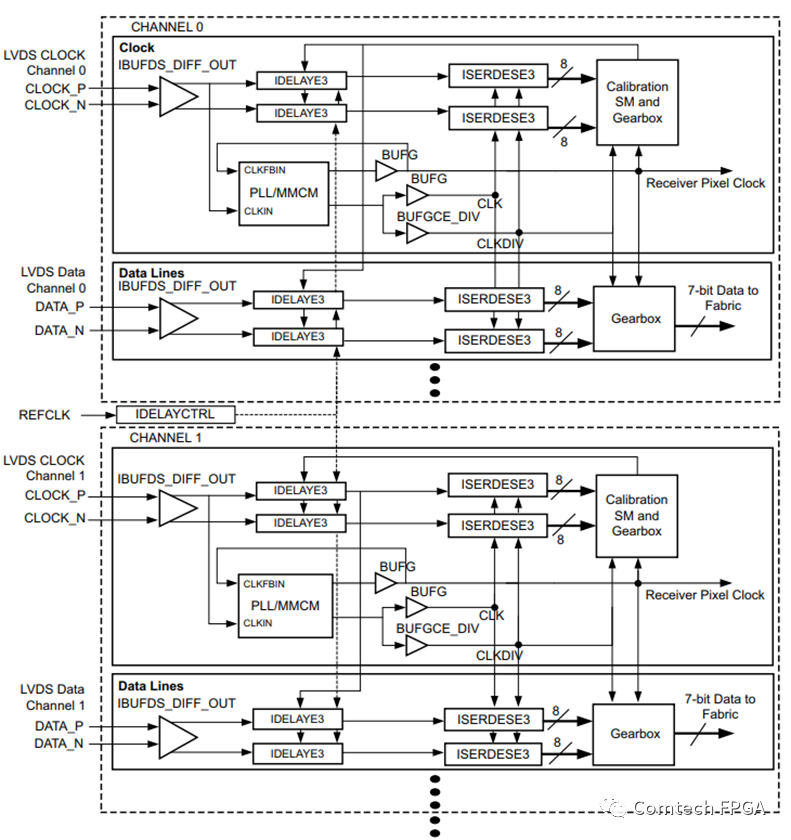

由于接收的数据流是输入时钟速率的7倍,时钟信号被用作接收数据的信号。在一个时钟周期内,数据线有7个状态变化。接收器使用1:8 DDR模式的ISERDESE3和基于8:7 Distributed RAM 的gearbox(如图3所示)来bit拼接调整和对齐输入数据流。

首先LVDS clock输入处理变成三个时钟域,一个1/2速率的采样时钟(rx_clkdiv2),一个1/8速率的反序列化数据时钟(rx_clkdiv8),以及一个1/7的像素时钟(px_clk),这相当于原始接收器源时钟。

接收器源时钟在MMCM或PLL中乘以7或14以满足VCO的频率范围,然后除以2以产生1/2速率的采样时钟(rx_clkdiv2),再除以7以产生接收像素时钟(px_clk)。1/8速率的反序列化数据时钟 (rx_clkdiv8)由1/2速率采样时钟MMCM或PLL输出产生,使用BUFGCE_DIV,以尽量减少ISERDESE3 CLK和CLKDIV输入之间的时钟偏移。

BUFGCE_DIV# (.BUFGCE_DIVIDE(4))

bg_rxdiv8 (

.I(rx_pllmmcm_div2),

.CLR(!cmt_locked),

.CE(1'b1),

.O(rx_clkdiv8)

);

除了直接路由到MMCM或PLL外,输入像素时钟还通过IDELAYE3元件连接到两个ISERDESE3(如图3所示)。第二个IDELAYE3和ISERDESE3是可以使用的,因为输入标准是LVDS,这是一个差分输入。在使用IBUFDS_DIFF_OUT时,差分输入可以连接到两个相关的延迟元件。

主延迟的初始延迟被设置为零。从属延迟被设置为偏移了一个半位周期。通过递增延迟、采样和比较主从位,校准状态机确定了DDR采样时钟的理想延迟。这个过程完成后,校准的延迟值被广播到通道中的所有数据线。在这一点上,校准状态机完成了,不再做进一步调整。数据字对齐和8:7转换是在gearbox中管理的,在为像素时钟数据线确定后,它被广播到其余的数据线。

图 3:数据接收

图 4:数据接收1:7仿真

3. 接收端设计的考虑因素

在使用xapp1315参考设计时,需要考虑以下几点。

A. ISERDESE3的CLK和CLKDIV端口之间过大的偏移会导致接口上的接收器数据错位。为了尽量减少偏移,CLK和CLKDIV来自同一个MMCM/PLL时钟输出,为了进一步减少偏斜,必须使用CLOCK_DELAY_GROUP约束。

下面是一个XDC约束的例子。这个约束对于每个rx_channel_1至7模块必须是唯一的。该约束必须有一个唯一的名称(例如, ioclockGroup_rx1)和正确的分层实例名称(例如,rx_channel1)。

set_property CLOCK_DELAY_GROUP ioclockGroup_rx1 [get_nets {rx_channel1/rx_clkdiv*}]

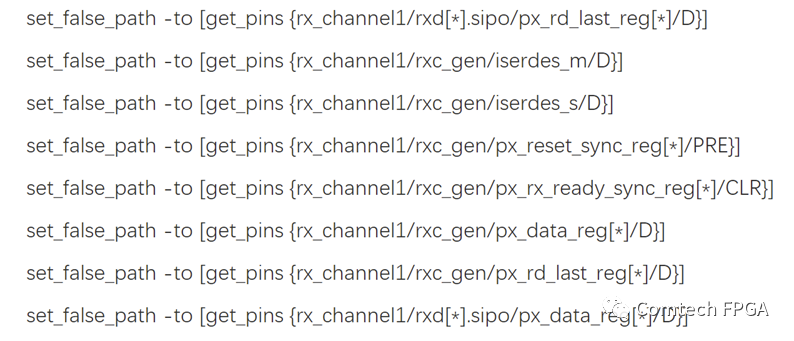

B. 接收器内的某些路径不需要计时,应标记伪路径以实现计时闭合。下面是一个XDC约束的例子。正确的分层实例名称,例如,rx_channel1,用于rx_channel_1~7 模块必须被使用。

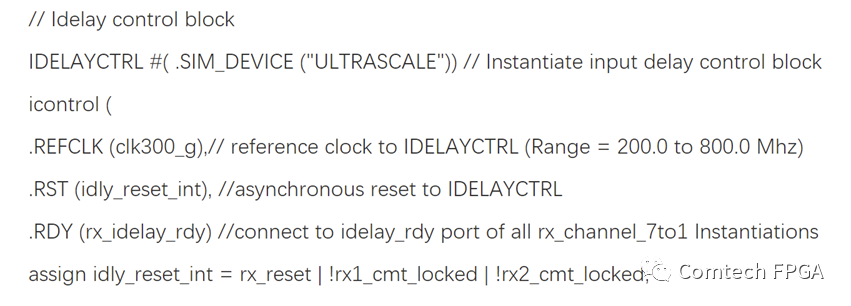

C. 为了使校准算法对bit时间有一个准确的读数,必须在设计的顶层实例化一个IDELAYCTRL块,其RDY输出连接到每个rx_channel_7to1实例化的idelay_rdy端口。一个实例是如下图所示。IDELAYCTRL块需要一个200-800MHz的时钟输入。这个时钟的频率(MHz)是作为属性REF_FREQ的值提供给rx_channel_7to1块的。IDELAYCTRL模块的复位(RST)必须复位清零在异步rx_channel_7to1实例的异步复位被释放并且接收机MMCM/PLL被锁定后。

4. 复位顺序要求

按照下面复位顺序:

A. 先对rx_channel_1-7复位清零;

B. 等待MMCM/PLL锁定置位;

C. IDELAYCTRL复位清零;

D. 当px_ready清零时,px_data输出总线有效;

如果您在LVDS高速传输数据方面有问题,欢迎联系

simonyang@comtech.cn

charlesxu@comtech.cn