本文转载自:图灵研究院微信公众号

1. UltraRam资源介绍

常规FPGA的片上存储资源有分布式Ram和Block Ram。分布式Ram存储的数据容量很小,一般也就Kb(kilo bits)的数量级。Block Ram为FPGA芯片的主要片上存储资源,容量能达到十多Mb(mega bits)的数量级。

随着现在FPGA工作的时钟频率越来越高,高速接口越来越多,即便容量达到十几Mb的数量级,片上用于缓存处理数据的存储资源仍然经常不够用或成为设计系统的瓶颈之一。

当然FPGA可以接片外高速存储设备,比如DDR颗粒,存储容量可达Gb量级。外接高速存储设备虽然有存储资源大的优点,但缺点是FPGA与外部设备之间必须通过高速接口来进行数据交换。高速接口一方面会增加数据读写方式的复杂度,一方面也有数据读写效率的开销,同时也会增大功耗的开销。

从存储资源容量上看,Block Ram与外围存储设备之间好像存在一个空白。因此UltraRam成为了填补该空白的新成员。

UltraRAM是UltraScale+™系列中最新的存储器模块,能实现高达500Mb的总片上存储容量,相当于赛灵思28nm FPGA片上存储器容量的6倍。

2. UltraRam细节与特性

2.1 容量大小

UltraRam可在设计中作为单个288Kb存储器,或者连接在一起构成更大的RAM 阵列。相同列中的所有UltraRam都可连接在一起,通过专用的级联路由传送地址、数据和控制信号。在Kintex UltraScale+和Zynq UltraScale+器件中,级联得到的RAM阵列可高达36Mb,在Virtex UltraScale+系列中,所有UltraRAM列都可通过光纤路由连接在一起,在最大器件中可构成容量达360Mb的存储器阵列。

2.2 读写特性

单个UltraRam模块的存储容量为288Kb,数据位宽为72bit,地址深度为4096。每个UltraRam模块都是一个双端口同步RAM。端口A和端口B共享相同时钟信号。在外部时钟的单个周期内,端口A操作总是在端口B操作之前完成。每个端口在每个时钟周期都可独立执行一个读操作或一个写操作。当两个端口在相同时钟周期内以相同地址(即地址冲突)执行写操作时,端口B的写操作有效,因为端口A 的写操作被覆盖。当端口A执行读操作,而端口B以相同地址执行写操作时,端口A 获得存储器阵列中的旧数据,然后端口B上的新数据被写到存储器阵列。其它地址冲突情况以此类推。

2.3 功耗特性

UltraRam提供各种内置功能以最大化功率效率,通常无需用户干预。这些功能包括:

(1) 将设计中不用的UltraRam断电;

(2) 自动对不使用的流水线寄存器进行时钟门控;

(3) 当UltraRam长时间不使用时,使其进入休眠模式。

UltraRam可通过手动或自动进入休眠模式。用户可以访问UltraRam的SLEEP 端口。激活SLEEP时,UltraRam从下个时钟周期开始进入休眠模式。休眠模式下,UltraRam SRAM存储器的外设逻辑断电,但SRAM保持加电并保留其中的内容。

3. UltraRam使用方法

与调用Block Ram不同的是,UltraRam不支持IP核的调用方式。但仍有三种方法可以在RTL设计中使用UltraRam。

方法一:编写代码以调用存储器

调用UltraRam代码的模板可以在vivado中查找到。打开vivado中的“Language Templates”。

在模板中选择“Verilog”->“Synthesis Constructs”->“Coding Examples”->“RAM”->“UltraRAM”

用户必须指定 ramstyle=“ultra” 才能明确指示vivado综合使用UltraRAM。

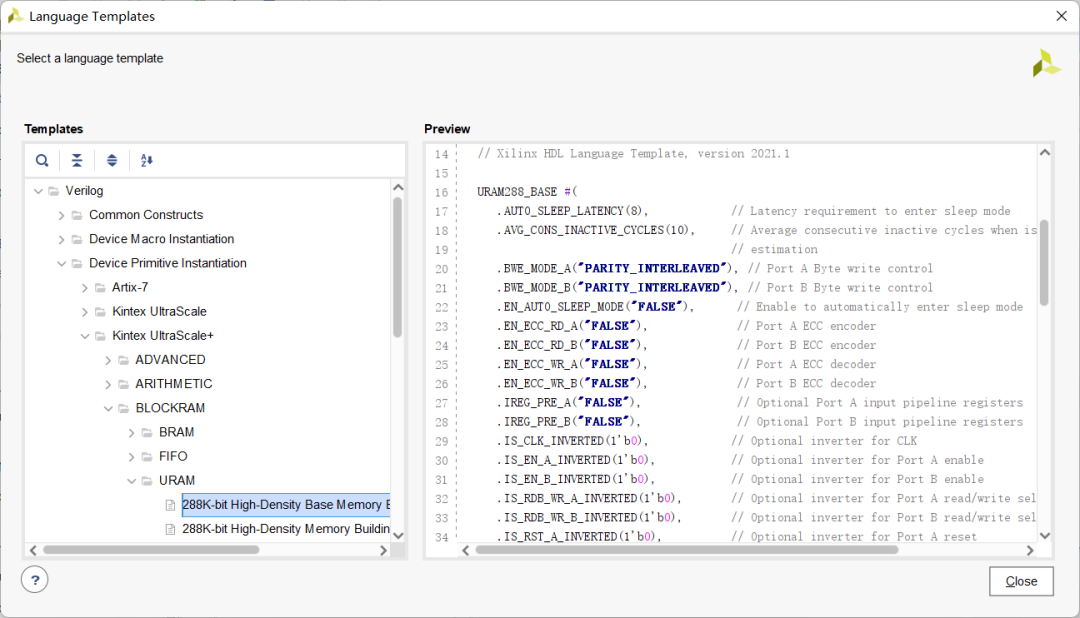

方法二:实例化器件原语

如果用户需要对UltraRam模块的连接具有完全控制权,应使用以下位置的器件原语:

在模板中选择“Verilog”->“Device Primitive Instantiation”->“Kintex/Virtex UltraScale+”->“BLOCKRAM” ->“URAM”

尽管用户能对UltraRam模块的连接实现最严格的控制,但因为模块控制的端口较多,这种使用方法会比较复杂。

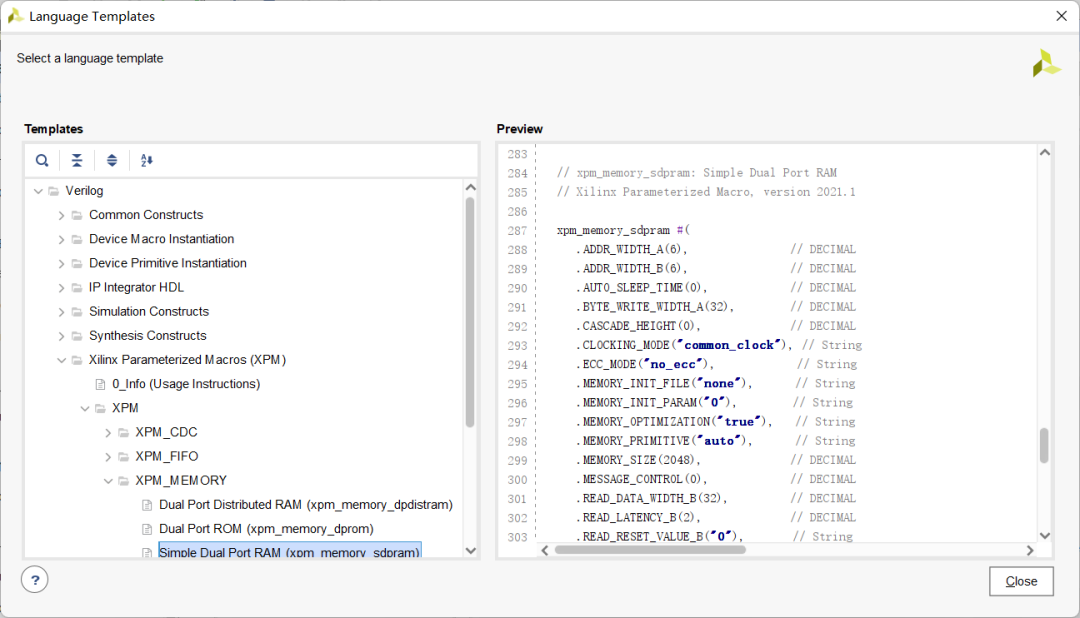

方法三:使用Xilinx参数化宏(XPM)

XPM是一种用来根据用户指定要求创建RAM和ROM结构的最新工具。用户可在XPM代码中指定多个参数,包括存储器大小或类型、时钟模式、ECC模式等。这些要求随后被vivado综合转化为适当的存储器阵列尺寸和风格。

通过XPM调用UltraRam的方法(也是Xilinx官方较推荐的方法):

在模板中选择“Verilog”->“Xilinx Parameterized Macros (XPM)”->“XPM”->“XPM_MEMORY” ->“Simple Dual Port Ram”

用户必须在MEMORY_PRIMITIVE类属上指定值UltraRAM,以明确指示vivado 综合使用 UltraRam。

本文使用的参考文献可以通过在公众号输入 URAM_XILINXDOC 来获取文档下载链接。

参考文献

[1] “Using UltraRAM in UltraScale+ Devices”, https://www.xilinx.com/video/fpga/using-ultraram-in-ultrascale-plus.html

[2] “UltraRAM: Breakthrough Embedded Memory Integration on UltraScale+ Devices”, WP477, Xilinx.

[3] “UltraScale Architecture Memroy Resources”, UG573, Xilinx.