作者:Fancheng Meng,AMD工程师

Versal设备的Axi bridge mode

Versal 系列的DMA axi bridge模式可以在PL的QDMA IP或者在CPM(The integrated block for PCIe® Rev. 4.0 with DMA and CCIX Rev. 1.0)的QDMA IP中选中,CPM内嵌在CIPS(Control Interfaces and Processing System)中。不同系列的Versal的产品可支持的PCIE最高速率不同,能够支持PCIE5.0协议的产品,例如VPK120,其CIPS内使用的是CPM5,而只能支持到PCIE4.0协议的产品,例如VCK190,其CIPS内使用的是CPM4。虽然CPM5和CPM4的地址转换参数都可以在界面中配置,但是CPM5与CPM4地址转换的配置方式相差很大。如果要在versal系列设备的PL中使用AXI bridge mode,需要打开QDMA的IP, 选择axi bridge mode。这一点与ultrascale系列不同,ultrascale系列设备的axi bridge mode需要在XDMA IP中打开。

CPM4 AXI bridge mode 的地址转换

如何将AXI地址转换为pcie地址

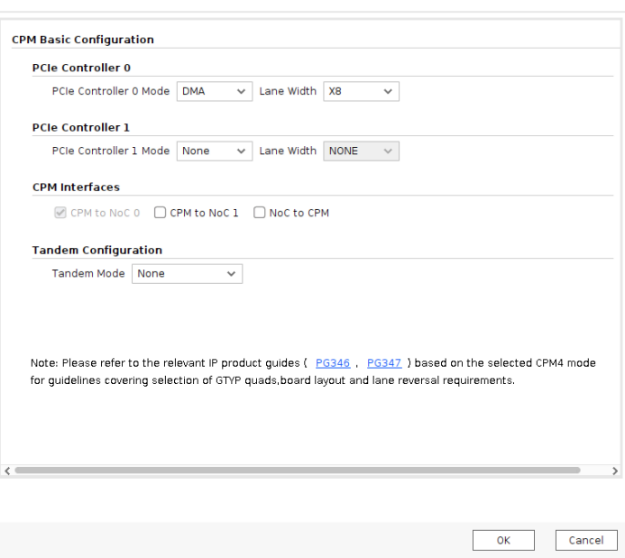

在CPM4的GUI配置界面中,通过配置AXIBAR的 参数,来实现将 AXI4 memory map (MM) 的地址范围映射到 PCIe的地址范围。在Vivado 2022.1中打开block design,在block design中添加CIPS IP。在配置CPM时,在PCIe Controller 0 mode中选择DMA,在Lane width中选择PCIE lane的数目。

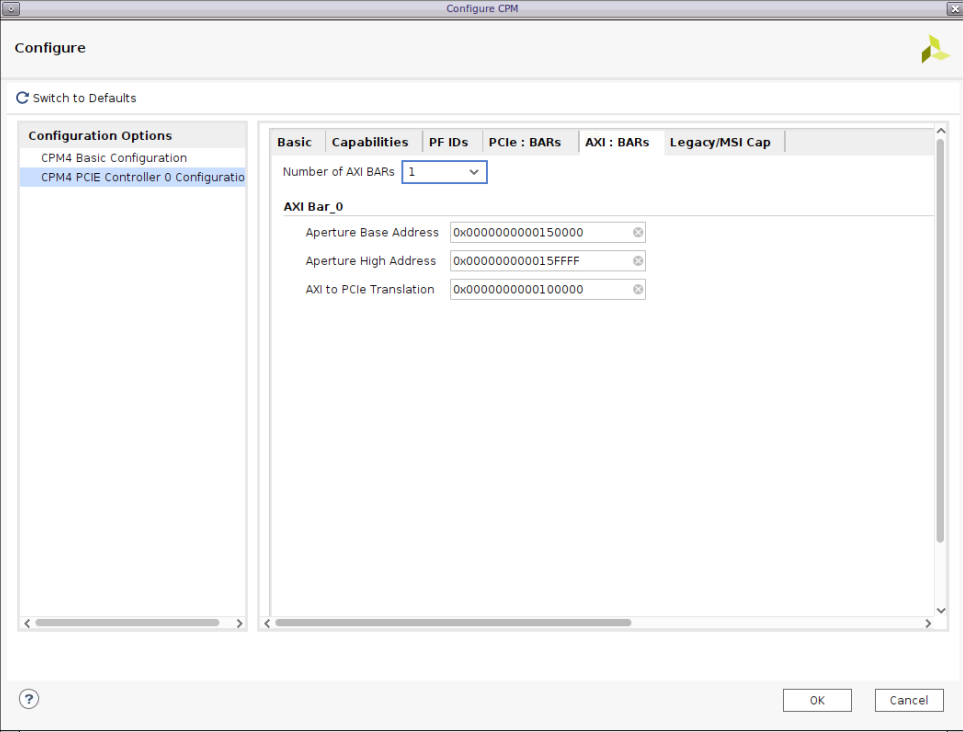

在CPM4 PCIE Controller 0 Configuration interface中,在Basic、Capabilities和legacy/MSI Cap等界面中选择所需的参数,然后打开AXI:BARs界面:

选择AXI bar的数量,AXI bar的数量取决于用户需要几段地址映射,想要将几段AXI的地址域映射到PCIE域,就选择几个bar。在进行地址映射时,可以选择将AXI地址映射到32位的PCIE地址或64位的PCIE地址,如果想要映射到32bit的PCIE地址,在AXI to PCIE Translation选项中,32到64位需要配为零,以生成32位地址的 TLP包,如果想要将AXI地址映射到64位的PCIE地址,需要把AXI to PCIE Translation的32到64位需要配成非0,才能生产64位地址的TLP包。Aperture base address和Aperture High address分别填写映射到PCIe地址域的AXI的起始地址和结束地址,以下通过举例分别对AXI地址映射到32位和64位PCIE地址,这两种情况进行说明。

示例1

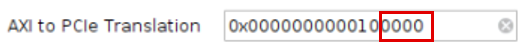

示例1是将AXI地址映射到32位的PCIe地址,使用下图所配置的参数,可以将AXI地址150000-15FFFF映射到PCIE地址100000-10FFFF。如果发送地址为150001的AXI数据包,则该IP会将其转换为地址为100001的PCIe数据包。

根据AXI 地址域的大小,AXI to PCIE Translation的位0-11位必须设置为零。

示例2

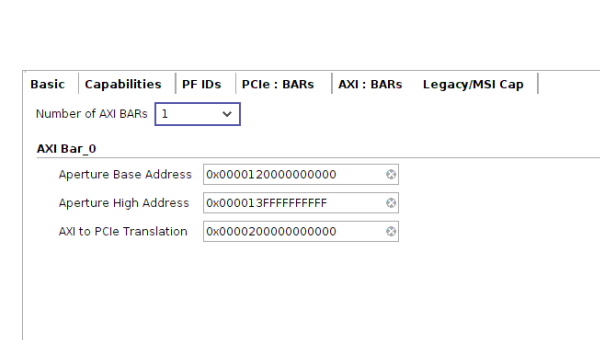

示例2是将AXI地址映射到64位PCIe地址,使用下面的参数,可以把AXI的地址0X120000000000-0x13FFFFFFFFFF映射到PCIe地址0X200000000000-0X21FFFFFFFFFFF。当发送AXI数据包的地址为0X12FFFFFFFFFF时,该IP会将地址为0X12FFFFFFFFFF的AXI数据包转换为地址为0X20FFFFFFFFFF的PCIe数据包。

PL Axi bridge mode的地址转换

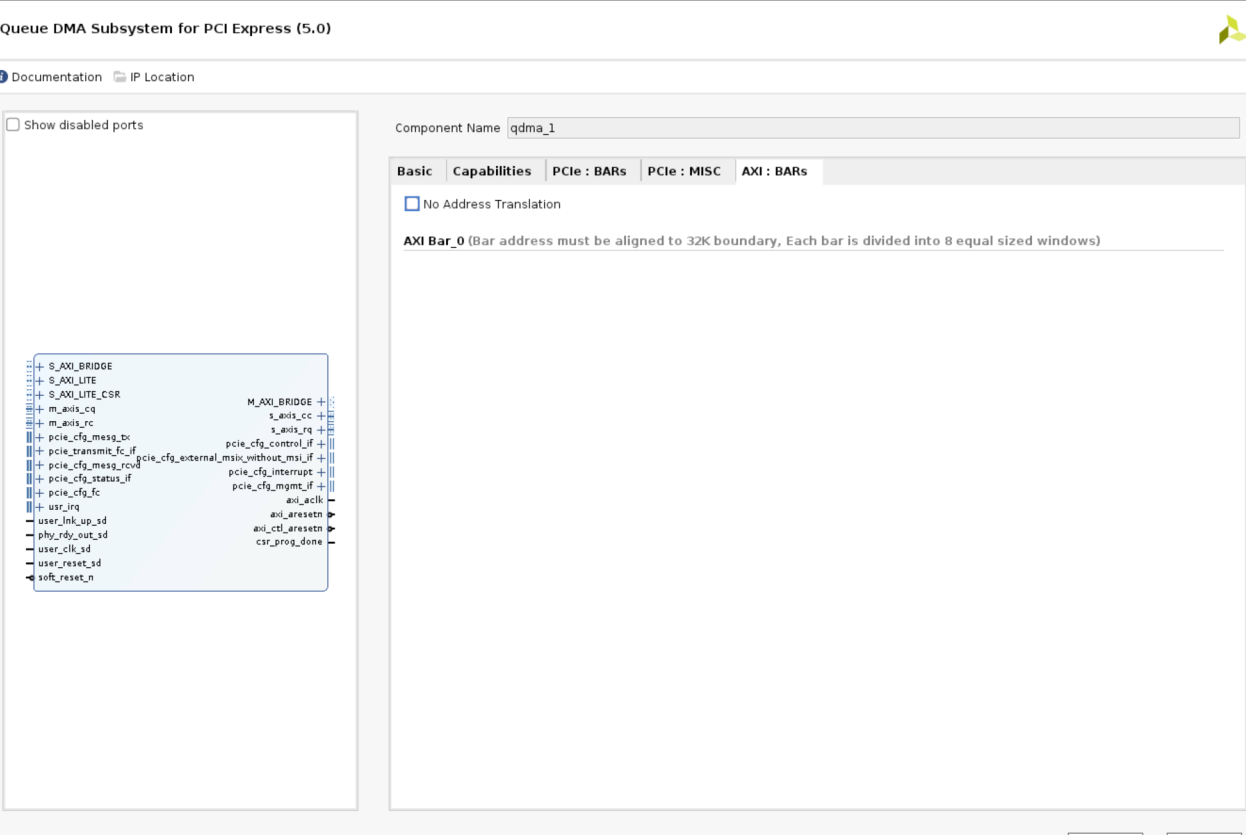

在block design中打开QDMA IP,在IP的function mode中选择axi bridge mode,在切换到axi bridge mode即可看到如下图所示,在GUI界面中多了AXI:BARs 选项,可以在下面选项中选择是否使用地址转换。

如果要使用地址转换功能,不要勾选上图选项。在进行地址转换时,地址的高位,以及转换的空间大小都需要在block design的address editor中选择,本次示例所选择的地址高位为AB0_0000_0000,空间大小为32G,具体配置如下图所示,起始地址、结束地址和空间大小分别是AB0_0000_0000,AB7_FFFF_FFFF,32g。

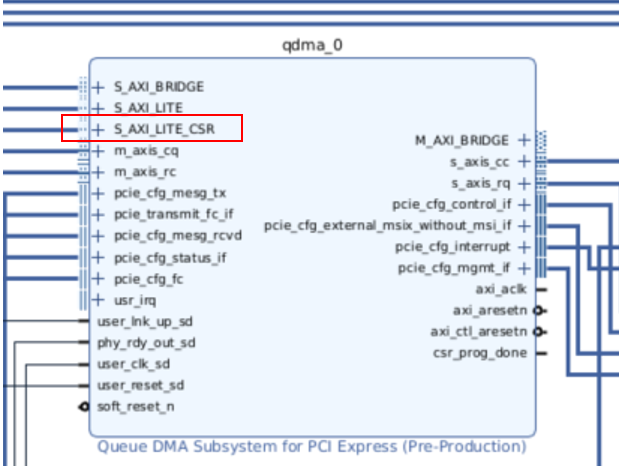

在进行完以上配置后,32GB的空间就被平均分成了8份。在Xilinx的手册中,通常称之为window,每个window的大小是固定的4GB,每个window的AXI起始地址和结束地址也固定了。用户可选择的是使用哪几个window,以及每个window使用多少空间。如何对每个window进行配置呢?在PG302上对此有所解释,AXI的地址转换的细节是基于BDF table进行配置,BDF table可以理解为AXI地址域到PCIE地址域的地址转换配置表,这张表可以通过s_axil_csr_*.接口进行配置,CSR接口如下图所示,这个接口在IP配置界面中是可以选中的。

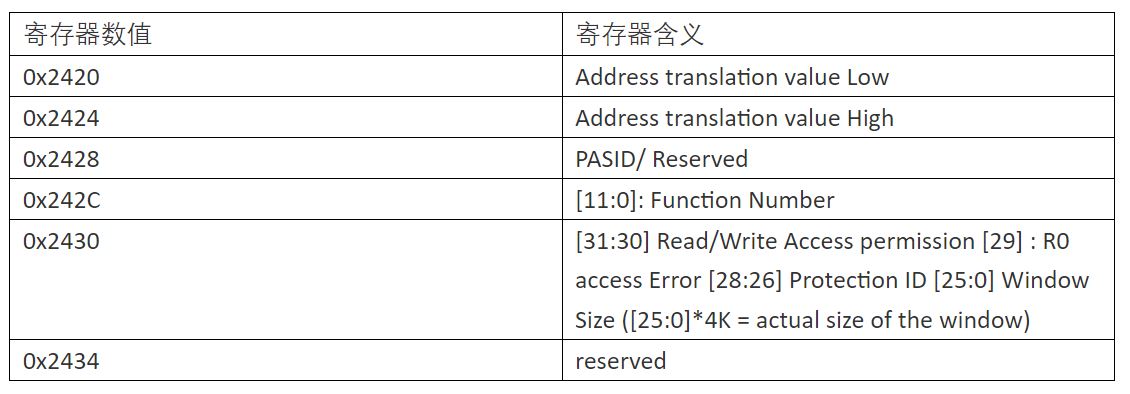

每个window都有6个寄存器与之对应,如果想要window生效,需要对这6个寄存器进行配置,第一个window的6个寄存器如下所示:

a. 0x2420

b. 0x2424

c. 0x2428

d. 0x242C

e. 0x2430

f. 0x2434

之后每个window的起始地址为0x2420 + (0x20 * i),i表示第几个window。6个寄存器代表的含义如下表所示:

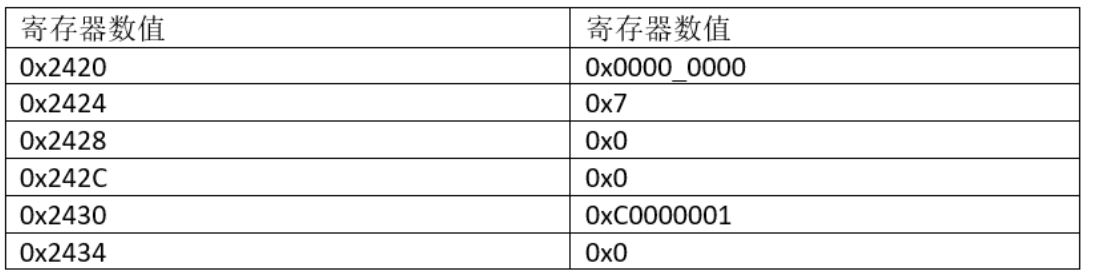

本篇blog通过2个window的配置流程对此机制进行说明,Window 0的大小为4 KB ,Window 1的大小为 4 GB。 Window0将AXI 地址的0x0000_0000_0000_0000-0x0000_0000_0000_0FFF转换到PCIE的地址0x0000_0AB7_0000_0000-0x0000_0AB7_0000_0FFF。 Window1将AXI地址的 0x0000_0001_0000_0000-0x0000_0001_FFFF_FFFF转换到PCIE地址的0x0000_0AB5_0000_0000-0x0000_0AB5_FFFF_FFFF.

Window0的BDF table配置如下:

如果AXI报的地址为0x0000_0000_0000_0100,经window0转换后的PCIE包的地址为0x0000_0AB7_0000_0100.

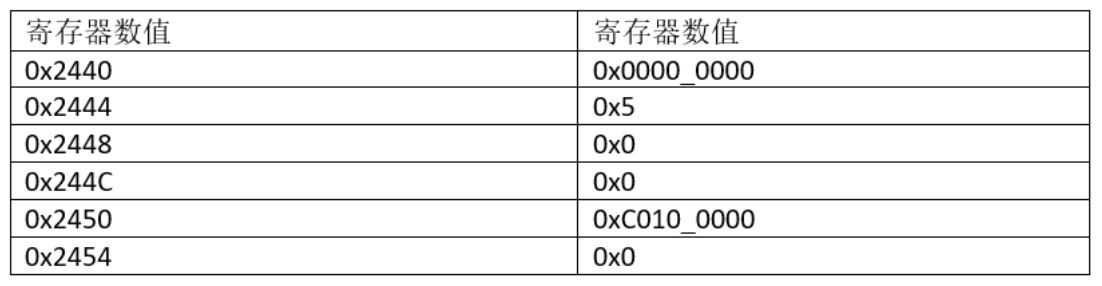

Window1的BDF table配置如下:

如果AXI包的地址为0x0000_0001_0000_0100,经window1转换后的PCIE包的地址为0x0000_0AB5_0000_0100.