文章来源:内容由半导体行业观察(ID:icbank)编译自servethehome,谢谢。

如今,AMD 拥有了一款新的巨型 FPGA。AMD VP1902 将成为世界上最大的 FPGA。此类 FPGA 旨在提供巨大的可编程逻辑阵列,专门用于模拟未来芯片的硅设计,范围从 Raspberry Pi 中的小型 SoC 到AMD Instinct MI300等大型下一代加速器。

上一代Xilinx VU19P在推出时是最大的FPGA,但新的VP1902增加了Versal功能,并采用了新的AMD小芯片设计,使FPGA的关键功能增加了一倍以上。

Xilinx 和 AMD 多年来一直拥有专门设计用于帮助芯片仿真和调试的生产线。对于那些不知道的人来说,设计芯片的一种非常常见的方法是使用工具将逻辑放入一系列大型 FPGA 上,然后在进行硅制造之前很好地模拟设计。随着芯片变得越来越大,需要使用的门的数量也会增加。没有真正的门与晶体管的比率,但人们告诉我们,硅中的 4 个晶体管大致相当于这些 FPGA 上的 1 个门,这是一个合理的近似值(有很多可变性)。

新型 AMD Versal Premium VP1902 有效地将可模拟多达 1850 万个逻辑单元的门数增加了一倍。除了额外的逻辑之外,AMD 还添加了更多的收发器和收发器上的更多带宽,以帮助连接更多设备以获得更大的仿真能力。对于某些参考框架,这些范围可以从一个或几个设备扩展到超过 1000 个连接的 FPGA,以模拟大型芯片设计。

除了拥有更多的可编程逻辑单元之外,AMD 还拥有 Versal Premium 系列的许多功能,而且也是该产品的独特功能。与 AMD Xilinx VU19P 相比,新的独特功能包括:

新款 VP1902 具有 16 个 PCIe Gen5 x4 硬核 IP 模块,而 VU19P 则具有 8 个 PCIe Gen4 x8。HPIO 到 XPIO 的升级应该会使芯片之间的延迟降低 36%。甚至还有一个很大的时钟速度更新。这些新的升级意义重大,而不仅仅是拥有更多的可编程逻辑单元。

所有这些额外的 IP 意味着该 IP 需要使用更少的可编程逻辑单元,因此更多的布局规划可用于仿真。AMD 还能够使用其 NoC 进行调试以及将设计恢复到特定寄存器状态等操作,以帮助调试过程。这也不需要构建所有这些功能。

这是一个巨大的芯片,AMD 正在做一些有趣的事情。它有两组mirrored和旋转dies(总共四组),组合成一个封装。如果您只看这个,您可能首先会认为它是第四代英特尔至强可扩展蓝宝石Rapids,而不是AMD设计。相反,它是 VP1902。

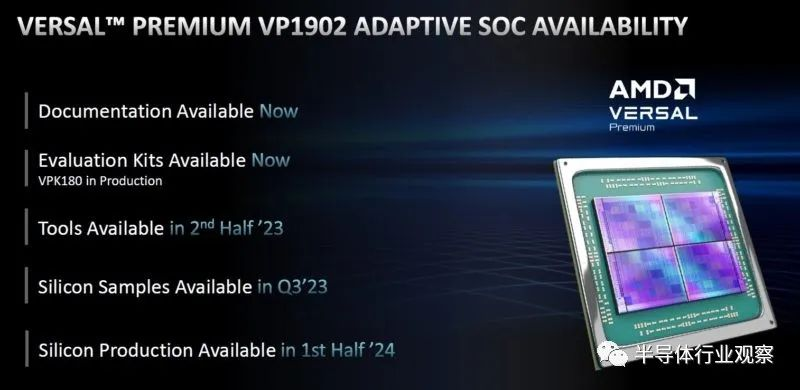

AMD 发布的最酷的部分之一是芯片将于下季度推出样品。Xilinx 历来早在出现任何可用性的曙光之前就发布了芯片,因此这是一个值得欢迎的变化。

AMD 推出全球最大的基于 FPGA 的自适应 SoC

AMD 今天宣布推出AMD Versal Premium VP1902自适应片上系统 (SoC),这是全球最大的自适应 SoC。VP1902 自适应 SoC 是一款仿真级、基于小芯片的设备,旨在简化日益复杂的半导体设计的验证。其容量是上一代产品的 2X ,设计人员可以自信地创新和验证专用集成电路 (ASIC) 和 SoC 设计,以帮助将下一代技术更快地推向市场。

人工智能工作负载正在推动芯片制造的复杂性不断增加,需要下一代解决方案来开发未来的芯片。基于 FPGA 的仿真和原型设计可提供最高水平的性能,从而实现更快的芯片验证,并使开发人员能够在设计周期中向左移动,并在芯片流片之前就开始软件开发。AMD 通过 Xilinx 带来了超过 17 年的领先地位和六代业界最高容量的仿真设备,每一代的容量几乎翻倍。

“提供基础计算技术来帮助我们的客户是当务之急。在仿真和原型设计中,这意味着提供尽可能高的容量和性能。”AMD 自适应和嵌入式计算集团产品、软件和解决方案营销公司副总裁 Kirk Saban 说道。“芯片设计人员可以自信地使用我们的 VP1902 自适应 SoC 来仿真下一代产品并制作原型,从而加速人工智能、自动驾驶汽车、工业 5.0 和其他新兴技术领域未来的创新。”

随着 ASIC 和 SoC 设计的复杂性不断增加,特别是随着基于 AI 和 ML 的芯片的快速发展,在流片之前必须对芯片和软件进行广泛的验证。

VP1902 提供业界领先的容量和连接性,提供 1850 万个逻辑单元,与上一代 Virtex UltraScale+ VU19P FPGA 相比,可实现2X 2更高的可编程逻辑密度和 2X 4聚合 I/O 带宽。

调试对于投片前验证和并行软件开发至关重要。在流片前查找并解决错误可以使项目按计划和预算进行。VP1902 自适应 SoC 利用 Versal 架构(包括可编程片上网络),与上一代 VU19P FPGA 相比,调试速度提高了 8 倍。

合作AMD Vivado 机器学习设计套件为客户提供了全面的开发平台,可快速设计、调试和验证下一代应用和技术,并加快上市时间。支持在 VP1902 自适应 SoC 上进行更高效开发的新功能包括自动设计收敛辅助、交互式设计调整、远程多用户实时调试和增强的后端编译,使最终用户能够更快地迭代 IC 设计。

AMD 与 EDA 社区密切合作,帮助客户将其创新和技术愿景变为现实。与 Cadence、Siemens 和 Synopsys 等顶级 EDA 供应商密切合作,可帮助设计人员访问功能齐全且可扩展的解决方案生态系统。

AMD Versal Premium VP1902 自适应 SoC 将于第三季度开始向抢先体验的客户提供样品,预计将于 2024 年上半年投入生产。