上周博文“Power Design Manager (PDM) 简介”已向大家简单介绍 PDM 以及 Versal™ 器件功耗从 XPE 迁移到 PDM 的简易迁移路径,作为补充本文将继续介绍最新版本 PDM 2023.1 的新增功能。

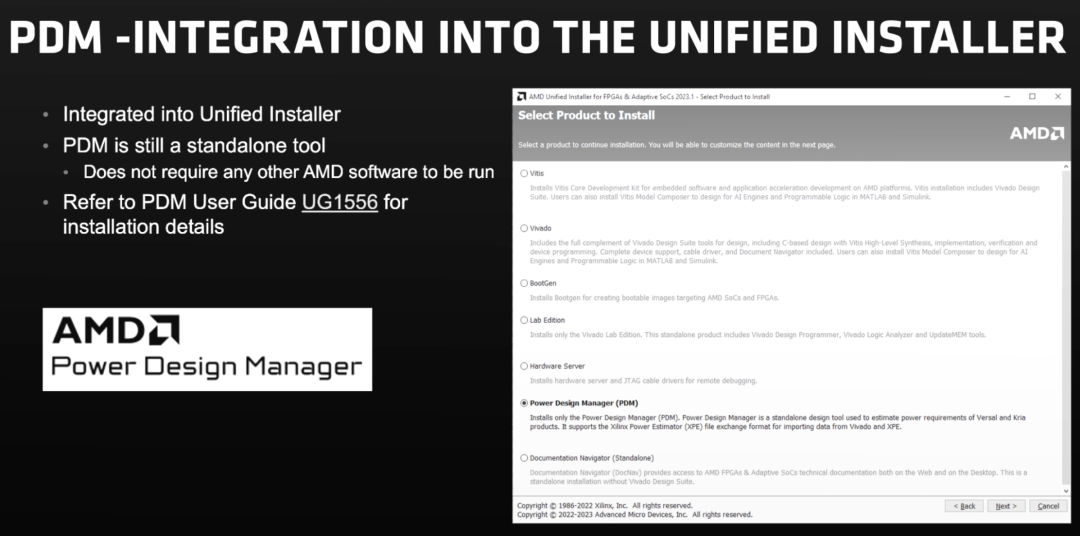

PDM 已经与其它 AMD FPGA 和自适应 SoC 工具一起集成到统一的安装程序中。这是一款独立的工具,无需任何额外的 AMD 软件,即可运行或完成安装。

如需了解有关安装以及其它相关的详细信息,请参阅 PDM 用户指南 UG1556:

https://docs.xilinx.com/r/en-US/ug1556-power-design-manager

PDM 23.1 目前可支持 Versal HBM 系列中的所有器件。使用 PDM 中的导入 XPE 功能,HBM Xilinx Power Estimator (XPE) 的用户可以迁移到 PDM。除了迁移流程之外,PDM 23.1 还支持使用 HBMMC 向导对HBM 堆栈进行设置。该向导位于 PDM 的 NoC TDRMC HBM 部分,并可在使用期间随时进行访问。向导将根据其包含的所选字段来设置所有必需参数以及 NoC 路径。为了准确配置 NoC,强烈建议您使用 Vivado™ 中的 NoC_compiler.xpe

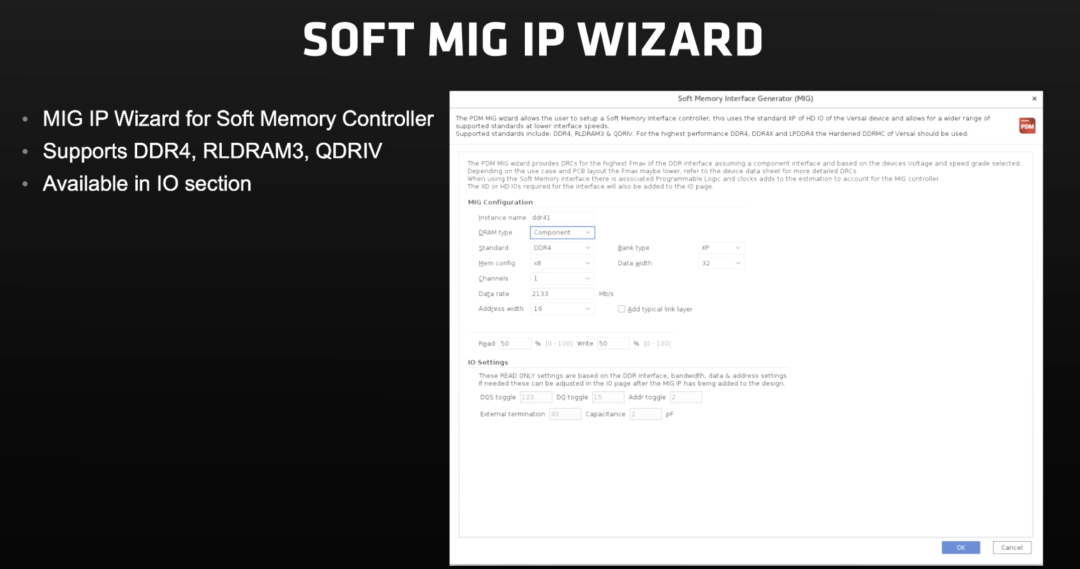

内存接口生成器向导现在也可用于在器件的可编程逻辑部分设置软内存控制器。此向导将帮助您根据所选配置来设置相关逻辑、时钟和 IO 详细信息。目前可支持 DDR4、RLDRAM 3 和 QDRIV 内存标准。此外,MIG 向导位于 PDM 的 IO 部分。

从 PDM 23.1 开始,我们启用了电源管理控制面板的初始版本。这个部分可用来探索各种 PL 功耗管理技术,如时钟门控、频率缩放和逻辑门控,以及通过实现这些技术可能带来的各种功耗节省。

这里的功耗估计值是评估表中的功耗的缩放版本,因此与所列出的功耗模型特性相比,可能会有一些差异。这些可用于评估在运行时功耗管理期间可能实现的功耗降低。除此之外,如果动态功耗节省导致结温 (TJ) 降低,进而降低静态功耗,则可能会出现额外的功耗节省,在上图中表内并未对此进行建模。

请注意,此页面仅用于假设分析,对此处变量的任何更改都不会改变或重新运行主评估页面中的任何向导或设置。更多功能将会在以后的版本中陆续添加。

PDM GUI 的外观通过为选项卡视图添加全新的逻辑布局得到了增强。这个部分下面的子模块被拆分成多个选项卡,以方便查看、访问和浏览。熟悉 Vivado 的用户会注意到,这与 Vivado 中清晰可见的 IP GUI 选项卡十分相似。

“重置为默认值”功能是一项新特性,它可将路径窗口中除路径设置以外的所有用户设置进行清除,并恢复为默认设置。这与可用的 XPE 特性非常相似。此选项位于摘要部分。

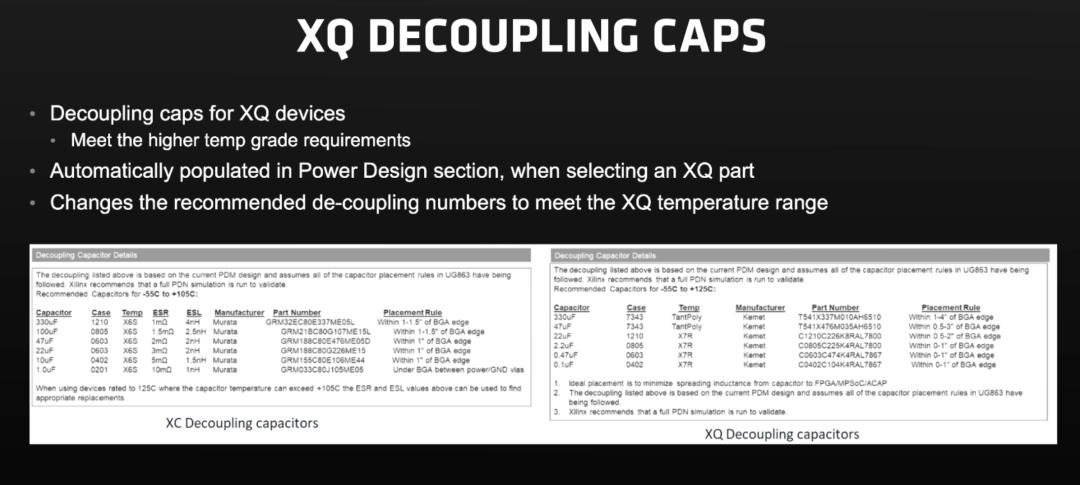

XQ 级器件对于温度规范的要求要高于 XE 级器件。PDM 电源设计部分的去耦指南已进行更新,这些电容器能够符合更高的温度规范。只要选择了 XE 器件,这些详细信息就会自动填充,因此不需要用户手动输入。

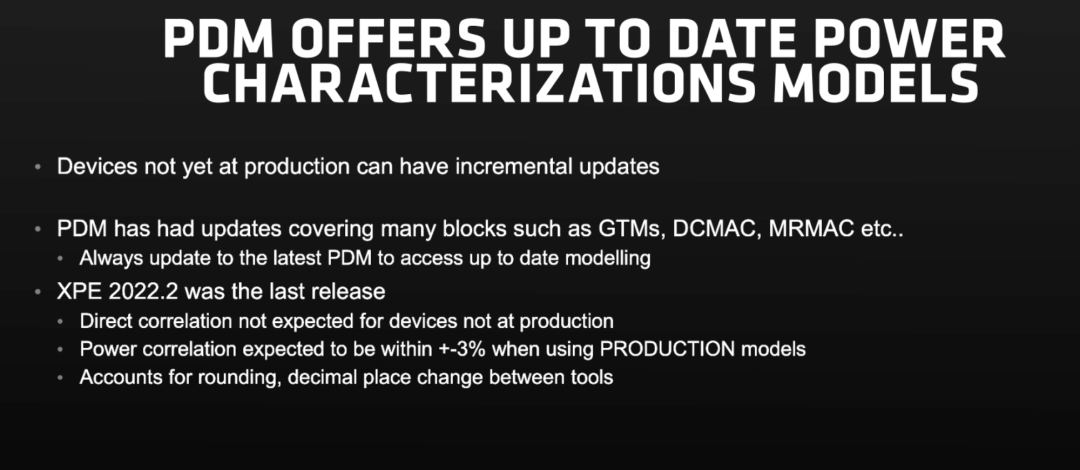

PDM 提供最新的功耗特性模型,所以任何尚未投产的器件都可能有一些增量更新。PDM 已经更新了 GTM、DCMAC 和 MRMAC 等多个硬核,为了获得最新的建模,建议您更新到最新的 PDM。XPE 2022.2 是 XPE 的最新版本,因此对于尚未投产的器件来说,预计不会存在直接的相关性。当使用生产模型时,功耗相关性预计为正负 3%。这是对不同工具之间的小数点变化进行四舍五入计算后的结果。

您可点击阅读原文查看讲解视频,如需了解更多信息,请访问:https://china.xilinx.com/pdm

文章来源: XILINX开发者社区