作者:Yang Iris,AMD工程师,来源:AMD Xilinx开发者社区

本博客将介绍如何通过CPM、NOC和LPD访问OCM。

片上存储器 (OCM)是一个在FPGA 内部包含 256 KB 的存储器,可通过其128位AXI 进行访问 接口端口。 OCM 可通过LPD的OCM 开关访问,其中包括两个 Cortex-R5F处理器和其他可以用于访问的OCM 的开关。下面的图展示了CPM 和PS 的内部连接,其中从PRU到OCM的访问,具有最高优先级, 具体路径可以参看下图。

如果用户需要通过PCIE接口访问OCM,一个推荐的数据路径可以经过CPM-NOC-PMC。您需要通过设置正确的“PCIE2AXI 地址转换” 来确保访问正确的地址。

该图的顶层如下所示。

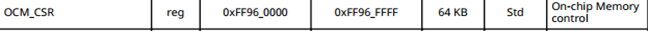

下面的表格是OCM 的地址。这些地址可以 通过NOC 访问。

在CPM 的图形界面中,请启用BAR2(AXI master)并将Pcie 2 AXI地址转换设置为fffc0000(与am011中的表147一致),将BAR的大小设置为256KB,将数据方向(Steering)设置为CPM到NOC0

注意你用PCIe 访问FPGA 的时候 首先要保证数据是集中BAR2的。方法是首先利用lspci 来读取BAR2 的基地址保证PCIE上的地址是在BAR2+SIZE 范围内。然后再通过PCIE2AXI 来计算偏移地址,如果偏移地址在OCM 的地址范围内,这个地址才能被OCM 接收。

下图是一个具体的例子:

在地址编辑器中,确保您已将正确的 OCM 地址设置为 FFFC0000,具体可以参考am011 或者下面的表格。

当FPGA 收到一个BAR2+偏移量的地址的时候 比如是bar2+1234, 那么这个地址就会通过cpm 变成FFFC1234,这个地址经过NOC 后 就能访问OCM (OCM 在下面的地址范围是FFFC0000 到FFFC0000+256k)。