作者:Denis Tramarin,AMD工程师;来源:AMD Xilinx开发者社区

本文档提供了有关 SelectMAP 启动设置的技巧和指南。在提交个案服务请求之前,应认真查看以下检查表。

SelectMAP 启动模式的常规检查表:

1. 是否已查看 SelectMAP 文档,了解连接和电源轨的用法?

- 请参阅相应的 Versal DC 和 AC 数据手册,了解电源轨和 SelectMAP 接口规格,并确保满足这些规格

- 请参阅 Xilinx Power Estimator (XPE) 或电源设计管理器 (PDM) 电源轨排序(Xilinx Power Estimator (XPE) 或电源设计管理器 (PDM))指南,并确保遵循这些指南

- 请参阅《Versal PCB 用户指南》(UG863) 的电源轨、专用管脚和 SelectMAP 章节,了解有关开发板初始化的信号连接指南 (https://docs.xilinx.com/r/zh_CN/ug863-versal-pcb-design)

- 请查看 XTP546 Versal 板级原理图检查表,了解 SelectMAP 和电源轨

- 请查看 AM011 SelectMAP 接口信息和 MIO 信号的使用方式 简介 • Versal 自适应 SoC 技术参考手册 (AM011) • 阅读器 • 文档门户 (xilinx.com)

- 请查看 UG1304 https://docs.xilinx.com/r/zh_CN/ug1304-versal-acap-ssdg 以获取常规启动流程参考资料

- 请查看《MIO 封装用户指南》,了解特定封装管脚的使用方式 https://docs.xilinx.com/r/zh_CN/am013-versal-pkg-pinout

2. 通过上电释放 POR_B 之前,REF_CLK 是否稳定且正在运行?

注:对于 SSIT 器件,需要连接 2 个 REF_CLK 专用管脚。

3. Versal 自适应 SoC 启动模式管脚是否设置为 SelectMAP MODE[3:0] = 1010?

4. JTAG 的启动模式选项设置是否也可用于开发板初始化/调试?

注:建议在所有开发板上使用 JTAG 启动模式选项。选择 JTAG 启动模式选项可防止在调试期间出现长时间超时(即,如果 SelectMAP 数据接口无法正常工作,则可能需要等待 30 分钟的超时周期,然后才能在不更改模式管脚的情况下尝试加载 JTAG PDI。)

如果无法物理更改启动模式管脚,并且想要在 SelectMAP 启动失败后加载 PDI,请按以下顺序执行操作:

- 以 SelectMAP 启动模式启动

- 等待 30 分钟超时周期

- 运行此 XSCT 脚本,以强制使用 JTAG 启动模式并发出 SRST。

versal_change_boot_mode.tcl ==============================

tar -set -filter {name =~ "Versal *"}

# Enable ISO

mwr -force 0xf1120000 0xffbff

# Switch boot mode

mwr 0xf1260200 0x0100

mrd 0xf1260200

# Set MULTIBOOT address to 0

mwr -force 0xF1110004 0x0

# Perform reset

tar -set -filter {name =~ "PMC"}

rst

=================================================

- 通过 JTAG 加载 PDI

软件流程 SelectMAP 检查表:

为 SelectMAP 启动模式生成 PDI 时,请确保已按以下步骤进行核对:

1. 确认已选择适当的 CIPS 设置以确保 SelectMAP MIO 功能正常

2. 确认正确设置了 BIF 文件属性,以确保 SelectMAP PDI 头文件设置正确且功能正常

. 在运行 Bootgen 以生成 PDI 之前,确认这些设置都正确无误

. 对于 SelectMAP,x32 为默认设置,不需要更改 BIF 文件。

. 对于 2022.1 或更低版本,使用 SelectMAP x8 和 x16 时,用户必须在运行 Bootgen 之前手动包含 BIF 属性,如下所示。

. 注:对于 SSIT 器件,请参阅下一个检查表项目以了解差异

对于 SelectMAP x8

new_bif:

{

id_code = 0x04d80093

extended_id_code = 0x01

id = 0x2

boot_config{smap_width=8}

image

{

name = pmc_subsys

id = 0x1c000001

…

Or for Select x16

new_bif:

{

id_code = 0x04d80093

extended_id_code = 0x01

id = 0x2

boot_config{smap_width=16}

image

{

name = pmc_subsys

id = 0x1c000001

注:在 2022.2 版中,当用户在“CIPS Peripheral IO”选项卡中选择 SelectMAP x8 或 x16 时,上述属性将自动写入 BIF 文件中。

. 在 Versal SSIT 器件的 BIF 文件中,用户将在 bitstream_master 节中看到目标 smap_width,在从 SLR 节中看到 smap_width=0。

. smap_width=0 用于表明从 SLR 设置模式,不得修改。如欲了解详细信息,请参阅相应软件版本的 UG1283。

BIF 文件中有关 SSIT 器件的设置示例

// For generating SLR1 – boot PDI

bitstream_boot_1:

{

id_code = 0x04d10093

extended_id_code = 0x01

id = 0xb

// Do NOT change setting shown on SSIT Slave SLRs

boot_config {smap_width=0}

image

{

name = pmc_subsys, id = 0x1c000001

partition { id = 0xb01, type = bootloader, file = gen_files/plm.elf }

partition { id = 0xb0A, type = pmcdata, load = 0xf2000000, file = gen_files/pmc_data_slr_1.cdo }

…

// For generating final PDI – by combining above generated PDIs.

bitstream_master:

{

id_code = 0x04d10093

extended_id_code = 0x01

id = 0x2

// Add attribute for SelectMAP 8-bit (smap_width=8) and 16-bit (smap_width=16) under the "bitstream_master" section of BIF file

boot_config{smap_width=8)

image

{

name = pmc_subsys, id = 0x1c000001

SelectMAP 写入数据加载顺序示例:

1. 上电(确保电源轨处于稳定状态并根据 Xilinx Power Estimator 或电源设计管理器指南进行排序)

2. Versal REF_CLK 专用管脚处于稳定状态

3. 启动模式专用管脚设置为 SelectMAP (MODE[3:0]=1010)

4. SMAP_RDWR_b=0 表示写入模式

5. POR_B 已释放

6. SMAP_CLK 时钟设置处于稳定状态

7. SMAP_BUSY 在准备好接受数据时将变为低电平

8. SMAP_CS_b 已由主机设置,用于启动使能器件并在 SMAP_CLK 的上升沿计时

9. SMAP_IO 主机开始发送 PDI 数据。SMAP_IO 在 SMAP_CLK 的上升沿计时

10. 在加载 PDI 数据期间,监视 SMAP_BUSY 断言情况

. 当 SMAP_BUSY=1 断言有效时,确保 SMAP_CS_b 在 24 个 SMAP_CLK 周期内断言无效 (SMAP_CS_b=1)

. 当 SMAP_BUSY=0 断言无效时,断言 SMAP_CS_b=0 有效以继续加载 PDI 数据

11.在最后一项 PDI 数据计时后确认以下内容:

. SMAP_CS_b 已断言无效

. 在最后一项 PDI 数据之后至少发出 24 个 SMAP_CLK 周期,以确保 DONE 变为高电平

Versal SelectMAP 32 位数据加载波形图:

1. SelectMAP 数据加载波形图显示了初始数据周期内的 PDI 启动头文件 - 16 字节总线检测模式。

2. Versal 自适应 SoC 在写入模式下发现 RDWR_B=0 后,将断言 BUSY=0 无效。大多数应用只需加载(写入)SelectMAP 数据,并且可以保留 RDWR_B=0。

3. 发出最后一项 PDI 数据后,设置 CS_B=1 并发送至少 24 个 SMAP_CLK 周期,以确保 DONE 信号变为高电平。

Versal SelectMAP PDI 16 字节总线检测模式顺序:

Versal SelectMAP 多器件接口示例:

大多数应用都在写入模式下使用 Versal SelectMAP 启动模式。对于不以读取操作为目标的应用,建议将 SMAP_RDWR_b 保持在写入模式 (SMAP_RDWR_b=0)。

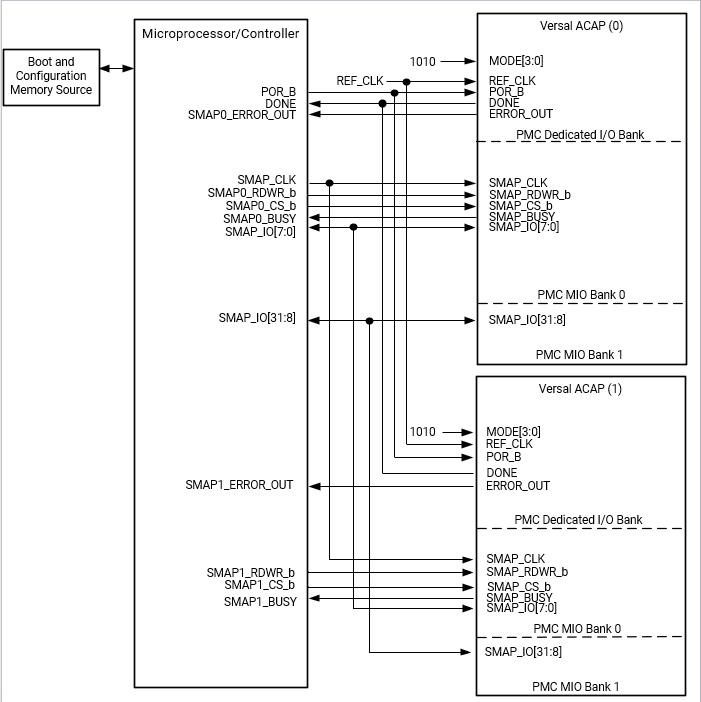

下面显示了两种 Versal 多器件设置示例。第一个示例显示的控制信号可在上电时或使用相同的 REF_CLK 源时连接在一起。第二个示例表明每个器件的信号都是唯一的,以保证更大的灵活性。

这两种设置都显示了唯一的 SMAP_RDWR_B,这样可防止在不太常见的读取模式用例中出现任何信号争用情况。使用读取模式 (SMAP_RDWR_b=1) 时,无论 SMAP_CS_b 设置如何,数据 I/O 都不会为三态。对于多器件设置,在读取模式下以某个器件为目标时,不属于读取操作目标的器件应保持在写入模式 (SMAP_RDWR_b=0) 下且 SMAP_CS_b=1。

示例 1.

示例 2.