作者:Florentw,AMD工程师;来源:AMD开发者社区

简介

在上一篇 AI 引擎系列博文 中,我们演示了 Vitis 完整系统示例,其中包含一个 AI 引擎应用。

在这篇新博文中,我们将构建系统、分析生成的输出并在硬件仿真中使用 QEMU 运行系统。

AI 引擎应用构建

首先打开上一篇博文中创建的 Vitis 工作空间。

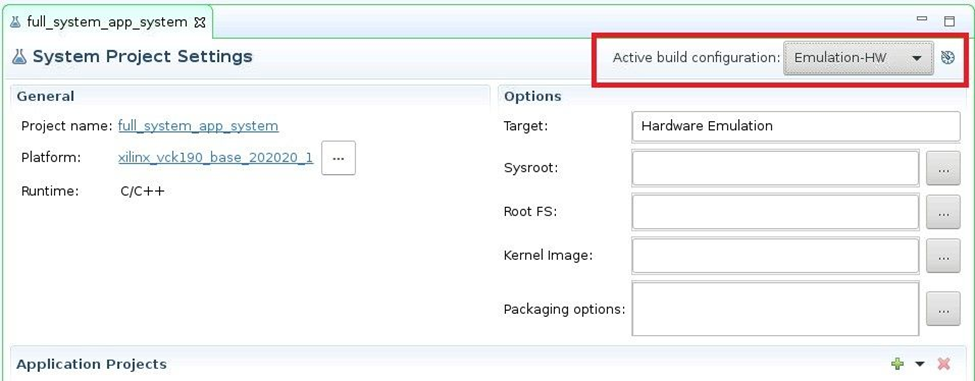

为确保系统配置已将系统构建目标设为硬件仿真,请打开 full_system_app_system.sprj 配置文件,检查当前处于活动状态的构建配置是否已设置为“Emulation-HW”(硬件仿真)。

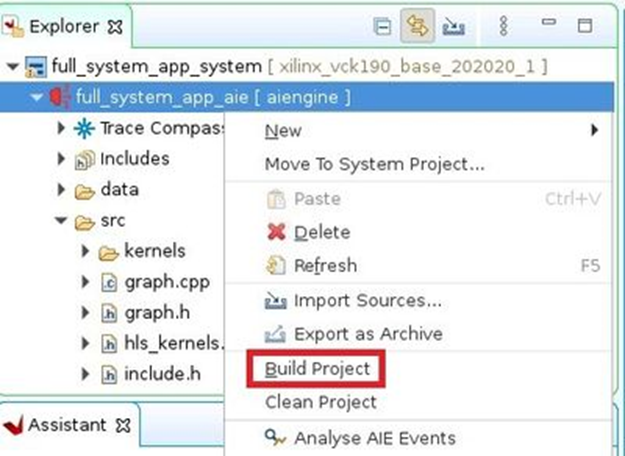

要构建 AI 引擎应用,请右键单击 full_system_app_aie 应用工程,然后单击“Build Project”(构建工程)。

通过观察控制台窗口,可以看到其中已运行下列命令:

aiecompiler -v -Xchess=main:darts.xargs=-nb -include="

这是用于为硬件仿真构建 AI 引擎应用的基本命令。在 AI 引擎系列 5 一文 中,我们已讲解过各项选项。

构建完成后,请双击 Vitis 分析器汇总文件 (full_sysetem_app_aie/Emulation-AIE/Work/graph.aiecompile_summary) 将其打开。

在“graph”(计算图)选项卡中可以看到计算图视图:

可以看到 2 内核(interpolator 和 classify)以白色方块来表示,在 2 个不同拼块的阵列中实现了 1 个蓝色闪电符号。此外,还可以看到从计算图到 PL 的连接和从 PL 到计算图的连接。

PL 内核构建

下一步是构建 C/C++ 内核,这些内核将在可编程逻辑 (PL) 内实现,并连接到 AI 引擎计算图。

注 1:在此系统中,所有 C/C++ 内核都连接到 AI 引擎阵列。但这并非铁则。内核只是在 PL 中加速(即,实现)的函数,因此内核可能与 AI 引擎无连接。

注 2:在这些示例中,AI 引擎使用内核连接到 PL。但这并非要求。平台中存在的 AXI4-Stream 接口可以直接连接到 AI 引擎(请参阅本示例)或者可使用 GMIO 接口将 AI 引擎连接到 NoC。

要构建 PL 内核,请右键单击 full_system_app_kernels 应用,然后单击“Build Project”(构建工程)。

观察控制台即可看到其中已运行下列命令:

v++ --package --config package.cfg ../../full_system_app_aie/Emulation-AIE/libadf.a ../../full_system_app_system_hw_link/Emulation-HW/binary_container_1.xclbin -o binary_container_1.xclbin

可以看到,其中使用了 v++ 工具来编译内核,并且编译输出为 XO 文件。如需了解有关使用 v++ 命令编译 C/C++ 内核的更多详细信息,

请参阅 Vitis 文档。

每个内核生成 1 个 XO 文件,其中内核编译结果如下所示:

硬件连接构建

下一步是将 PL 内核与 AI 引擎集成到硬件平台中。这个步骤称为系统硬件连接。

要运行硬件连接构建,请右键单击 full_system_app_system_hw_link,然后单击“Build Project”(构建工程)。

注:此步骤会在后台调用 Vivado,因此您将需要有效的许可证才能运行综合与实现并为 Versal 器件生成比特流。

观察控制台即可看到其中已运行下列命令:

v++ --target hw_emu --link --config binary_container_1-link.cfg -o"binary_container_1.xclbin" ../.. /full_system_app_kernels/Emulation-HW/build/mm2s.xo ../../full_system_app_kernels/Emulation-HW/build/polar_clip. xo ../../full_system_app_kernels/Emulation-HW/build/s2mm.xo ../../full_system_app_aie/Emulation-AIE/libadf.a

我们可以看到,v++ 工具搭配 --link 选项使用,并以已编译的内核(mm2s.xo、polar_clip.xo 和 s2mm.xo)和已编译的 aie 应用 (libadf.a) 作为输入。此步骤将使用 Vivado 生成 XCLBIN 文件。

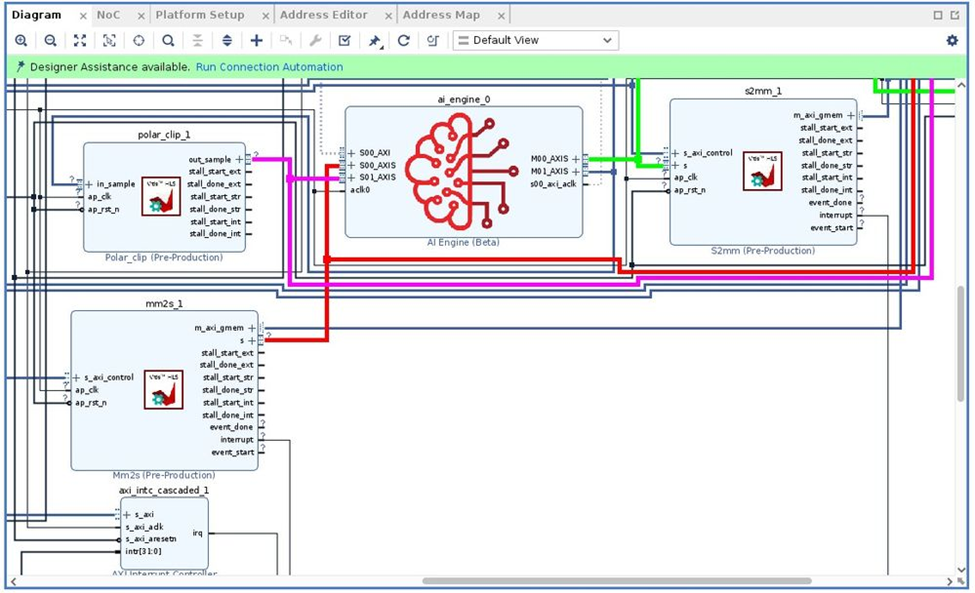

成功构建应用后,可以看到用于在 Vivado 中生成 XCLBIN 的设计。

在以下目录中应包含名为 prj.xpr 的 Vivado 工程:

在 Vivado 2021.1 中,打开 prj.xpr 工程中的块设计 xilinx_vck190_base 后,即可看到 MM2S、S2MM 和 polar_clip 内核均已作为 IP 块添加并连接到 AI 引擎的 AXI4-Stream 接口。

PS 应用构建

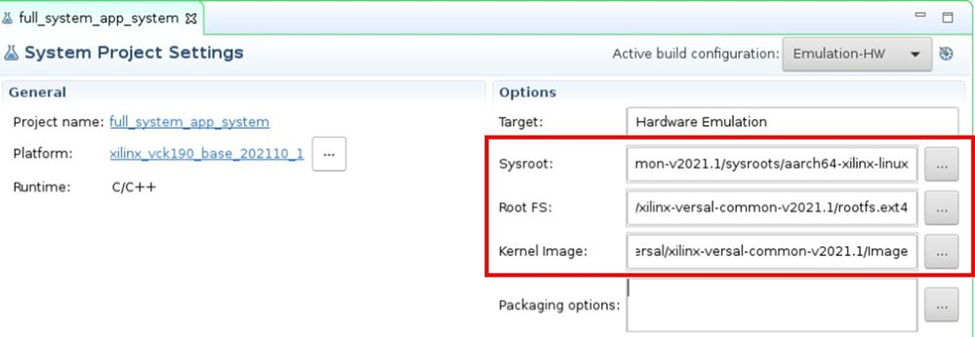

下一步是为 Linux 系统构建应用。要成功构建应用,Vitis 要求设置下列选项:sysroot、根文件系统与内核镜像的路径。

为此,可以使用预构建的 Linux 内核与根文件系统,这两者可搭配任意 Versal 开发板一起使用。可从以下页面下载(Versal 通用 tarball):

https://china.xilinx.com/support/download/index.html/content/xilinx/zh/d...

下载 Versal 通用文件后,需使用 Linux 终端从解压的文件夹内运行以下脚本来构建 sysroot:

xilinx-versal-common-v2020.2/sdk.sh -y -dir

构建 sysroot 后,在 Vitis IDE 中打开 full_system_app_system.sprj 配置文件,设置 sysroot、根文件系统和内核镜像的路径。

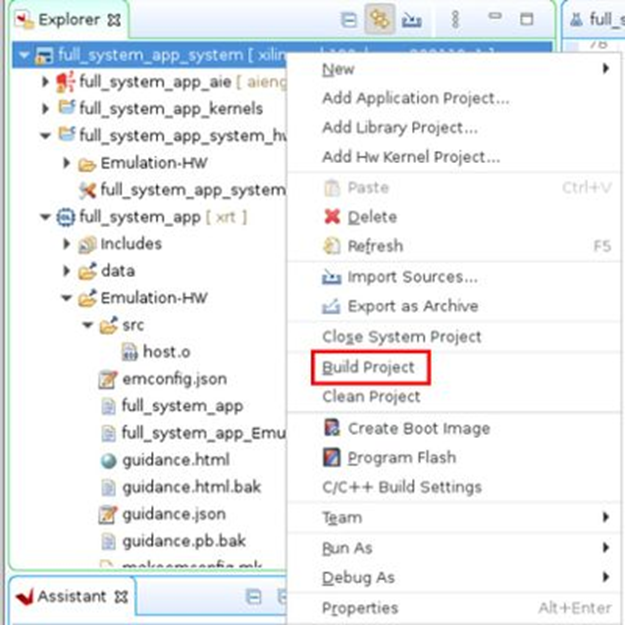

现在就能构建 PS 应用了,方法是右键单击 application full_system_app[xrt],然后单击“Build Project”

这将在 full_system_app/Emulation-HW 下生成名为 full_system_app 的二进制文件。

系统封装

最后一步是封装系统。该步骤将创建启动镜像。

选中 full_system_app_system,单击“Build Project”。

注:如果未按前文所述逐个完成构建 AIE 应用、PS 应用或内核的步骤,或者未连接系统,那么构建完整系统还会一并完成这些步骤。

在控制台中可以看到,其中已执行下列命令:

v++ --package --config package.cfg ../../full_system_app_aie/Emulation-AIE/libadf.a ../../full_system_app_system_hw_link/Emulation-HW/binary_container_1.xclbin -o binary_container_1.xclbin

从中可以看到调用 v++ 工具时还会搭配 --package 选项以及硬件连接期间创建的 XCLBIN 文件与已编译的 AIE 应用 (libadf.a)。

package.cfg 文件包含适用于 v++ 命令的其他选项,包括已编译的 PS 应用 (full_system_app)

在硬件仿真中运行系统

最后一步是在硬件仿真中测试系统。

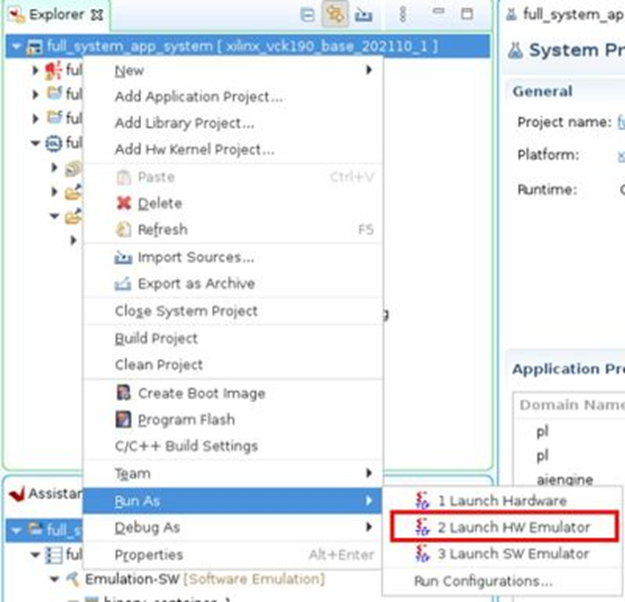

要为系统启动硬件仿真,请右键单击 full_system_app_system,然后单击“Run As...> Launch HW Emulator”(运行方式 > 启动硬件仿真器)

这样会弹出一个窗口,询问是否要使用 GUI 模式。虽然 GUI 模式可用于查看进出 AI 引擎的信号,但本文不涉及这部分内容(后续博文中再来详谈这部分)。

保留不选中“Launch Emulator in GUI mode to display waveforms”(以 GUI 模式启动仿真器以显示波形)选项,然后单击“Start Emulator and Run”(启动仿真器并运行)。

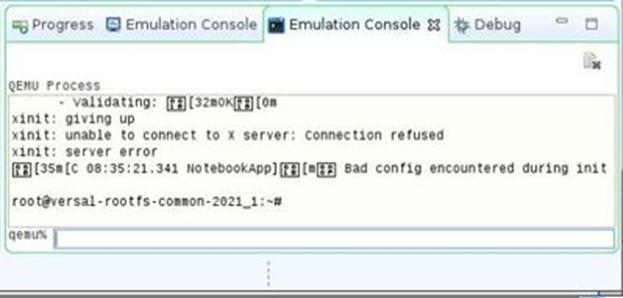

这将打开“Emulation Console”(仿真控制台)窗口,我们可在其中查看系统启动过程:

启动时,使用显示的 Linux 提示符来运行设计。

显示仿真的 Linux 提示符时,执行以下命令以设置环境:

cd /mnt/sd-mmcblk0p1

export XILINX_XRT=/usr

dmesg -n 4 && echo "Hide DRM messages..."

最后,执行以下命令以运行应用:

./full_system_app ./binary_container_1.xclbin

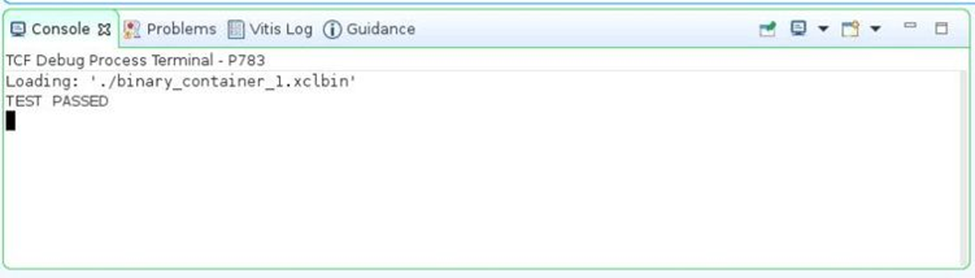

在控制台窗口中,应显示如下输出,表示应用已运行成功:

Loading: './binary_container_1.xclbin'

TEST PASSED