作者:Kathy Ren,AMD工程师;来源:AMD开发者社区

在非常多的客户应用工程中,都会用到DDR4/LPDDR4来存取大容量数据。如何设计DDR4/LPDDR4接口,布局相关管脚,并且能够在IO bank比较有限的情况下,实现多个memory controller接口就会是设计之初很重要的一个环节。

在Versal器件中,有两种DDR4/LPDDR4控制器。一种是硬核DDRMC,它是通过配置NOC IP生成;另一种则是通过软核soft DDR4 memory controller IP生成。

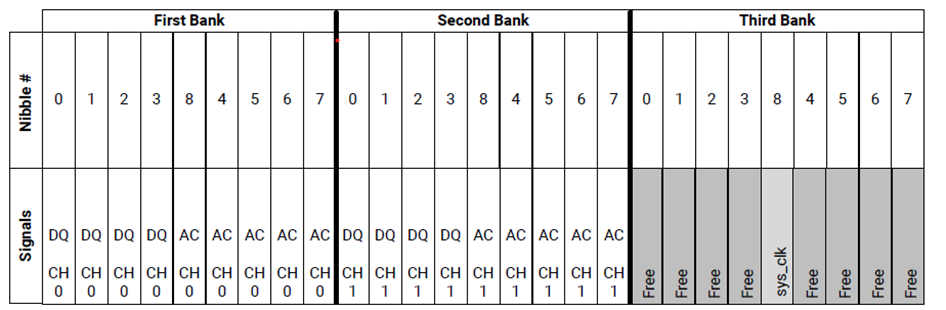

一个DDRMC相关的管脚被放置在一个triplet中,并且是固定位置的,具体的信息可以参考文档pg313 Site Search (amd.com)中“Pinouts for Supported Configurations”章节。1个NOC配置成2x16bit DDRMC的情况下,管脚如下图所示(分为Non-Flipped和Flipped两种情况)。

接下来,我们希望在第1/3个bank空余的管脚上再放置一个16bit的soft DDR4 controller。

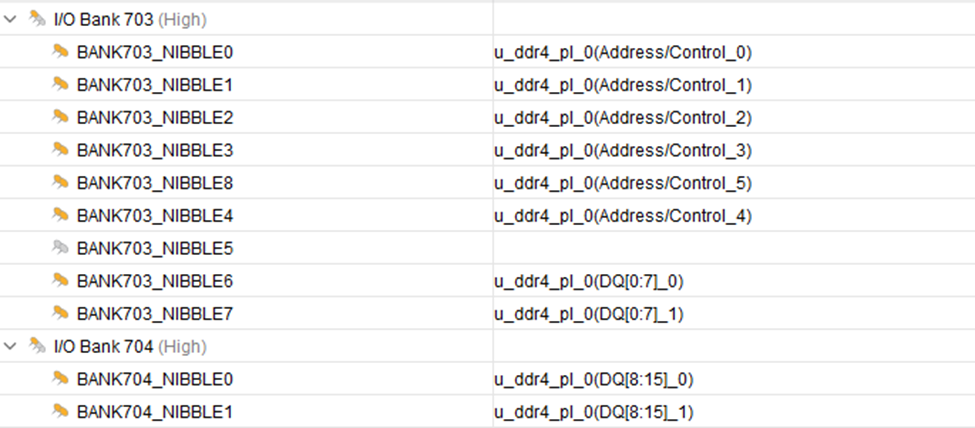

从Advanced IO Planner中,可以看到,通过工具自动布局,需要10个byte,无法放入1个bank中。

通过观察,发现16bit的soft DDR4 controller的所需要管脚总数是足够的。所以接下来,我们需要对默认的管脚位置进行一些手动调整, 并写入xdc文件。

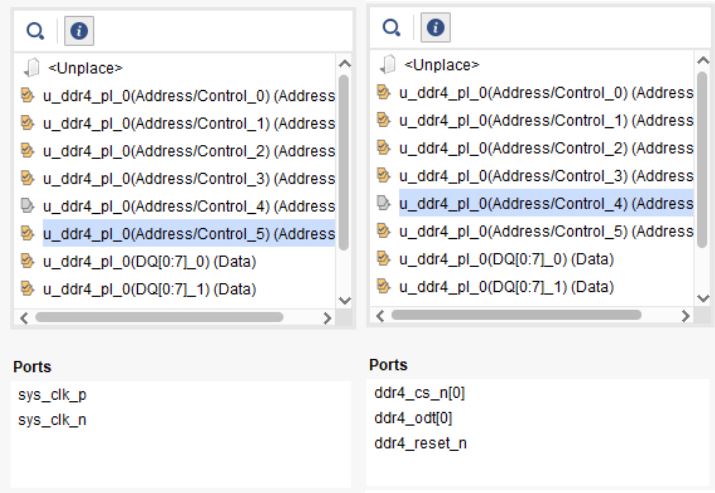

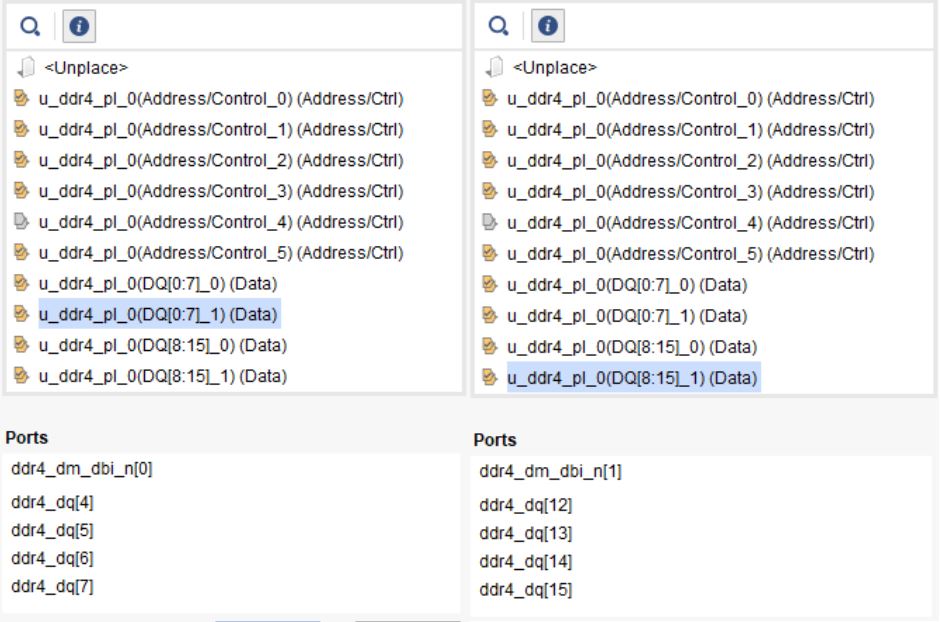

Address/Control_4中只有cs_n,odt和reset_n一共3个信号。将reset_n信号放入Address/Control_5所在的nibble 8;然后将cs_n和odt信号分别放入DQ[0:7]_1和 DQ[8:15]_1所在的nibble的空余管脚,这样就空出了整个nibble4。然后,DQ[8:15]_0和 DQ[8:15]_1两组信号就可以整体放入nibble4和nibble5中了。