作者:Ivy Guo,AMD工程师;来源:AMD开发者社区

此文针对一个MultiBoot应用案例做一些深入探讨,需要读者比较熟悉FPGA的MultiBoot设计流程。

该案例来自客户。原始问题是基于一个PROG_B管脚使用的疑问: “PROG_B管脚到底能否用于控制延迟FPGA的配置开始?我们的观测结果和文档描述不一致。” 客户的设计基于Artix-7系列器件。

在7系列之前或者之后的FPGA系列,PROG_B管脚都可以用于延迟配置的开始。这一点在对应的Configuration User Guide里面有明确描述。比如下面UG570文档(对应UltraScale系列):

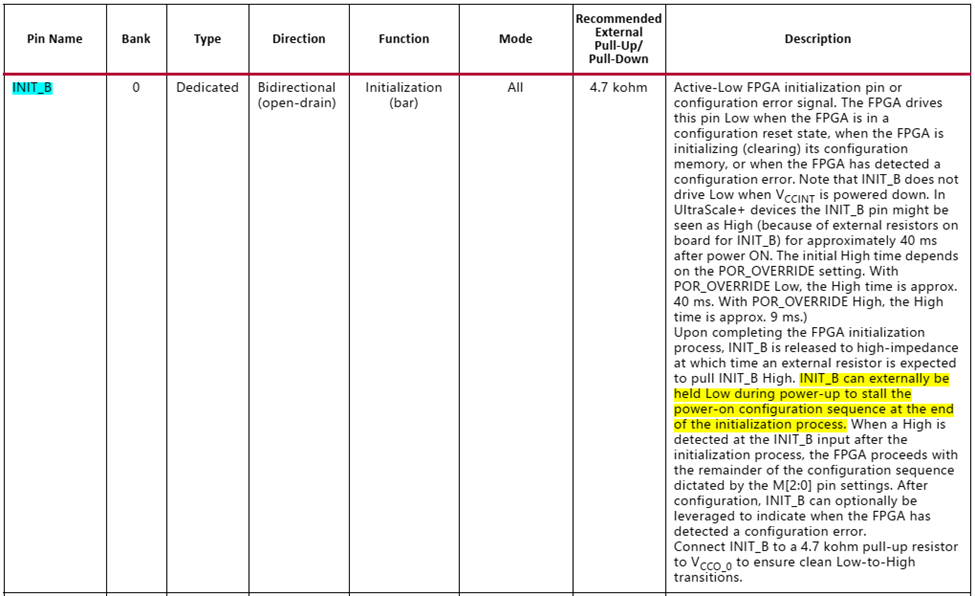

INIT_B管脚可以起到同样的作用:

但是在7系列里面,注意PROG_B管脚没有这个功能了。参考UG470说明

直接说原因:这是因为7系列的PROG_B管脚从level sensitive,改为了edge sensitive。在器件上电阶段,如果FPGA没有‘及时’看到PROG_B的下降沿,FPGA就会认为并没有出现PROG_B的有效信号,从而会开始正常的配置流程。

基于AC701开发板,我们开始测试。

先说明一下验证采用的两个简单的点灯设计:

top1:例化ICAPE2模块及MultiBoot状态机,LED灯从0->3快速闪烁后全亮循环。收到外部IPROG信号时,跳转到SPI指定地址0x40 0000。

top2: 普通点灯设计。无ICAPE2,无跳转控制。LED灯从3->0慢速闪烁后全亮循环。

第一个实验:

把top2.mcs烧写到板上的SPI Flash N25Q256。在板子上电前就按住SW9(PROG_B按钮),可以看到代表配置完成的DONE管脚LED正常亮起来了,4个User LED灯也按照预期闪烁。说明FPGA没有看到PROG_B的下降沿,无法阻止配置的开始。

文档没有问题。那么客户为什么声称他们观察到了不同的现象——拉低PROG_B后,配置文件并没有加载呢?讨论发现原来他们的设计是一个MultiBoot的设计:客户使用了Header + Golden + MultiBoot的组合。有关这种类型的设计,大家可以参考一下SP605的MultiBoot设计:

这里说明一下,其实Header的使用并不是Spartan-6系列特有的功能,支持MultiBoot功能的FPGA都可以在正式的配置文件前加一个Header,从而实现MultiBoot设计在上电阶段的任意跳转。

以AC701为例来说,可以把Header文件建立如下:

FFFFFFFF

AA995566 – 同步字

20000000

30020001 – 写WBSTAR寄存器

xxxxxxxx -- 这里写入上电想直接跳入的Image的配置起始地址

30008001

0000000F -- 执行IPROG命令,实现跳转

20000000

对了,这段指令就是我们在做‘普通’的MultiBoot设计的时候,一般在Golden里面发给ICAPE2的跳转指令 (UG470, Table 7-1)。这些指令完全可以直接写入Flash 0地址,在一上电就被FPGA读入,从而直接实现跳转。

不过这里暂停一下,我们先做

第二个实验:

我们再做一个普通的常见的MultiBoot设计来测试。即Golden top1 + MultiBoot top2的组合。烧写top1_2.mcs到flash。正常情况下测试结果如预期,AC701上电进入top1。等指令信号(按钮SW3.3)触发后,进入top2。

接下来我们先按住SW9按钮,然后再给AC701上电。我们会发现器件直接进入了top1(说明拉低PROG_B不起作用)。保持SW9一直未释放,然后启动IPROG指令信号(按钮SW3.3),结果发现无法跳入top2。

再次暂停讨论结果,做:

第三个实验:

客户的设计是:地址0x1 0000存储Golden Image,0x40 0000存储MultiBoot Image, Header存储在0地址,其中Header的WBSTAR中存储了地址0x40 0000,即需要实现上电直接进入MultiBoot。正常情况下测试一切如预期。但是如果拉低PROG_B信号,发现FPGA根本无法进入MultiBoot。实际上,FPGA没有进入任何一个Image,包括也没有fallback回Golden。看起来好像PROG_B的‘延迟配置’作用生效了。

仿照客户的设计,生成Header+Golden+MultiBoot的Image,即header_1_2.mcs。该mcs烧写到flash后,如正常上电启动,直接进入top2。但如果按住SW9然后给板子上电,发现FPGA确实未进入任何设计,和客户结果一致。

根本原因是:PROG_B和IPROG在这里发生了冲突。PROG_B和IPROG,起到的作用可以简单理解为几乎一致:清除FPGA的配置数据并进一步触发新的配置流程。当PROG_B在外部为拉为低电平时,相应地IPROG也无法生效了。

有了这个思路,我们再分析三个实验分别拉低PROG_B的现象:

1. SPI写入的是普通的top2.mcs,配置正常进行,DONE信号拉高;

——在7系列里,PROG_B由level sensitive改变为edge sensitive。由于启动阶段未探测到 PROG_B的下降沿,所以配置正常进行。

2. SPI写入普通常见的MultiBoot设计top1_2.mcs。上电后正常进入top1,但是在外部跳转信号发出后,无法进入top2.

——PROG_B无法阻止配置的进行,因此设计正常进入了低地址的top1。但是由于PROG_B一直保持为低电平,IPROG信号无法生效,导致向top2的跳转失败。

3. SPI 写入Header_1_2.mcs,Header中包含跳转top2的地址和IPROG指令。配置无法进行。

——一上电,FPGA就开始读取Header中的内容并准备进行向top2跳转。但是由于PROG_B持续为低电平,IPROG无法生效,因此无法进行配置。

通过该案例的深入探讨,我们知道了PROG_B是否能延迟“配置”的进行,关键还是看配置启动的具体方式和是否有其他的冲突。普通的设计,文档对于7系列PROG_B行为的描述是正确的。