AMD Versal™ AI Core 系列和 Versal AI Edge 系列旨在凭借 AI 引擎机器学习 ( ML ) 架构来提供突破性的 AI 推断加速。这些器件的设计应用范围广泛,包括用于云端动态工作负载以及超高带宽网络,同时还可提供高级安全性功能。AI 和数据科学家以及软硬件开发者均可充分利用高计算密度的优势来加速提升任何应用的性能。AI 引擎机器学习拥有先进的张量计算能力,非常适合用于高度优化的 AI 和 ML 应用。

AI 引擎机器学习器件包含二维阵列,由带有单指令流多数据流 ( SIMD ) 矢量单元的超长指令字 ( VLIW ) 处理器构成,专为计算密集型应用而高度优化,特别适用于机器学习 ( ML ) 等 AI 技术。

AI 引擎机器学习阵列支持三种级别并行度:

指令级并行度 ( ILP ):通过 VLIW 架构,允许在单个时钟周期内执行多次运算。

SIMD:通过矢量寄存器,允许并行执行多项计算。

多核:通过 AI 引擎机器学习阵列,支持并行执行多个 AI 引擎机器学习核。

指令级并行度包括 1 次标量操作、1 次移动、2 次矢量读取(加载)、1 次矢量写入(存储)和 1 条可执行的矢量指令,总计每个时钟周期达 6 路 VLIW 指令。数据级并行度是通过矢量级操作来实现的,其中每个时钟周期可执行多组数据操作。

每个 AI 引擎机器学习都包含矢量处理器和标量处理器、专用程序存储器、本地 64 KB 数据存储器、支持访问其本身和三个相邻 AI 引擎机器学习内的本地存储器。它还可访问 DMA 引擎和 AXI4 互连开关,以通过串流来与其他 AI 引擎机器学习进行通信或者与可编程逻辑 ( PL ) 或 DMA 进行通信。请参阅《Versal 自适应 SoC AIE ML 架构手册》 ( AM020 ) 以获取有关 AI 引擎机器学习阵列和接口的具体详细信息。

虽然对于 AI 引擎机器学习而言,大部分标准 C 语言代码均可编译,但代码可能需要重构才能充分利用硬件所提供的并行度。AI 引擎机器学习的优势在于,它能够在每个时钟周期内使用 2 个矢量执行乘积累加 ( MAC ) 运算、为下一项运算加载 2 个矢量、存储来自上一项运算的单个矢量,并递增一个指针或执行另一次标量运算。称为本征函数的专用函数允许您以 AI 引擎机器学习矢量处理器和标量处理器为目标,并提供多个常用矢量函数和标量函数的实现,使您能够专注于处理目标算法。AI 引擎机器学习不仅包含其矢量单元,还包含一个标量单元用于所有标准 C 语言代码程序。

AI 引擎机器学习程序使用以 C++ 编写的数据流计算图(自适应数据流计算图)规格。此规范可使用 AI 引擎编译器进行编译并执行。自适应数据流 ( ADF ) 计算图应用由多个节点和边缘组成,其中节点表示计算内核函数,边缘则表示数据连接。应用中的内核可编译为在 AI 引擎机器学习上运行,这些内核构成了 ADF 计算图规范的基础构建块。ADF 计算图属于 Kahn 进程网络,其中包含并行运行的 AI 引擎内核。AI 引擎内核在数据串流和缓冲器上执行运算。这些内核会耗用输入数据块并生成输出数据块。内核还可包含静态数据或运行时参数 ( RTP ) 实参,包括异步实参或同步实参。

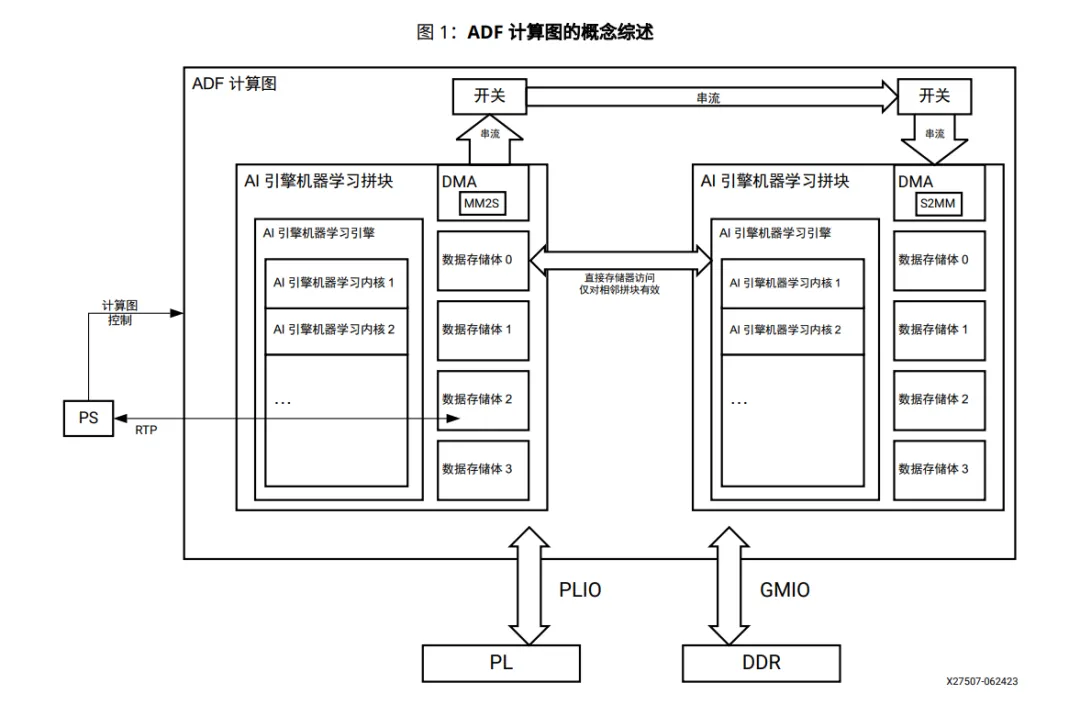

下图显示

ADF 计算图的概念视图及其与处理器系统 ( PS )、可编程逻辑 ( PL ) 和 DDR 存储器的对接接口。它包括:

AI 引擎机器学习:每个 AI 引擎机器学习都是一个 VLIW 处理器,其中包含一个标量单元、一个矢量单元、两个加载单元和一个存储单元。

AI 引擎内核:内核是以 AI 引擎机器学习中运行的 C/C++ 编写的。

ADF 计算图:ADF 计算图是具有单个或多个 AI 引擎内核(以数据串流和/或缓冲器连接)的 Kahn 进程网络。它凭借如下特定构造来与 PL、全局存储器和 PS 进行交互,此类构造有:PLIO(计算图中的端口属性,用于建立往来可编程逻辑的串流连接)、GMIO(计算图中的端口属性,用于建立往来全局存储器的外部存储器映射连接)和 RTP。

如需了解有关 AI 引擎机器学习存储器拼块访问的信息,请参阅 AI 引擎机器学习存储器拼块访问。如需了解有关 AI 引擎机器学习外部存储器访问的信息,请参阅 AI 引擎机器学习外部存储器访问。

本文档第 2 章到第 5 章聚焦 AI 引擎内核编程,不仅涉及单内核编程,还涵盖了多方面的内容,如内核之间的数据通信,这些内容都是将应用分区为多个内核以达成所需的吞吐量所必不可少的概念。

本文档第 6 到 14 章焦点包括 AI 引擎计算图编程构造、内核之间的数据通信类型、通过主机应用来控制 AI 引擎计算图以及高级计算图编程构造。

获取完整版学习阵列支持

《AI 引擎机器学习内核与计算图编程指南(UG1603)》,请扫描二维码进行下载。三种级别并行度: