本指南提供了有关 AMD Vivado™ Design Suite 中包含的 32 位和 64 位 MicroBlaze™ V 软核处理器的信息。该文档旨在用作为处理器硬件架构的指南,随附《RISC-V 指令集手册》第一卷和第二卷。

MicroBlaze V 与传统 MicroBlaze 处理器之间完全硬件兼容。

本指南包含以下章节

第 2 章:

MicroBlaze V 架构 包含处理器功能特性概述以及有关特定定制功能和高速缓存实现的信息。

第 3 章:

MicroBlaze V 信号接口描述 描述了可用于连接处理器的信号接口的类型。

附录 A:

性能和资源使用情况 包含不同配置和器件的最大频率值和资源使用率值。

附录 B:

附加资源与法律声明 提供了文档和其他资源的链接。

MicroBlaze V 架构概述

MicroBlaze V 嵌入式处理器软核是专为在 AMD 现场可编程门阵列中实现而优化的精简指令集计算机 (RISC)。下图显示了该处理器的功能模块框图。

功能特性

MicroBlaze V 软核处理器具有很高的可配置性,您可根据自己的设计需求选择特定的功能集。

该处理器固定的功能集能实现 RISC-V RV32I 基整数指令集和机器级 ISA。

. 32 个通用寄存器

. 可扩展的 32 位程序计数器

. 单发射流水线

. 算术逻辑单元 (ALU)

. 桶式移位器

. “Zicsr”控制和状态寄存器 (CSR) 指令

. “Zifencei”指令提取围栏

除这些固定功能特性外,MicroBlaze V 处理器还会通过参数化设置来允许有选择地启用附加功能。

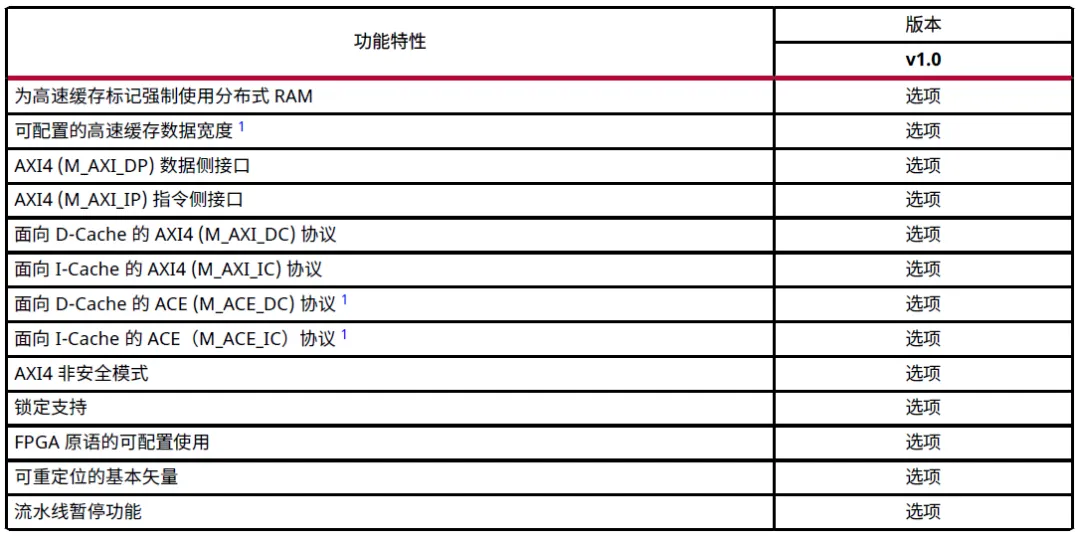

下表提供了可配置的功能特性的概述

术语

下表中简要解释了本指南中所使用的 MicroBlaze V 处理器相关的 RISC-V 术语。如需获取这些术语的完整全面的解释,请参阅《RISC-V 指令集手册》。

. Custom Instruction(定制指令):可用于供应商专用的非标准扩展的指令集类别。MicroBlaze V 定义了 GET 和PUT 定制指令,以支持 AXI4‑Stream 接口,提供与传统 MicroBlaze 的兼容性。

. Exception(异常):在运行时发生的不寻常状况,此状况与当前 RISC-V hart 中的指令相关。

. Hart:硬件线程。每个 MicroBlaze V 核仅支持一个硬件线程。

. Interrupt(中断):一种外部异步事件,可导致 RISC-V hart 遇到意外的控制传输。MicroBlaze V 支持机器外部中断、不可屏蔽中断和定制平台中断。

. Retire(停用):当一条指令执行完成时,就表示停用该指令。在 MicroBlaze V 中,当指令离开 3 阶流水线的执行 (EX) 流水线阶段,或离开其他所有流水线的写回 (WB) 流水线阶段时,就会停用该指令。

. Trap(陷阱):由异常或中断引发并以陷阱处理程序为目标的控制传输。