智多晶EDA工具HqFpga软件实用小功能增加啦,支持生成可调用网表的功能和ballmap功能。下面来给大家讲解一下如何通过HqFpga软件生成可调用的网表文件以及ballmap功能的使用。

Hq生成可调用的网表文件

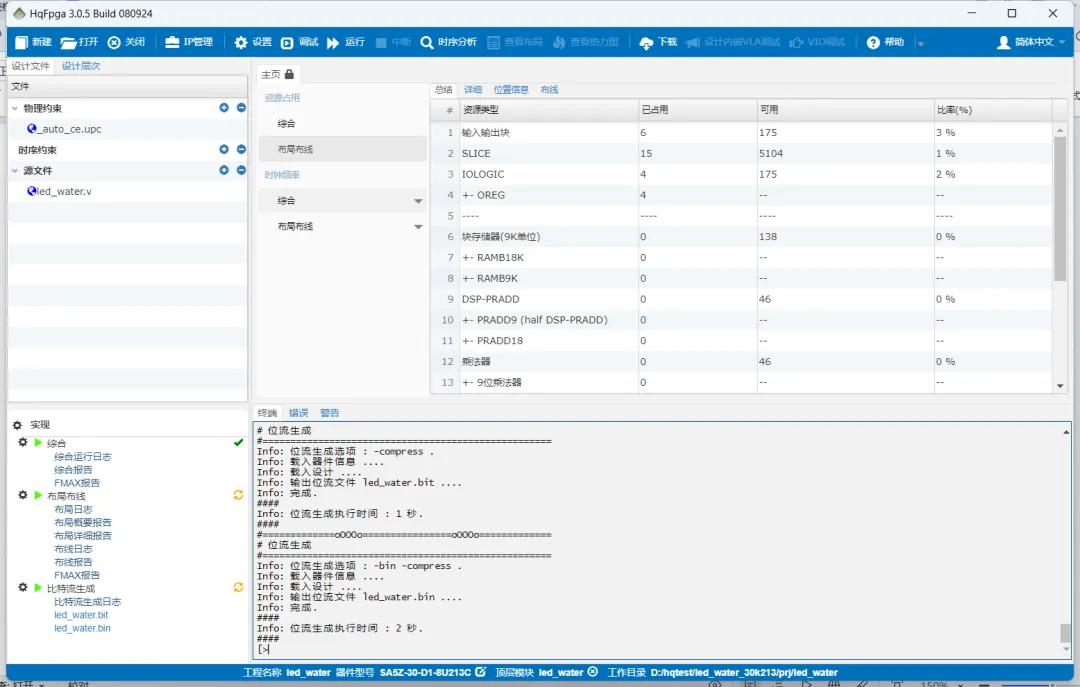

启动Hq,通过Hq工具打开工程

例如下图:

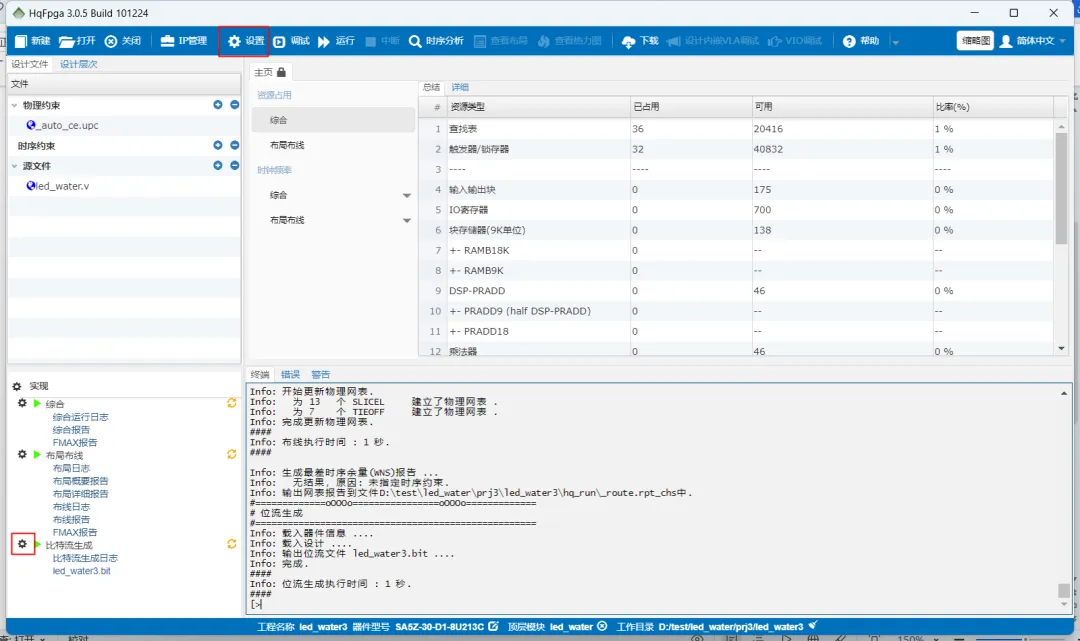

打开“配置优化选项”页面

点击设置(通过图中红色框的两个位置均可打开配置优化选项页面)。

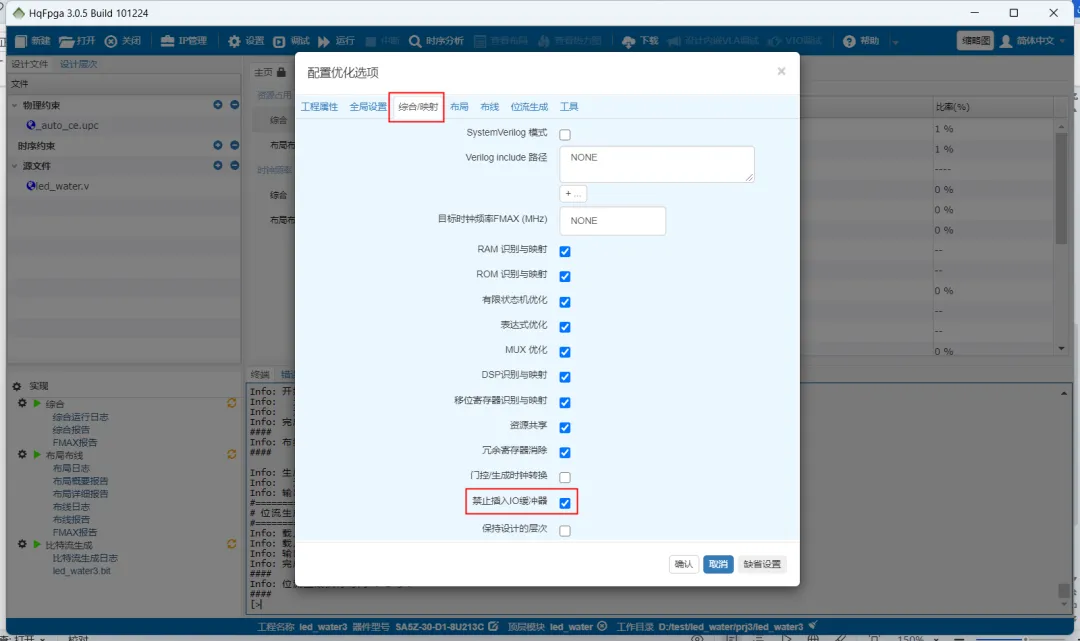

“配置优化选项”页面设置

如下图,在“配置优化选项”页面,选择“综合/映射”,然后勾选“禁止插入IO缓冲器”,最后点击“确认”。

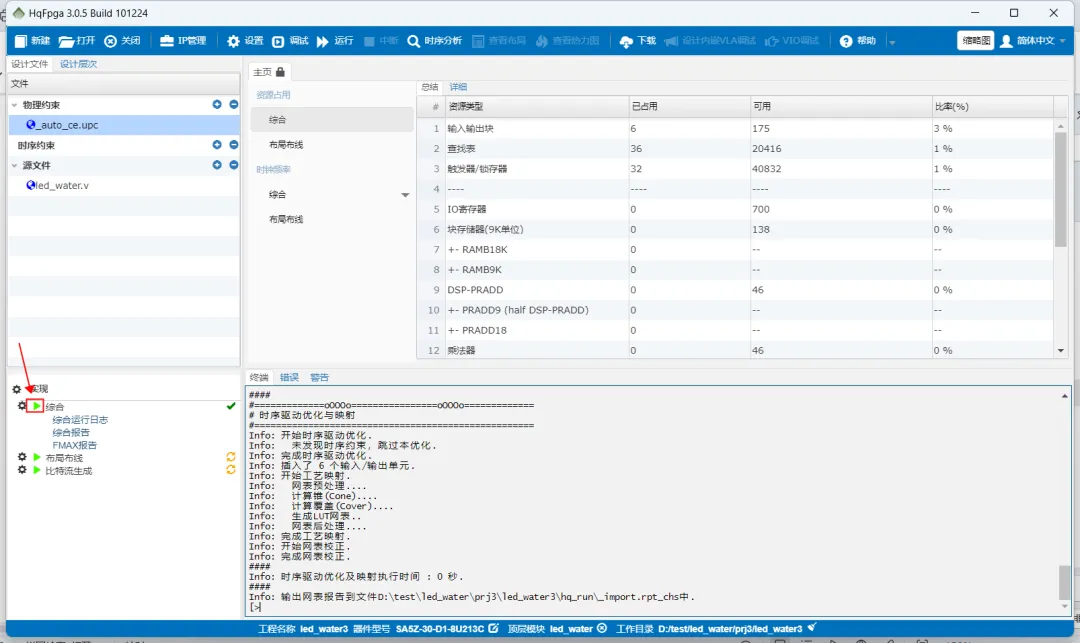

Hq综合生成“_rtl.v”网表

点击下图红色框中的综合,等待Hq运行完成,即可生成网表文件“_rtl.v”。

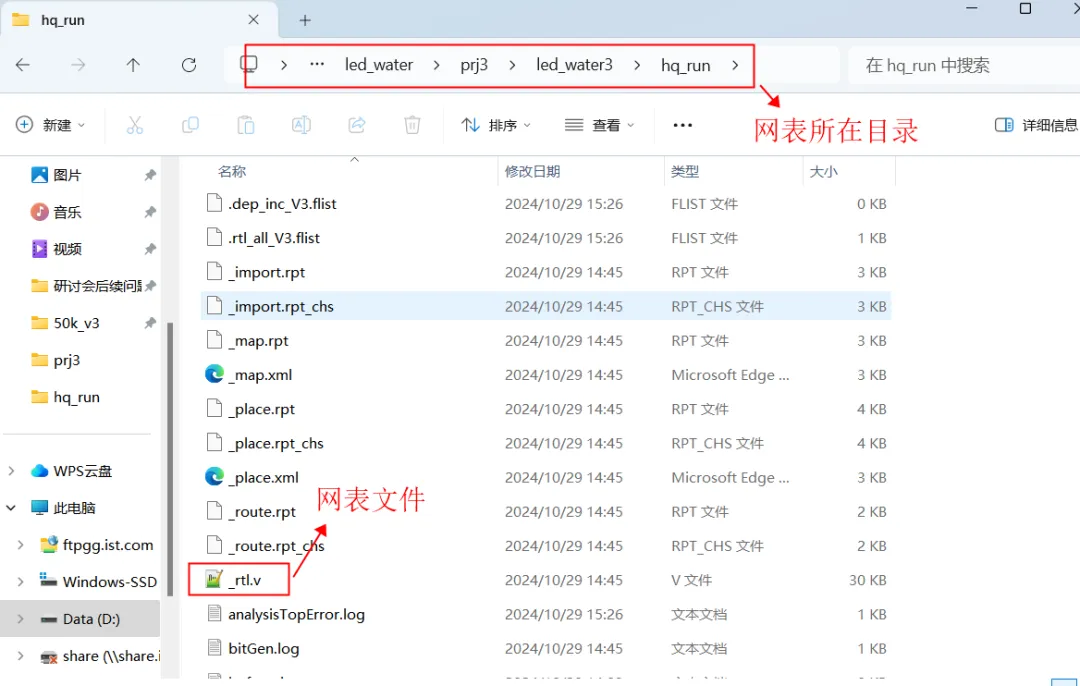

“_rtl.v”网表存放路径

在工程文件夹下,hq_run文件夹下,有一个“_rtl.v”的文件,该文件即为生成的网表文件

注:打开“_rtl.v”,搜索“IOB”,不存在“IOB”相关的模块,即生成可调用网表成功,如果能搜索到“IOB”相关的模块,即生成的网表不可直接调用。

ballmap功能的使用

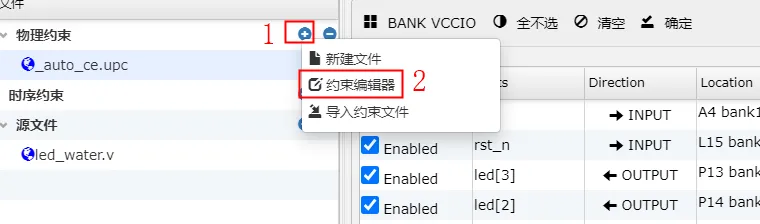

使用Hq打开UPC约束编辑器

通过Hq打开工程,在Hq打开upc约束编辑器,打开方法如下:

ballmap入口

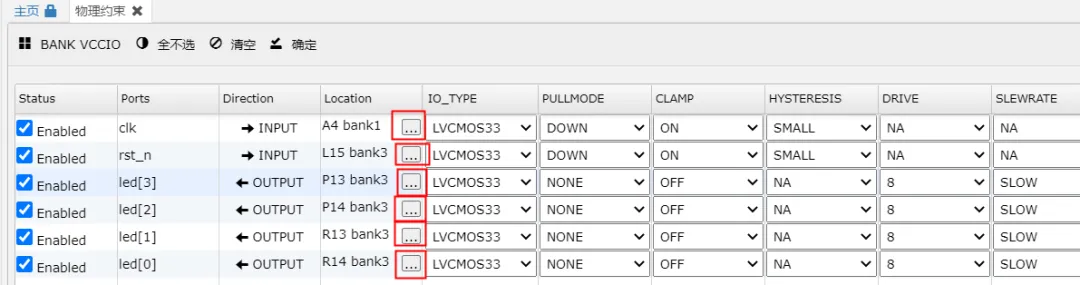

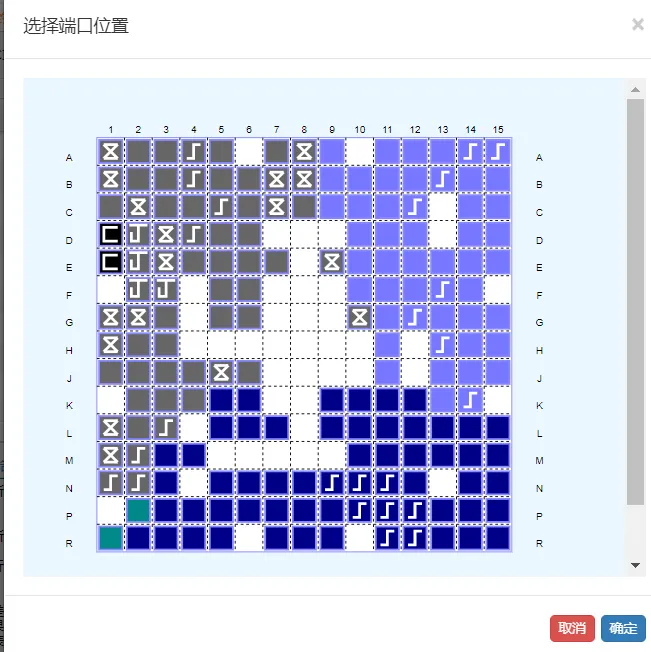

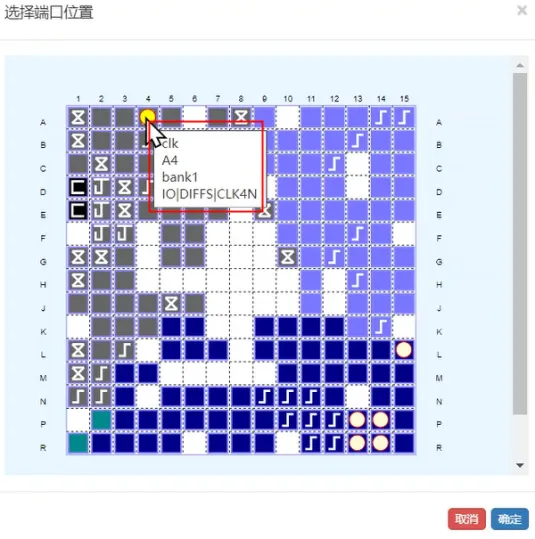

在约束编辑器里面,Location那一列,每个引脚旁边都有一个下图中的图标,点击,即可进入ballmap页面。

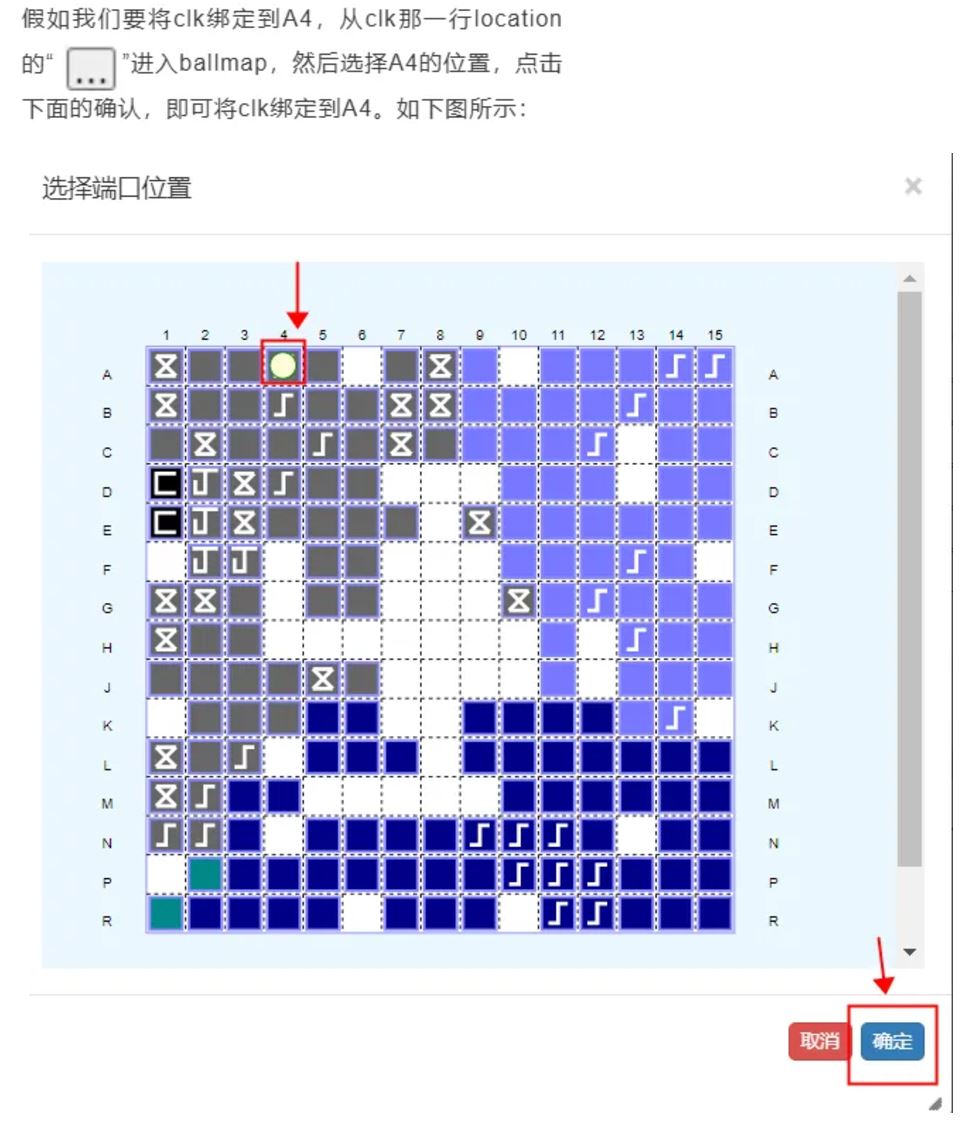

通过ballmap进行引脚绑定

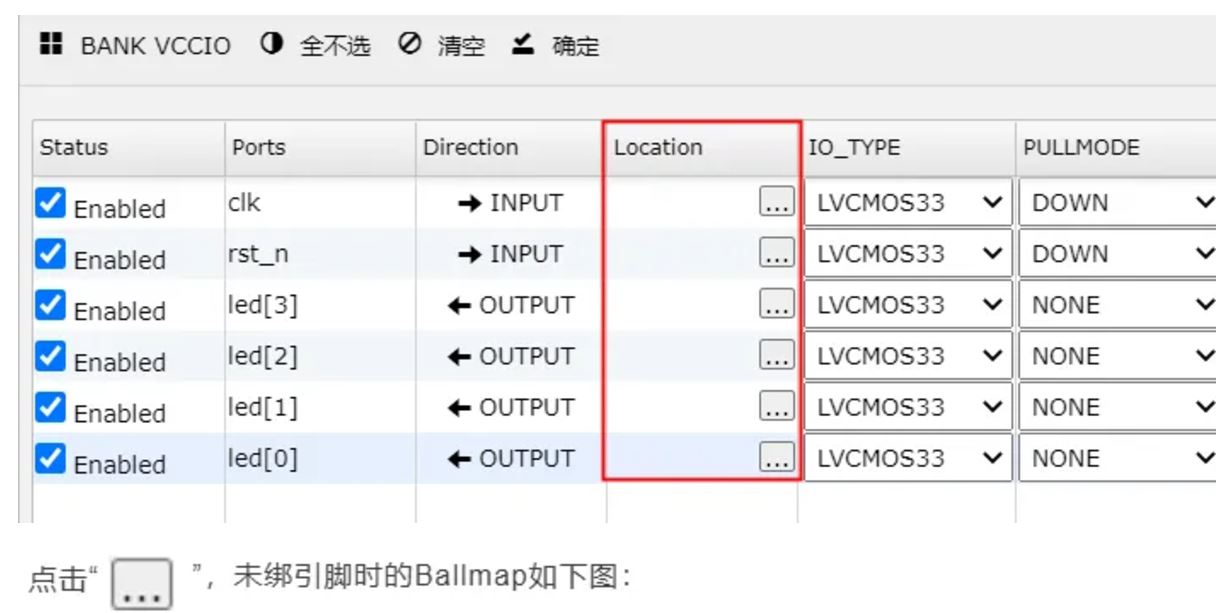

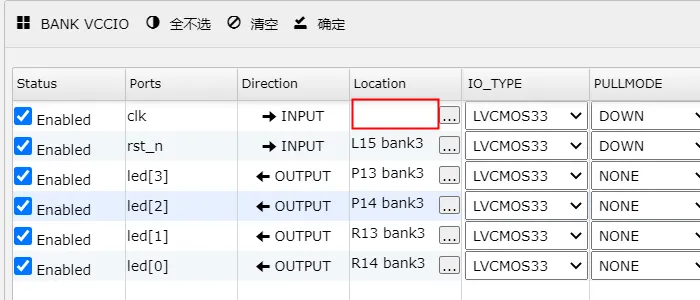

未绑定任何引脚时,打开约束编辑器,Location那一列为空。未绑引脚时的编辑器如下图所示:

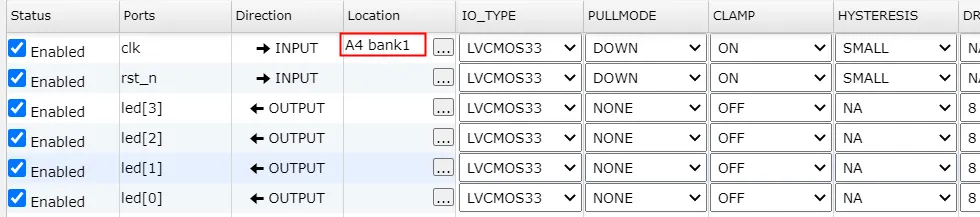

绑定结果如下:

已经绑定引脚后的ballmap

在ballmap页面,其他有白色圈的位置即为其他引脚绑定的位置。

在ballmap页面,点击任何空白方块处,再点击确定,可清除当前引脚的绑定,例如下图:点击空白方块处,然后点击确认,最后clk绑定的引脚为空。

从下图可见,clk引脚被清空,同理,其他引脚也可进行该操作。

注:将鼠标移动到想要了解的引脚上停留几秒之后,可显示出该引脚的相关信息。如下图:

详情请点击官网网址https://www.isilicontech.com/sv.aspx?nid=8&typeid=147#s50010,并按照图示步骤操作。

文章来源:智多晶