作者:Ivy Guo,AMD工程师;来源:AMD开发者社区

环回(loopback)是GT的一种特殊配置模式。可以把发送端的数据直通过自身PMA层或对方器件(不加进一步处理)后再转回给发送器件的接收端,并校验是否有误码。这种工作方式可以检验GT配置是否正常,外部链路信号质量等。在比较复杂的断链场景下一般作为一个基本的调试定位手段。

环回分为近端(Near-End)环回和远端(Far-End)环回。具体介绍可以参考AM017,CH2。

https://docs.amd.com/r/en-US/am017-versal-gtm-transceivers

近端环回比较常用且方便,远端环回则需要两个独立的器件来通信。AMD的开发板一般只有一块FPGA或者Versal芯片,做远端环回测试的话需要把两块开发板对接起来,并且保证两块板子的时钟同源。这里我们介绍一种用一块开发板测试远端环回功能的办法。

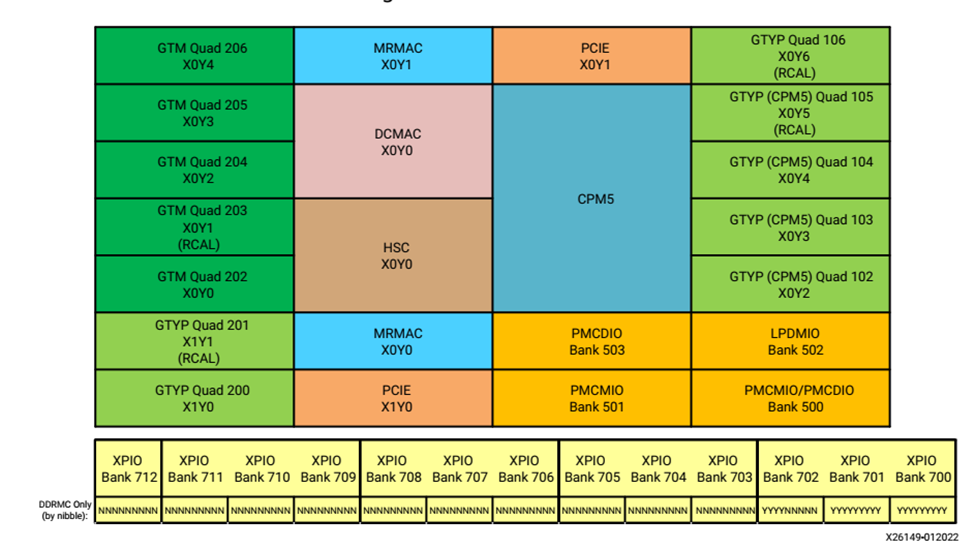

以Versal VPK120开发板为例。其上包含一块VP1202的芯片,可用GT Quad如下:

https://www.xilinx.com/products/boards-and-kits/vpk120.html

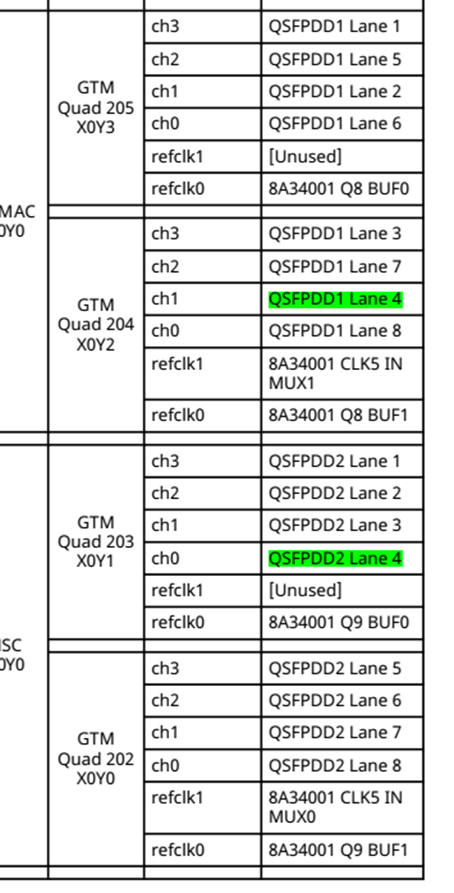

示例选择Quad 203来模拟发送端器件。查看https://docs.amd.com/r/en-US/ug1568-vpk120-eval-bd, QSFP-DD1和QSFP-DD2的连接关系如下:

可以看到Q203的ch0和Q204的ch1可以对应连通。选择Quad 204模拟作为接收端器件,使用DAC电缆线对接两个QSFP-DD。

Step 1:

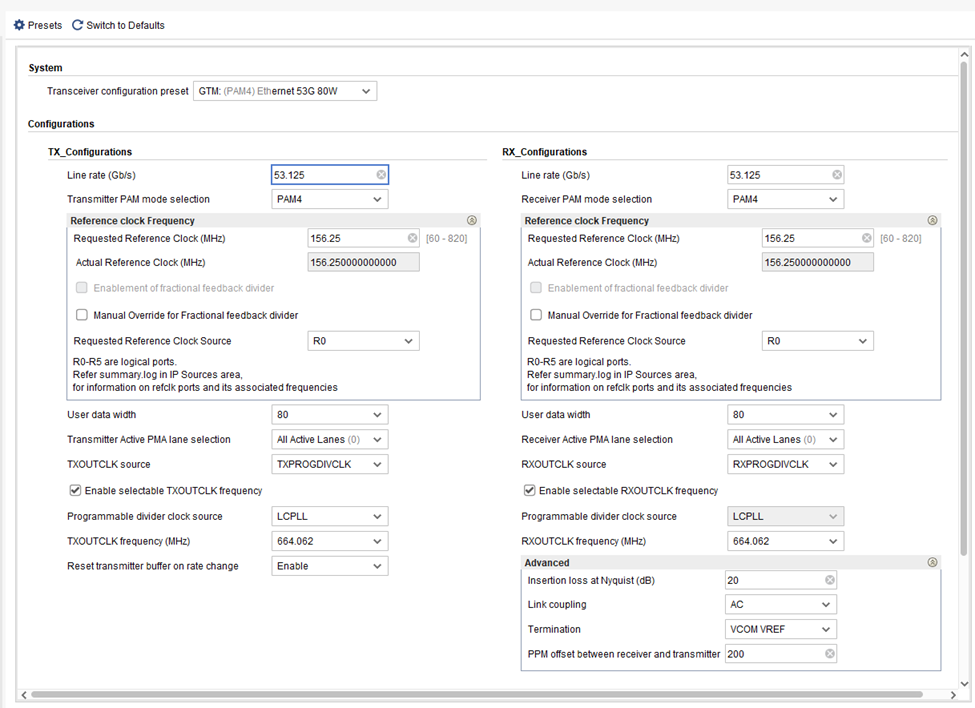

在Vivado 2024.1里面建立测试工程。因为是模拟两个不同器件,这里分别用不同的gt_bridge去控制两个Quad。Create Block Design, 里面添加两个gt_bridge和两个gt_quad_base。在gt_bridge里面选择好协议如下 (可按自己需要选择):

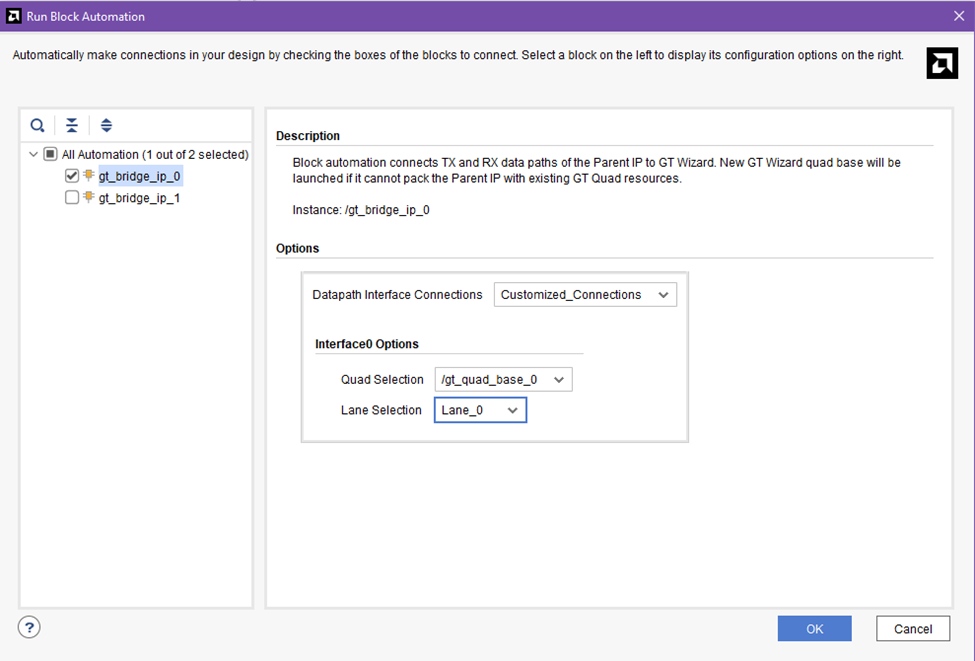

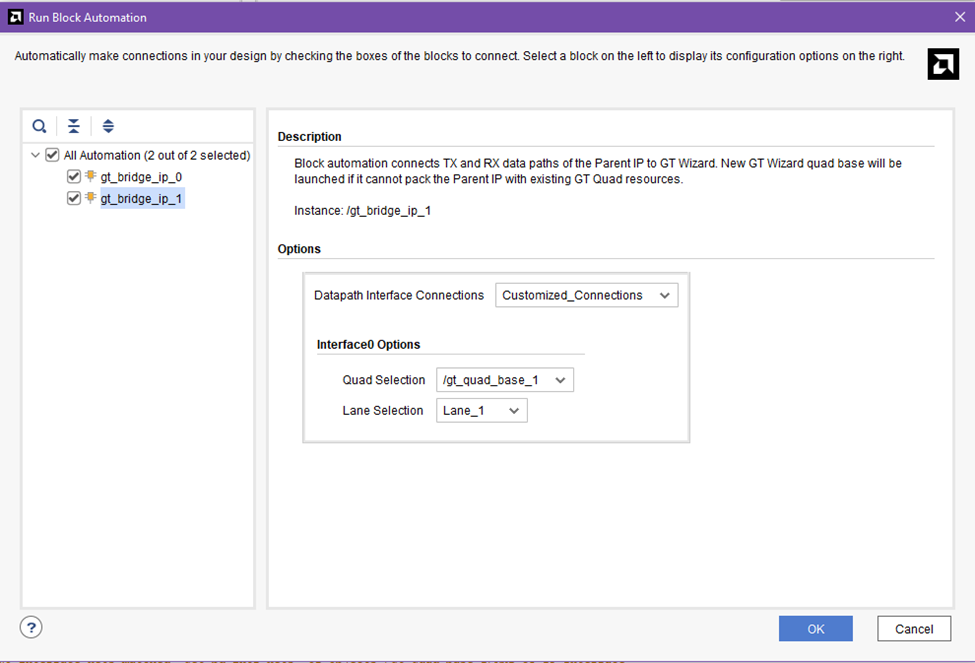

使用Run Block Automation – Customized_Connections, 自动化连线:

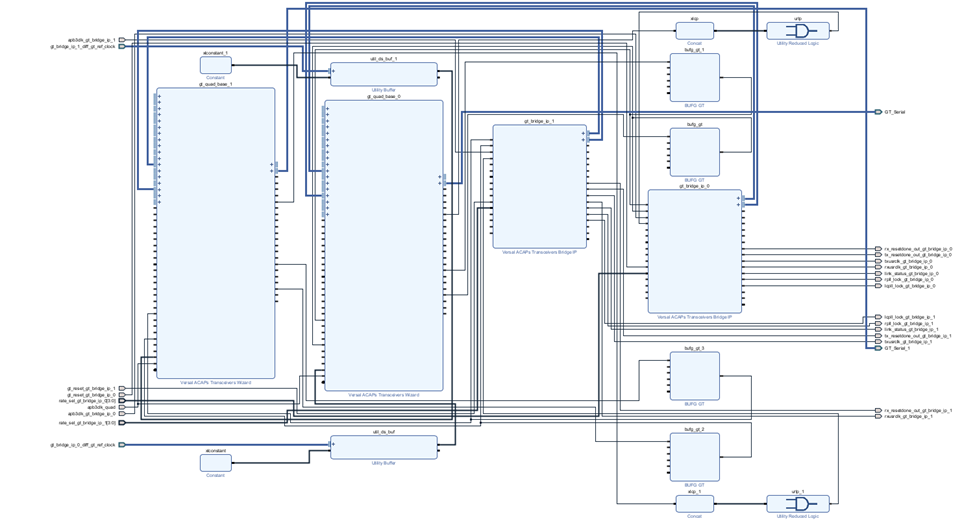

自动化连线结果如下:

Step 2:

远端环回需要两个器件使用同源时钟,我们把Quad 203和204的REFCLK修改为同一个。另外去掉该基本测试里面不必要的IO控制,只保持GT serial ports即可。

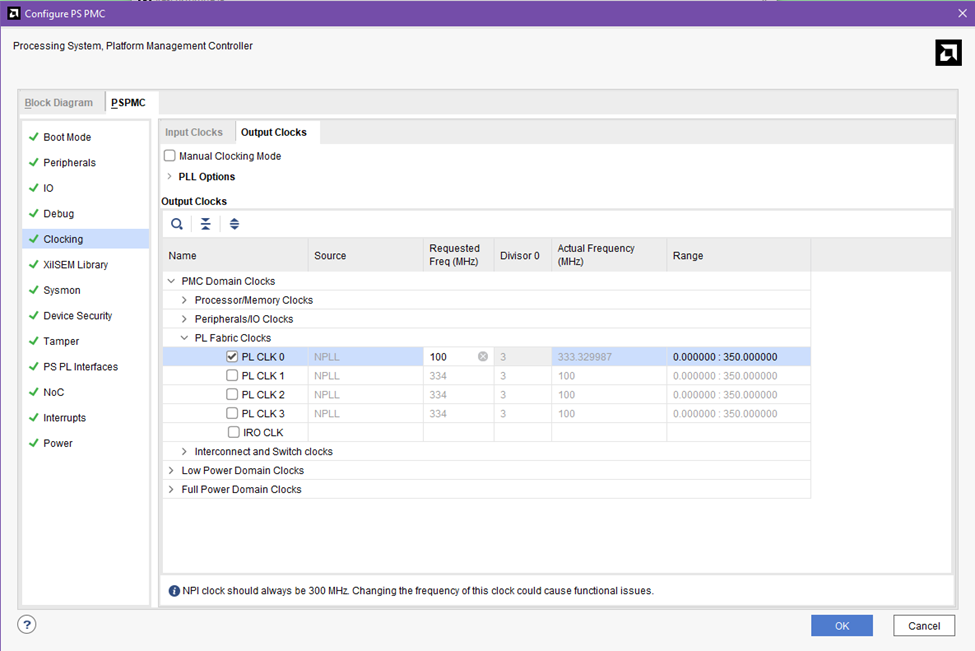

驱动控制逻辑所需的apb3clk,可以用CIPS来产生:

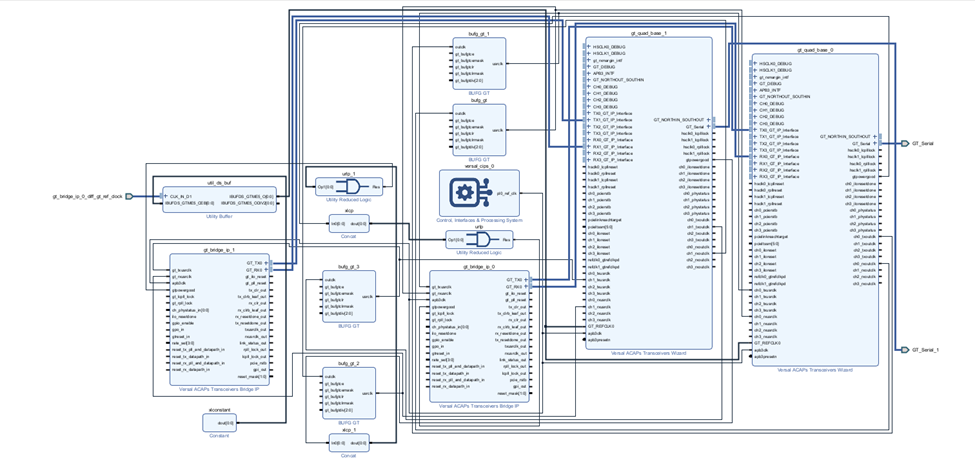

修改后的diagram如下:

保存,生成HDL wrapper。

Step 3:

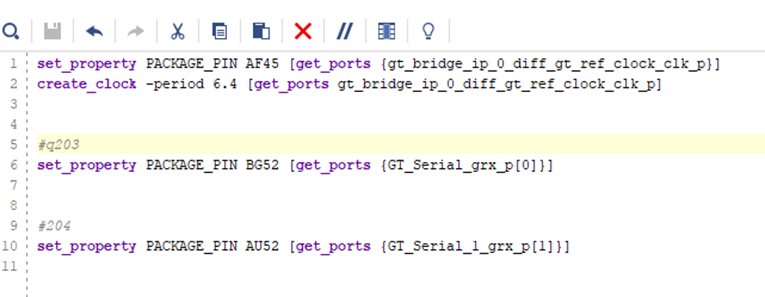

根据VPK120开发板的设置,添加REFCLK和GTM位置约束:

接下来按普通流程生成下载文件pdi即可。

Step 4:

将VPK120的SW1设置为0000 (JTAG),启动并下载pdi文件。

Step 5:

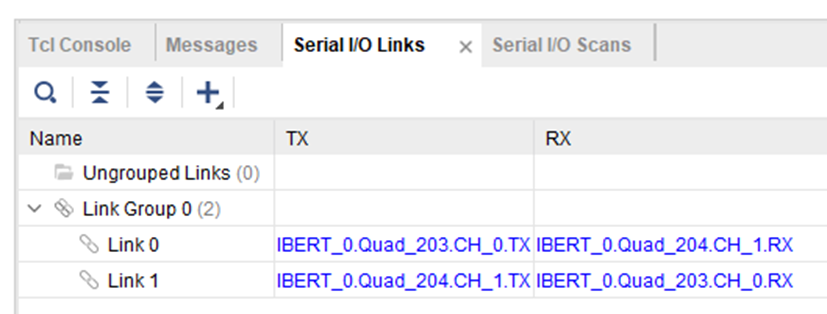

按照刚才对照的硬件连接关系,在Serial I/O Links中建立链:

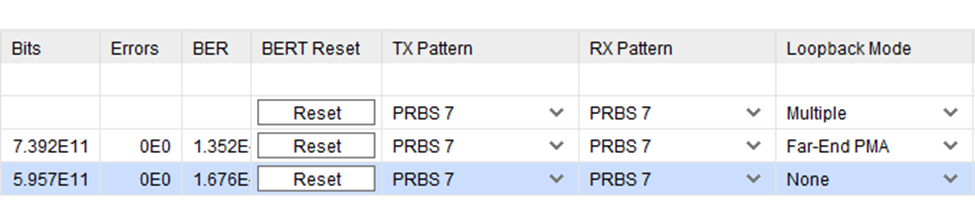

选择自己想要测试的PRBS pattern,设置第一个link Q204 ch1. RX为Far-End PMA模式,Q203 ch0.RX为None(由于此处双向通信,两个link的设置可以互换)。此时Q204作为了远端执行环回的器件,Q203则是发送端器件。这样就模拟了两个器件以远端环回对接的连接方式:

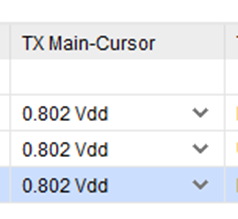

设置TX Main-Cursor;如果外部cable插损比较大,还可以针对性调节其他TX Cursor:

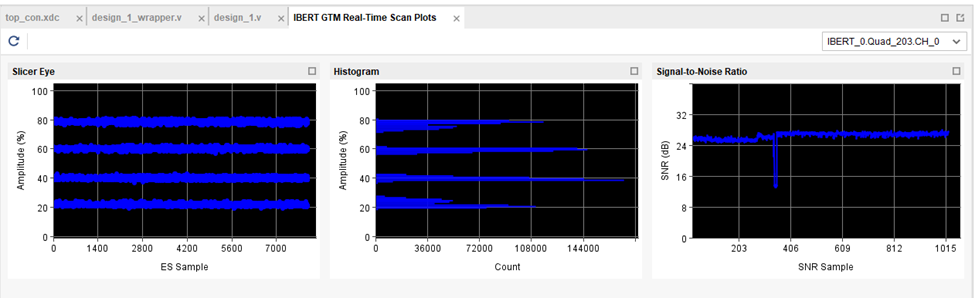

分别复位两个link。之后在IBERT GTM Real-Time Scan Plots的眼图里面,可以看到通信已经建立起来:

应用此文的办法,可以在有限的实验室环境下做针对Far-End PMA/PCS Loopback的一些特性测试和观察,方便进一步学习。