AI引擎配置和启动

1. AI引擎阵列配置

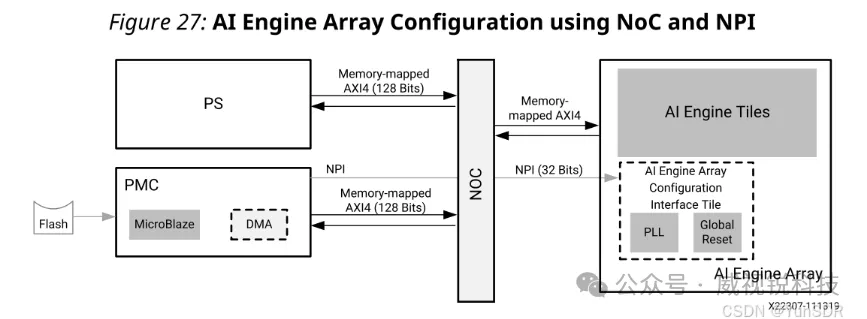

在AI Engine阵列配置中有两种顶级方案:通电时的AI Engine阵列配置和AI Engine阵列部分重新配置。下图显示了AI引擎阵列和配置接口的高级视图,其中沿着有通过NoC连接到PS和平台管理控制器(PMC)的寄存器。

任何内存映射的AXI4主机都可以使用NoC(例如PS和PMC)配置AI引擎阵列中的任何内存映射的AXI4寄存器。由于全局寄存器映射到NPI地址空间,因此可以使用NPI接口对阵列配置接口片中的全局寄存器(包括PLL配置、全局复位和安全位)进行编程。

AI引擎阵列的配置时间

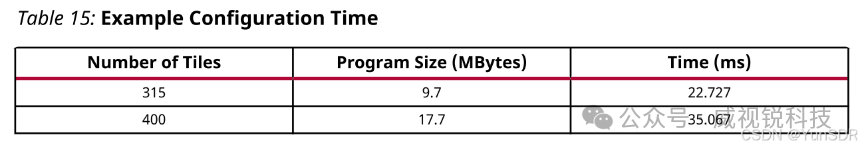

AI引擎阵列配置使用NoC接口上的内存映射AXI4完成。NoC可以支持128位传输。在AI Engine模块内部,内存映射的AXI4具有32位数据传输速率,可以在突发模式下传输1到4个32位字。下表显示了VCK 190板上典型设计的配置时间示例。

2. AI引擎启动顺序

本节介绍AI Engine阵列的靴子过程中涉及的步骤。

1.上电和上电复位(POR)解除断言:与AI引擎阵列相关的所有模块(包括PLL)均已通电。上电后,PLL以默认速度运行。平台管理控制器(PMC)和NoC需要在AI引擎靴子序列启动之前启动并运行。阵列电源打开后,PMC可以取消AI引擎阵列中的POR信号。

2.使用NPI配置AI引擎阵列:上电后,PMC使用NPI接口对AI引擎阵列中的不同全局寄存器(例如PLL配置寄存器)进行编程。通过NPI进行AI引擎阵列初始化所需的AI引擎配置映像来自闪存设备。

3.使能PLL:配置PLL寄存器后(POR后),PLL使能位可使能PLL。然后,PLL建立在编程频率上,并置位PLL信号。PLL输入(ref_CLK)来源于hsm_ref_CLK,并在控制接口和处理系统(CIPS)中生成。时钟的生成和分配在Versal Adaptive SoC技术参考手册(AM011)的PMC和PS时钟章节中描述。

4.释放复位:PLL锁定后,软件可对寄存器进行编程,以解除AI引擎阵列的全局复位信号。

5.AI引擎阵列编程:AI引擎阵列接口需要从NoC接口通过内存映射的AXI4进行配置。这包括所有AXI4流开关、内存映射AXI4开关、阵列接口DMA、事件和跟踪配置寄存器。

3. AI引擎阵列重新配置

AI引擎配置过程将bootgen工具生成的可编程设备映像(PDI)写入AI引擎配置寄存器。AI引擎配置通过NoC在内存映射的AXI4上完成。NoC上的任何主机都可以配置AI Engine阵列。有关使用bootgen工具生成PDI的更多信息,请参阅AI Engine Tools and Flows User Guide(UG1076)。

AI Engine阵列可随时重新配置。该应用程序驱动重新配置。安全的重新配置需要:

•确保重新配置不会在正在进行的通信期间发生。

•在重新配置之前,禁用AI引擎到PL的接口。

•在重新配置子区域之前排空子区域中的所有数据,以防止来自先前配置的残余数据的副作用。

AI Engine阵列重新配置描述了两种场景:

•完全重新配置:为AI Engine阵列断言全局重置,并通过下载新的配置映像来重新配置整个阵列。

•部分重新配置:阵列中的一些AI Engine瓦片被重新配置,而其余瓦片继续运行内核。重新配置不会影响AI引擎阵列中已在运行的内核。

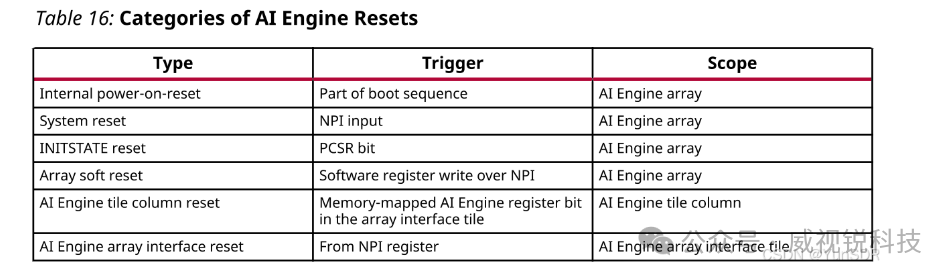

PMC和PS负责初始化AI引擎阵列。下表总结了全局AI引擎阵列可用的重置控件。

列重置和阵列接口瓦片重置的组合(参考AI引擎阵列层级)实现了部分重新配置用例,其中包括AI引擎瓦片和阵列接口瓦片的子阵列可以被重置和重新编程而不干扰相邻子阵列。处理阵列拆分和添加隔离的细节取决于用例的类型(多用户/租户或单用户/租户多任务)。

文章来源:威视锐科技