作者:Jon Lu,AMD开发者;来源:AMD开发者社区

什么是环回测试?

环回测试通过生成流量并将其发送回原先的流量来源,以测试系统功能与性能。

内部环回会将流量环回至同一片上收发器

用于评估该收发器是否按配置工作

外部环回通过环回模块或环回线缆向链路伙伴发射流量

通常用于评估链路与通道 SI

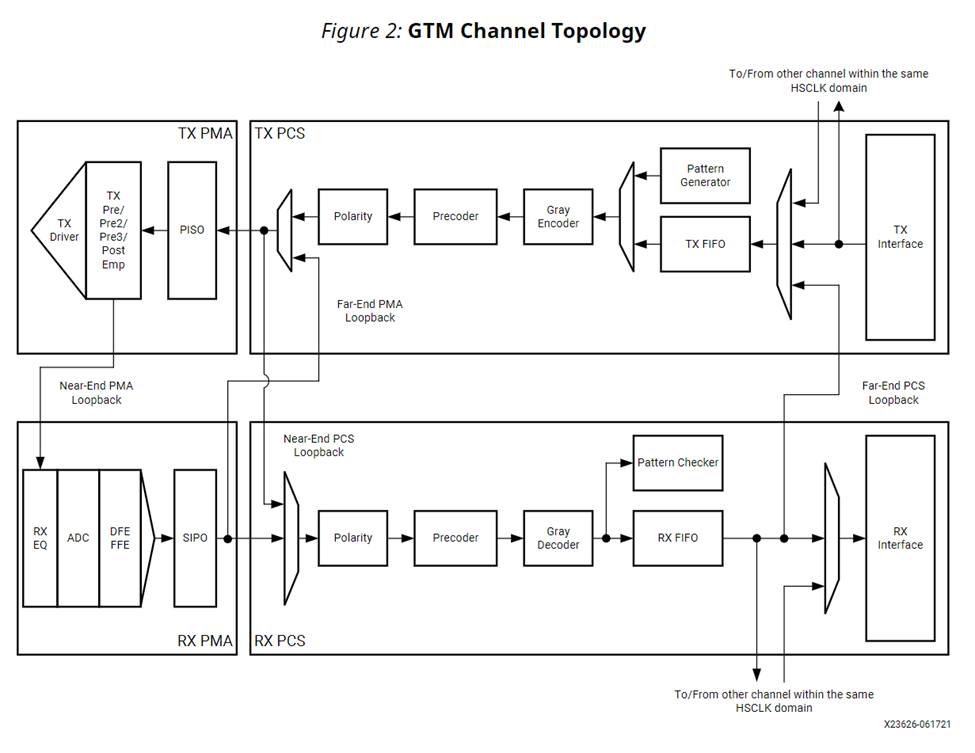

在 GT 上支持 4 种模式:

1. 近端 PCS 环回

GT 通过连接 TX 和 RX PCS 的通路,在内部向自身发送数据

在 IBERT 上无眼图扫描可用 - 仅有“数字”数据

通常用于测试正常收发器功能

在成对 TX 差分输出上有数据可供探测之用

2. 近端 PMA 环回

GT 通过连接 TX 和 RX PMA 的通路,在内部向自身发送数据

在 IBERT 上有眼图扫描可用 - 有“数字”数据和“模拟”数据

可用于测试 GT 均衡器

在成对 TX 差分输出上有数据可供探测之用

3. 远端 PMA 环回

流量通过环回模块或环回线缆等传输到链路伙伴,然后链路伙伴会回传数据

用于测试通道 SI -“数字”和“模拟”

GT 接口上不存在 RXDATA

4. 远端 PCS 环回

向链路合作伙伴发射流量,数据同样会流经链路伙伴的 PCS 块

用于测试整个通信链路 -“数字”和“模拟”

GT 接口上存在 RXDATA

Versal GTY 与 GTM 环回路径:

环回测试目标

1. 确保 GT 按配置来工作

使用环回测试验证 GT PCS 和 PMA 按配置来工作

线速率与数据完整性、编码器、缓冲器旁路和变速箱函数是常见的评估项目

AMD 提供 IBERT IP,用于回读计算所得的 GT 线速率与 USERCLK 频率、切换 PRBS 生成,以及调整 RX 均衡器。IBERT 需要 JTAG 或 XVC。

2. 通过 BER 评估 GT 性能

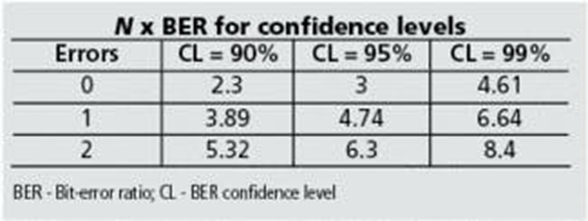

误码率 (BER) = 接收的比特错误数 / 发射的总比特数

BER 是随机的,需要运行 N 比特才能保证 BER 与可信度一致

针对每条通道,大多数 GT 设计均配置为 >1 Gb/s,例如,1G、10G、25G 和 56G

有多项标准用于指定测试模式和所需 BER,例如,10GBASE-* Ethernet = 1e-12。指定的 BER 也可能取决于 FEC、传输介质和传输距离。

经验法则 - 0 个比特错误:95% BER 需 N * BER = 3,99% BER 需 N * BER = 4.6,更多比特错误 -> 增加 N

通道信号完整性与 EQ 调谐

检查通道功能是否正常

按需对均衡器设置进行调谐

何谓 IBERT?为什么使用 IBERT?

Integrated Bit Error Ratio Tester (IBERT) 是 AMD 基于 GUI 的 GT BER 测试解决方案

IBERT 是通过 Vivado™ 硬件管理器来访问的(需 JTAG)

显示 GT 线速率与 PLL 锁定状态,以及眼图扫描

控制模式生成器与检查器、复位、均衡器、环回模式

使用方便,支持快速调试

可与 ILA、VIO、ChipScope 连携使用

. 例如,探测 *RESETDONE、*PLLLOCK 和/或断言其他复位或用户逻辑

如果无法访问 JTAG...

手动眼图扫描不需要 JTAG,可通过 AR 指示信息来获取支持

环回和流量生成器可利用 PL 通过 GT 寄存器/端口来进行控制

Xilinx Virtual Cable 用于基于以太网对 JTAG 连接进行仿真

需要构建 Linux/PetaLinux 应用

IBERT 版本之间的常见差异

独立 IBERT IP

控制模式生成器/检查器、RX 均衡器

查看线速率、PLL 锁定、复位等。

In-System IBERT IP

UltraScale/UltraScale+™ GT Wizard 选项,添加捕获眼图扫描的功能

7 系列对比 UltraScale/UltraScale+ 对比 Versal™

7 系列/UltraScale/UltraScale+:独立 IBERT IP 需包含在 GT 设计内

UltraScale/UltraScale+:GT Wizard 中的 In-System IBERT 选项需在硬件管理器中执行眼图扫描

Versal:独立 IBERT 与 In-System IBERT 功能集成到所有 GT Wizard 设计中,无需其他 IP

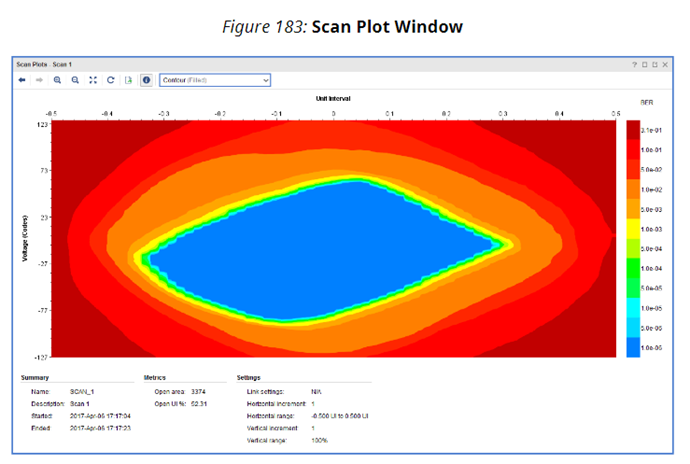

眼图扫描

GTY 器件仅使用 NRZ 信令 - 眼图扫描显示全 BER 深度

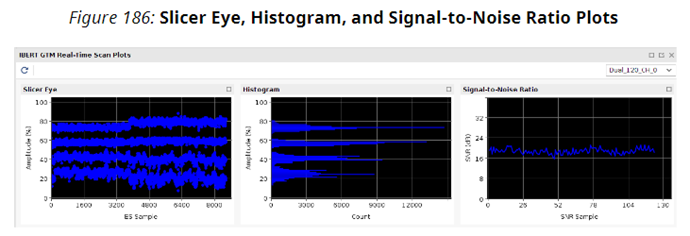

GTM 器件使用 NRZ 和 PAM4 信令,因此 RX 基于 ADC - 眼图扫描仅对 Slicer 眼图进行采样

In-System IBERT 支持 UltraScale+ GTH/GTY 眼图扫描

MPSoC PS-GTR 使用独立眼图扫描模块(UG936 实验课)

有关 7 系列 GT 设计的信息,应查阅 AR64098、AR60024、XAPP1198

手动眼图扫描

请查阅对应 GT 和器件家族的答复记录

这些答复记录提供了有关手动生成眼图扫描的 RTL 指示信息。

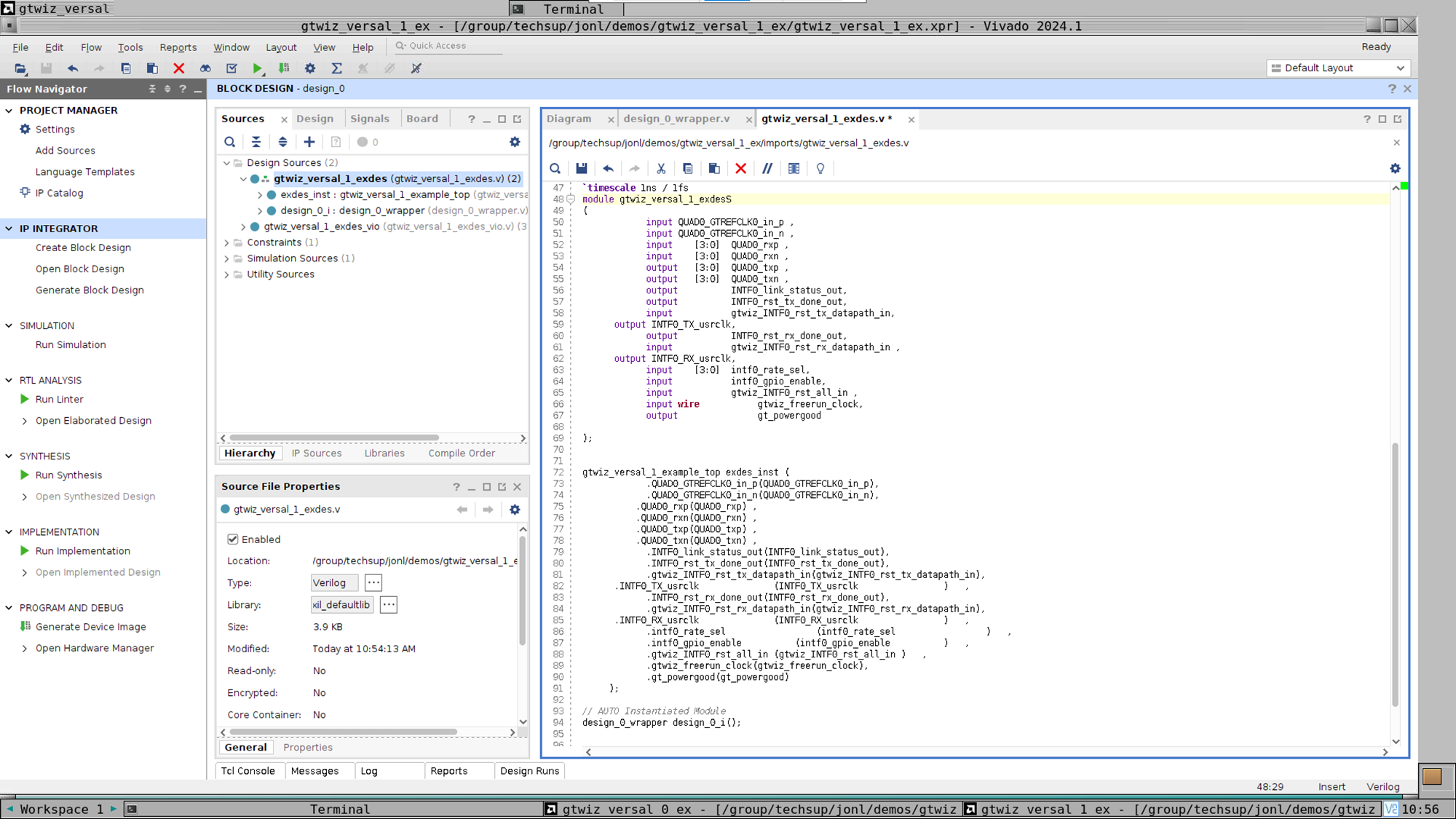

如何创建可供 IBERT 立即使用的设计 (US/US+)

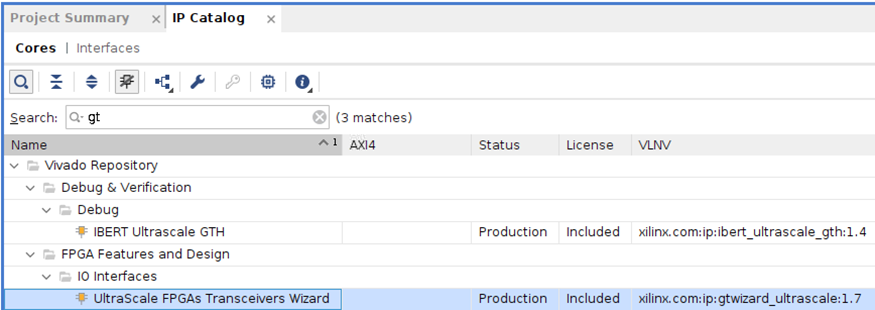

1. IBERT UltraScale GTH/GTY/GTM

在 IP 目录中,搜索 IBERT Ultrascale GT*

配置 IBERT GT 通道并根据 IBERT IP 创建设计示例

或通过 GT 和 IBERT IP 上公开的端口,在封装文件中将 IBERT 连接到现有 GT 设计

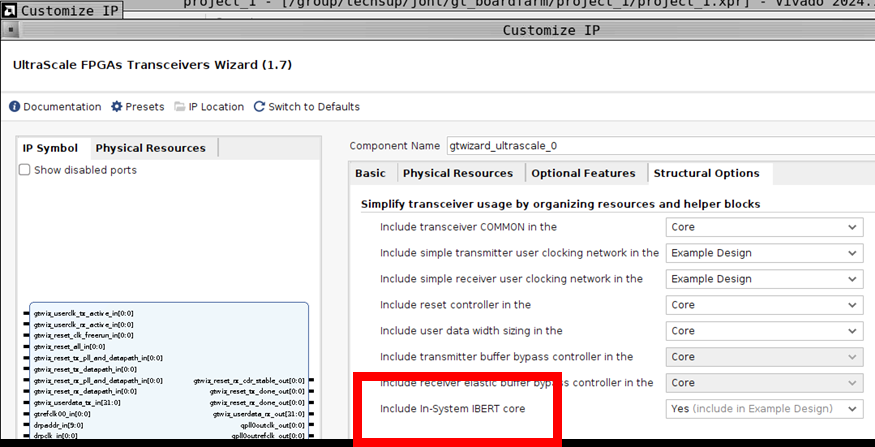

2. In System IBERT

打开 GT Wizard GUI

在“Structural Options”(结构选项)选项卡中切换开启“Include In-System IBERT core”(包含 In-System IBERT 核)

如何创建可供 IBERT 立即使用的设计 (Versal)

特此提醒,IBERT 已包含在所有 Versal GT 设计中。

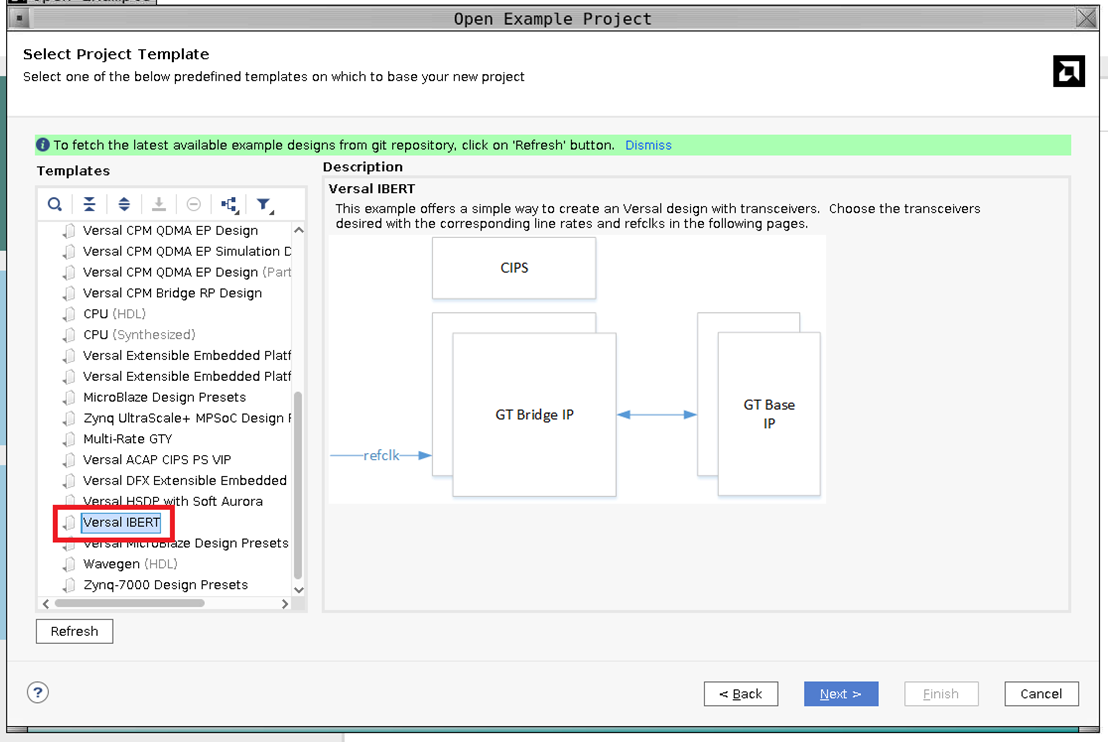

1. Versal IBERT CED

选择“File > Project > Open Example”(文件 > 工程 > 打开示例)

选择“Part”(部件),然后设置线速率和四通道 (Quad)

约束位置和参考时钟

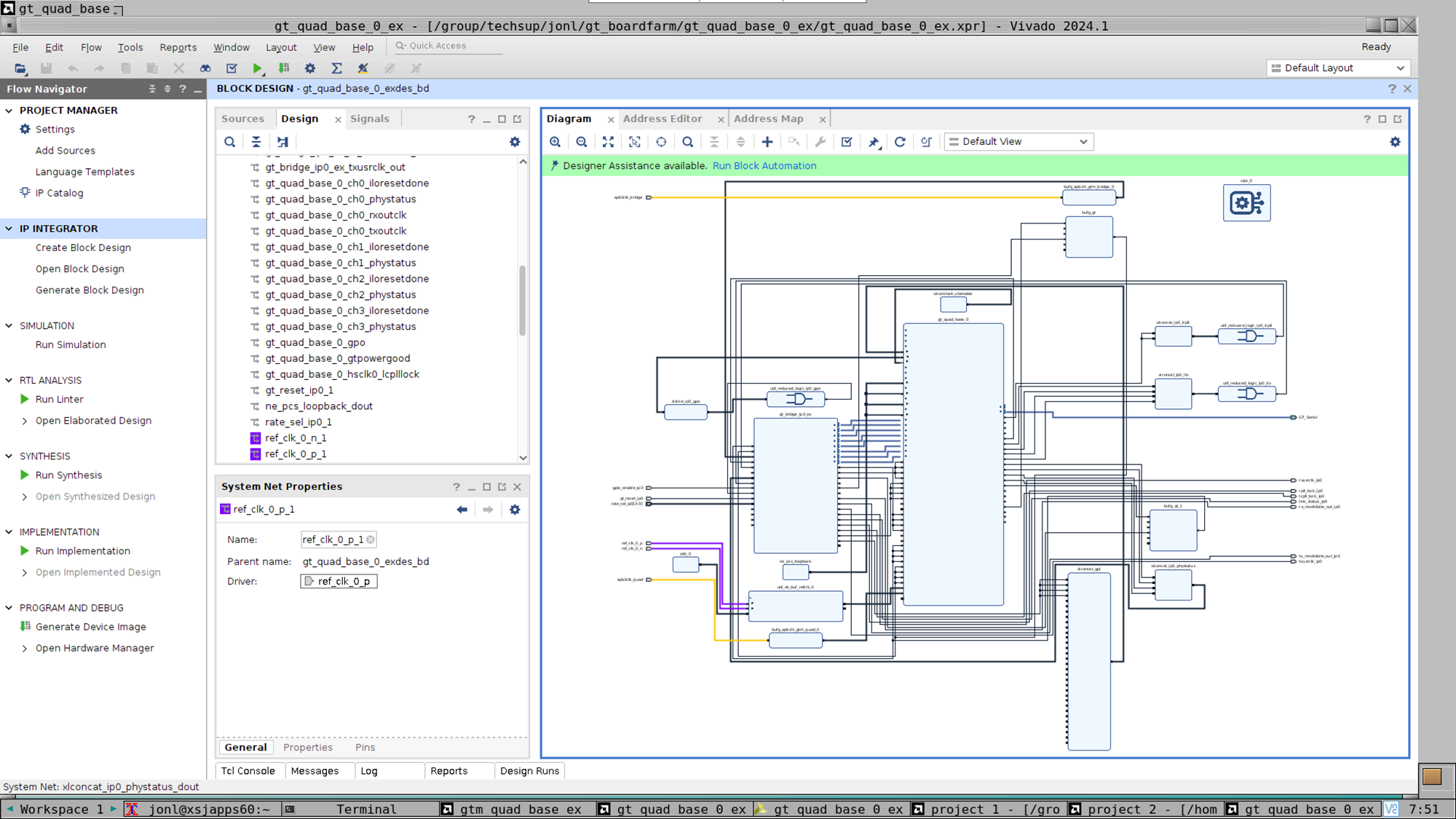

2. GT 设计或设计示例

配置 gt_quad_base 或 GT Subsystem IP

(可选)生成设计示例并约束 GT 位置和参考时钟

2024.1+ GT Subsystem IP 还包含 VIO 封装文件

3. 父级 IP 设计或设计示例

以太网设计、PCIe 等将例化包含 IBERT 功能的 GT。

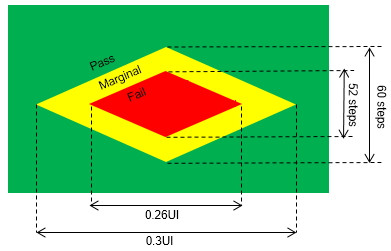

解读眼图扫描

Y 轴以运行均衡器后的电压“代码”表示 - 约 2mV = 1 个代码。

X 轴以单位间隔时间 (UI) 表示

良好的眼图扫描 = 距离中心 +/- 0.3 个 UI,于 Dwell BER 处采样可得 +/- 30 个代码

US/US+ 和 Versal GTY 眼图模板:

US/US+ GTH 眼部模板

请参阅 IBIS-AMI 模型

https://www.xilinx.com/member/versal_transceiver_ibis_ami_models.html

https://www.xilinx.com/member/ultrascale_plus_ibis_ami.html

请参阅当前测试的协议,获取正确的 Dwell BER

GT 设计示例技巧

连接 GT refclk 参考时钟和自由运行时钟

在 AMD 开发板上,查询开发板用户指南和原理图

自由运行时钟可从 CIPS 生成

将 GT 约束到目标位置

检查是否已配置目标 TX/RX 主时钟源

IBERT CED 或 GT+VIO 公开的端口数量比 GT 设计示例更少(相同功能)

如果不使用某些端口,则后续要删除或约束的端口数量更少

公开的端口数量不超过必要的数量(前提是这些端口当前不受控制)

可能导致出现浮动值或者意外行为

IBERT 常见问题

报告的 GT 线速率与 USRCLK 不正确

NPI 时钟配置必须为 300 MHz,否则 IBERT 将报告线性移位

在 Vivado 2024.1 及更高版本中已修复

IBERT 未报告正确的 BER 或链路状态

以 TX 开始 IBERT 测试,然后是 RX 和 BERT 复位

检查是否有任何端口未正确连接或绑定

眼图扫描 GUI 无法正常工作

尝试将眼图扫描导出到 .csv 文件 - 右键单击 IBERT 眼图扫描图,在文本编辑器中打开 .csv

检查确认环回模式未设置为“Near-End PCS”(近端 PCS)

更多资源

请参阅随附的 PowerPoint 获取更多详细信息

包含 XVC 和 BER 测试资源

常见 BER 测试持续时间

GT 与 IBERT 比较表

远端环回设置