来源:内容编译自pcisig。

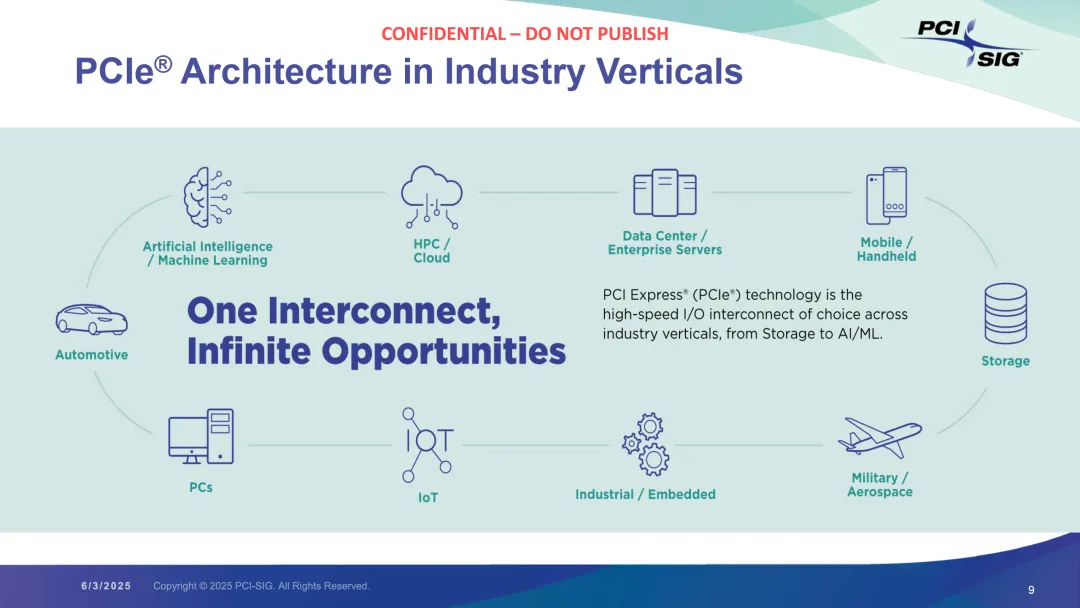

PCI-SIG今日宣布向会员正式发布PCI Express ( PCIe ) 7.0规范,该规范速度达到128.0 GT/s。PCIe 7.0规范面向数据驱动型应用,例如人工智能/机器学习 (AI/ML)、800G 以太网、云计算和量子计算。PCIe 8.0规范的探索工作已在进行中,以继续支持行业在PCIe技术生态系统中的投资和产品路线图。

PCIe 7.0 规范特性:

通过 x16 配置提供 128.0 GT/s 原始比特率和高达 512 GB/s 的双向速率

采用 PAM4(4 级脉冲幅度调制)信令和基于 Flit 的编码

提供更高的电源效率

保持与前几代 PCIe 技术的向后兼容性

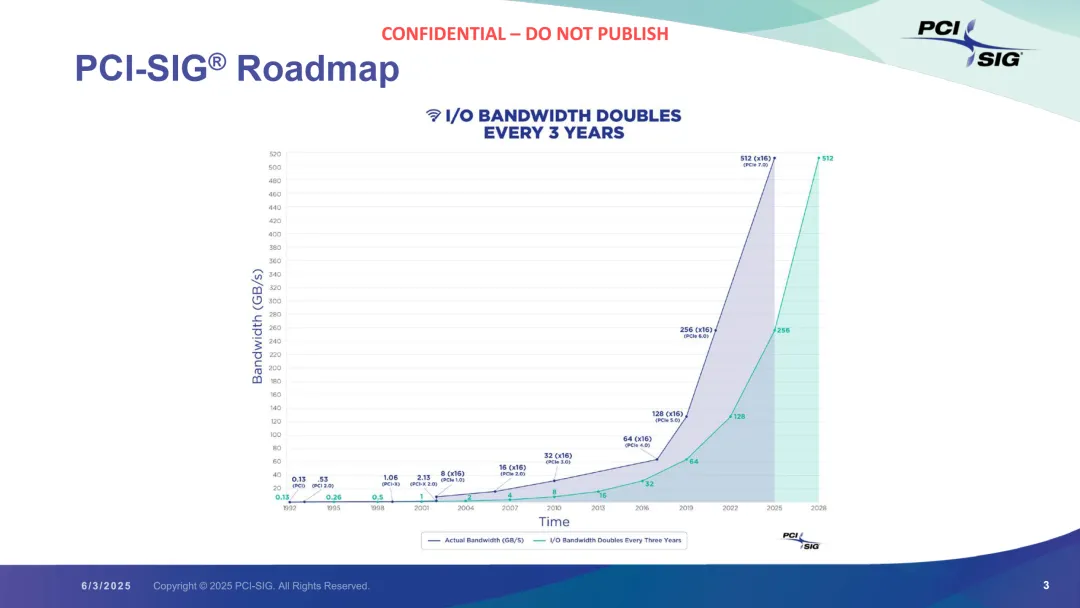

PCI-SIG 总裁兼主席 Al Yanes 表示:“PCIe 技术在过去二十多年一直是高带宽、低延迟 IO 互连的首选。我们很高兴宣布发布 PCIe 7.0 规范,这延续了我们每三年将 IO 带宽翻一番的悠久传统。随着人工智能应用的持续快速扩展,下一代 PCIe 技术将满足部署 AI 的数据密集型市场的带宽需求,包括超大规模数据中心、高性能计算 (HPC)、汽车以及军事/航空航天。”

PCI-SIG 总裁兼主席 Al Yanes 表示:“PCIe 技术在过去二十多年一直是高带宽、低延迟 IO 互连的首选。我们很高兴宣布发布 PCIe 7.0 规范,这延续了我们每三年将 IO 带宽翻一番的悠久传统。随着人工智能应用的持续快速扩展,下一代 PCIe 技术将满足部署 AI 的数据密集型市场的带宽需求,包括超大规模数据中心、高性能计算 (HPC)、汽车以及军事/航空航天。”

“PCIe 规范的最终版本发布是一个特殊的时刻,”More Than Moore 首席分析师兼首席执行官 Ian Cutress 表示。“尽管业界在高速信号方面制定标准非常复杂,但通过 PCIe 技术实现的计算和网络需求的增长却达到了前所未有的水平。数据中心已准备好开始部署基于 PCIe 7.0 技术的网络,而且我接触到的几乎所有 ASIC 公司都已与 IP 提供商接洽,并准备从中获益。尽管 PCIe 6.0 的部署已经非常普及和备受关注,但 PCIe 7.0 规范比以往任何版本都更受关注。”

如上所述,就实际带宽而言,PCIe 7.0 将通过 x16 通道配置提供高达 128.0 GT/s 的比特率和高达 512 GB/s 的双向带宽。PCIe 7.0 还采用了 PAM4(四级脉冲幅度调制)信号和基于 Flit 的编码。该技术将实现更高的能效,并保持与前几代 PCIe 技术的向后兼容性。

与此同期,PCI-SIG宣布推出 PCIe光纤互连解决方案。

PCI-SIG今日宣布了一项新的光纤互连规范修订,旨在提升PCI Express ( PCIe )技术的性能。“光学感知重定时器工程变更通知”(ECN) 修订了 PCIe 6.4 规范和新的PCIe 7.0 规范,纳入了基于 PCIe 重定时器的解决方案,为通过光纤实现 PCIe 技术提供了首个行业标准化方法。

PCI-SIG 总裁兼主席 Al Yanes 表示:“我们看到了基于 PCIe 技术的行业标准光互连的需求,而 Optical Aware Retimer ECN 是添加模块化光解决方案的第一步。我们预计该技术将首先应用于人工智能/机器学习和云等数据中心应用。随着 PCIe 技术逐渐普及,我们预见到众多细分市场将出现创新用例。”

PCI-SIG 总裁兼主席 Al Yanes 表示:“我们看到了基于 PCIe 技术的行业标准光互连的需求,而 Optical Aware Retimer ECN 是添加模块化光解决方案的第一步。我们预计该技术将首先应用于人工智能/机器学习和云等数据中心应用。随着 PCIe 技术逐渐普及,我们预见到众多细分市场将出现创新用例。”

光学感知重定时器ECN:

无缝支持各种光学技术,用于现有符合 PCIe 6.4 和 7.0 规范的交换机、根复合体和端点硅片设计之间的光学互连

扩大机架和舱室的覆盖范围

允许跨电域和光域进行多路复用和数据映射

比铜缆解决方案更紧凑的实现

现代 AI 工作负载需要一种专门的架构,该架构集成了多个加速器,并与中央处理器协同工作。一些最先进的架构要求单个计算单元内最多包含 1,024 个加速器。因此,计算扩展结构需要最快的互连,以便通过高吞吐量 I/O 网络将数百个加速器连接到一起,从而有效地训练这些 AI 模型。

PCI-SIG 于 2022 年发布了 PCIe 7.0 技术,并计划于 2025 年发布完整规范(实际他们也如期发布了)。此项发展旨在满足数据密集型应用和市场的巨大带宽需求,包括人工智能/机器学习 (AI/ML)、1.6T/800G 以太网网络、高性能计算 (HPC) 以及高性能计算数据中心的量子计算。PCIe 7.0 将在加速器、处理器、网卡 (NIC) 和其他组件之间提供低延迟、低功耗且可靠的连接,确保高性能计算环境的高效连接。

PCIe 7.0 代表了 AI 和 HPC 硬件基础设施的重大进步,提供了多项关键优势,可满足持续创新和前所未有的数据集的需求:

更高的带宽:PCIe 7.0 的带宽是 PCIe 6.0 的两倍,双向传输速度高达 512 GB/s,拥有 16 条 128 GT/s 的通道。这种增强的带宽对于快速高效地处理大量数据至关重要,这对于 AI 和 HPC 应用至关重要。

低延迟:通过提高信号速率,PCIe 7.0 降低了对 AI 算法中的实时处理和响应能力以及 HPC 中的高速数据处理至关重要的延迟。

兼容性和可扩展性:PCIe 7.0 保持与前几代 PCIe 的向后兼容性,确保与现有硬件的互操作性,并为未来的升级提供可扩展性。这对于将新技术无缝集成到现有的 AI 和 HPC 基础设施中至关重要。

能源效率:尽管性能有所提升,但 PCIe 7.0 仍旨在保持或提高能源效率,这对于降低数据中心和大型计算设施的总体运营成本和环境影响至关重要。

高级功能:PCIe 7.0 引入了新功能和优化,进一步增强了其在要求苛刻的应用中的实用性,包括改进的通道裕度功能、增强的错误检测和报告机制,以及对 CXL 等新兴技术的支持。

通道覆盖范围和信号完整性考量:PCIe 7.0 的目标通道覆盖范围与 PCIe 6.0 保持一致,在单连接拓扑中采用 4 英寸 - 14 英寸系统布线和 2 英寸 - 4 英寸 AIC 布线,焊盘间通道损耗高达 -36dB。为了最大限度地降低根复合体参考封装中的插入损耗和反射,通过最大限度地减少串扰来改善连接器插入损耗、回波损耗、PCB 损耗以及过孔插入和回波损耗。

参考发射机 被指定为 4 抽头 Tx 均衡方案,需要进一步研究链路裕度对抽头系数分辨率和 Tx 预设的敏感性。发射机和参考时钟抖动规格几乎是 PCIe 6.0 的一半,需要更精确、更迭代的方法进行芯片级、电路板和封装的协同设计。

参考接收机 由拟议的基于 CTLE 和 ADC 的参考接收机架构组成。PAM-4 128Gbps 压力眼图方法、抖动容限、校准通道和接收机校准眼图模板的规格均尚未定义。此外,还将定义根复合体 (RC) 和端点 (EP) 的参考封装模型。

PCIe 7.0 连接器的增强和向光学解决方案的过渡

卡机电 (CEM) 连接器由 PCI-SIG 开发,于 2000 年首次推出,对于连接主板与附加卡 (AIC) 和转接卡至关重要。它们支持各种模块,例如用于存储的 SSD、用于图形处理的 GPU、用于网络连接的 NIC 以及 ML/DL 或混合计算模块。对于 PCIe 7.0 CEM 连接器,重点在于减少反射和串扰,确保低电缆损耗、干净的导体端接,并最大限度地减少偏移和周期性谐振。PCIe 7.0 连接器和电缆具有严格的信号完整性要求,目前正在讨论回波损耗偏移等新指标,以提高更高速度下的信号质量和可靠性。

此外,PCI-SIG 成立 PCIe 光纤工作组,标志着其突破了铜缆信号传输(尤其是 CopprLink 外部电缆)的限制,开始拥抱光纤解决方案。光纤布线技术最近被引入 PCI-SIG,引发了人们对扩展计算网络物理覆盖范围的热情。这项技术具有更低延迟和增强热管理能力等优势。

对 PCIe 光纤链路的双重关注包括在协议层调整逻辑通信方案,同时在物理层引入具有更佳热管理和优化光纤链路的新规格。这些改进旨在满足高性能计算和网络领域对速度、可靠性和效率日益增长的需求。向 128Gbps PCIe 标准的过渡标志着芯片设计的重大演进,有望扩展功能、提高缓存一致性,并带来新的设计挑战,包括:

扩展功能:光纤链路可实现更大的传输范围和更高的数据速率,突破铜缆的限制。这有助于提升性能,同时降低功耗和延迟。

缓存一致性:128Gbps SerDes & Controller 的 CuLink 与光纤链路集成,支持缓存一致性。这允许处理器和加速器之间高效共享资源,从而优化整体系统性能。

设计挑战:确保128Gbps的信号完整性和电源完整性至关重要。设计裕度对于补偿这些高速链路中的线对内偏移和通道间偏移至关重要。

行为接收器模型:128 Gbps 的 Rx 模型集成了先进的功能,例如功能更强大的前馈均衡器 (FFE) 和抽头数更高的数字反馈均衡器。实际设计预计将超越最低要求,在所有实际 PVT(工艺、电压、温度)条件下实现目标误码率 (BER)。

压力测试与验证:生成压力激励信号的技术对于验证这些先进的接收机至关重要。这包括在早期标准的基础上进行升级以支持 PAM4 调制以及新的信道和测试要求。

参考链接

本文转载自:半导体行业观察