作者:电子创新网编辑部

三款低密度器件率先出货,聚焦高I/O、低功耗与安全特性,全面升级中低端FPGA解决方案

在边缘计算与安全通信加速融合的今天,全球对灵活、高效、低功耗的可编程逻辑器件(FPGA)需求正在迅速扩大。据MarketsandMarkets报告预测,全球FPGA市场规模将在2027年达到93亿美元,年复合增长率达7.8%。其中,边缘智能终端、工业自动化与医疗仪器等对中小型FPGA器件的需求尤为旺盛,市场正逐步从“性能优先”向“功耗、安全、连接性多维均衡”转型。

为抢占这一增长趋势,AMD宣布其Spartan UltraScale+ FPGA产品家族首批器件(SU10P、SU25P、SU35P)正式量产出货,并在最新Vivado™ 2025.1工具链中全面开放支持。这一代产品专为成本敏感型、功耗约束型应用场景而打造,重点面向工业自动化、边缘AI、医疗检测、通信接口等领域。

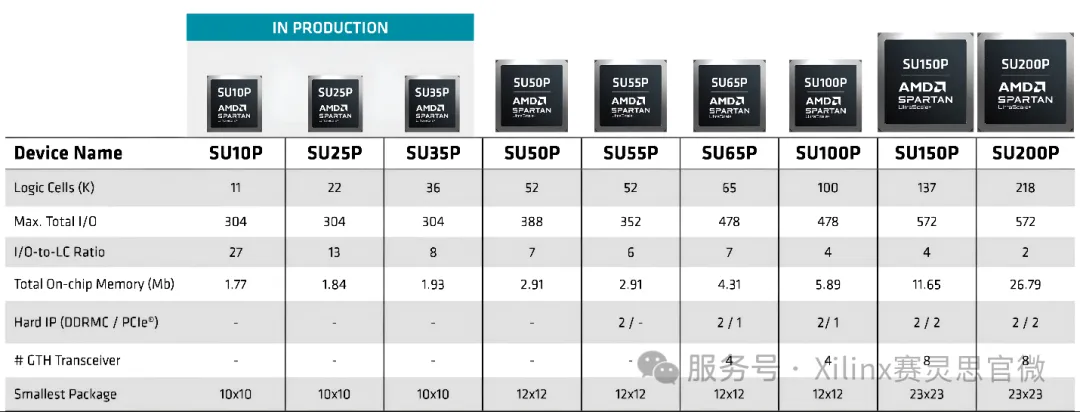

AMD Spartan UltraScale+ 系列产品表

近年来,随着边缘计算节点爆发式增长,小型、低功耗、高接口密度的FPGA逐渐成为终端设备厂商的理想选择:

据IDC统计,2025年全球超过55%的数据将由边缘设备产生并处理,终端智能处理需求激增;

超过80%的工业传感器和控制器对高I/O电平支持和灵活外设连接有明确需求;

在医疗与可穿戴设备领域,对低延迟、高安全、低功耗的逻辑控制器件需求呈现快速增长态势;

同时,美国国家标准与技术研究院(NIST)推动的后量子密码算法标准化进程也对嵌入式系统的安全模块提出更高要求。

上述趋势正倒逼芯片企业推出更轻量、更安全、连接能力更强的FPGA产品。

AMD Spartan UltraScale+ FPGA专为此类新场景设计,继承UltraScale+架构稳定性基础上,注入多项关键创新:

支持NIST认证的后量子密码硬IP:安全启动、TRNG、PUF、防篡改机制一应俱全;

内置LPDDR4X/5内存控制器,支持高达4266 Mb/s带宽,节省15k逻辑资源;

XP5IO新型高速IO接口,最高支持3.2 Gb/s MIPI D-PHY,适配各类高速图像传感器;

集成PCIe Gen4硬核IP,支持EP/RC双模式,快速连接主控系统;

支持8线SPI高速启动,进一步优化系统冷启动时间与配置吞吐。

在连接性方面,其高密度HDIO接口支持丰富的3.3V逻辑,较上一代产品提升I/O与逻辑比,更适用于工业、图像处理等多端口场景。

依托Vivado 2025.1标准版设计套件,开发者可一站式完成从建模、仿真、综合、布局布线到时序验证的全流程设计,尤其对小型团队与快速迭代项目更为友好。Vivado还支持设计复用与跨项目集成,加速多个产品线并行落地,极大提升开发效率。

Spartan UltraScale+ FPGA的量产,标志着AMD在低功耗FPGA市场取得战略性突破。该系列产品填补了从 Artix-7 到 Zynq SoC 之间的成本性能段位,与 Artix、Kintex 以及 Versal 系列形成高低搭配。

在边缘AI、工业视觉、低功耗通信等领域,Spartan UltraScale+将成为连接感知设备与AI推理核心之间的桥梁,构筑全新的智能计算生态基础。

在“万物互联+安全可信”的新工业浪潮下,Spartan UltraScale+ FPGA的量产,不仅是AMD拓展产品线的一小步,更是其融合安全、连接性、低功耗能力于一体,抢占边缘智能主战场的一大步。未来,该系列有望进一步拓展高密度型号,满足更广泛的边缘计算应用。

* 本文为原创文章,转载需注明作者、出处及原文链接,否则,本网站将保留追究其法律责任的权利