SGMII简介

SGMII(Serial Gigabit Media Independent Interface) 通过将网络数据与控制接口进行转换,将复杂的GMII接口转换为一对serdes接口,减少了PHY与MAC之间的接口数量。

SGMII IP遵循《Serial-GMII Specification V1.7》与《IEEE 802.3-2008》规范。

SGMII IP特性

支持10/100/1000Mb/s GMII接口

支持自协商同步

支持MDIO控制接口

支持半双工与全双工模式

支持独立的SERDES调试接口

支持运行状态与自协商结果输出

SGMII IP设计

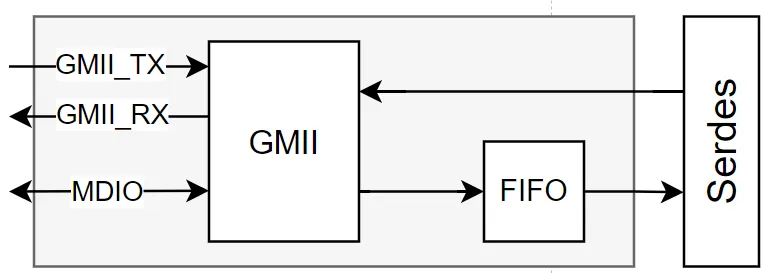

SGMII IP包含了《Serial-GMII Specification V1.7》定义的PCS功能部分与PMA部分。

SERDES实现了PCS部分的8B/10B编解码功能的同时,也实现了PMA部分的数据时钟恢复、数据串行与数据接串功能。

图1 SGMII系统框图

SGMII IP使用

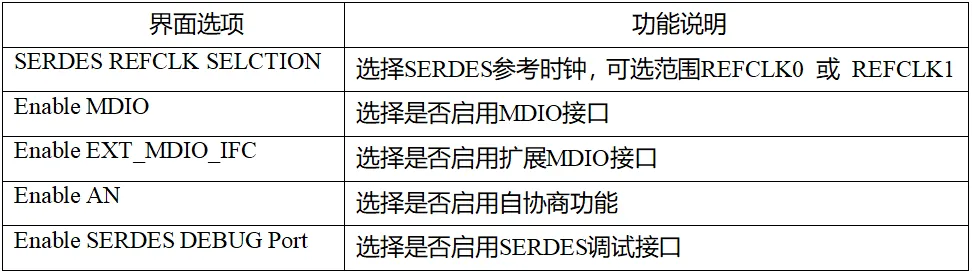

图2 IP界面配置

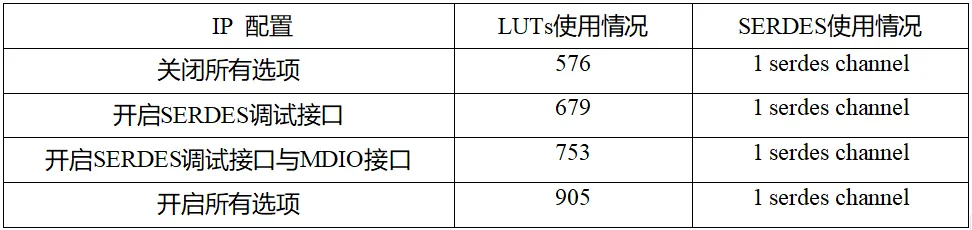

资源占用情况

典型应用示例

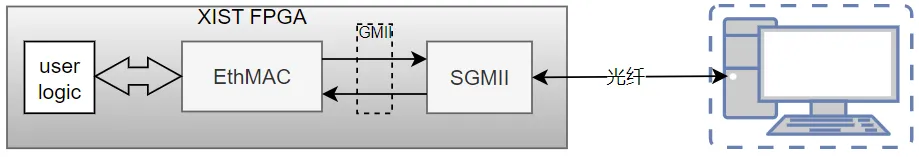

图3展示了一种SGMII的典型应用场景,借助EthMAC IP将用户数据打包为网络数据包,通过光纤将数据传递到电脑端。

图3 SGMII典型应用

获取技术文档与demo

技术文档获取:SGMII IP已发布,用户可以在HQFPGA IP Manage中打开SGMII IP界面查看用户指南,或访问智多晶官网(www.isilicontech.com)下载SGMII IP用户指南。

设计参考案例获取:请联系FAE获取参考设计案例,或在公众号中与我们联系。

文章来源:智多晶