作者:Xu Dong,文章来源:AMD开发者社区

本篇博文演示了在 ZCU208 评估板上运行简单的 RFDC 示例的不同 Vitis™ 流程。此处使用的是 xrfdc_read_write_example,但并不限制您实现自己的应用。

此硬件设计以 RFDC IP 示例设计为基础,但额外采用了 Zynq™ PS。它还涵盖了 ZCU208 的时钟选择注意事项。

Vivado™ 和 Vitis v2024.2

ZCU208

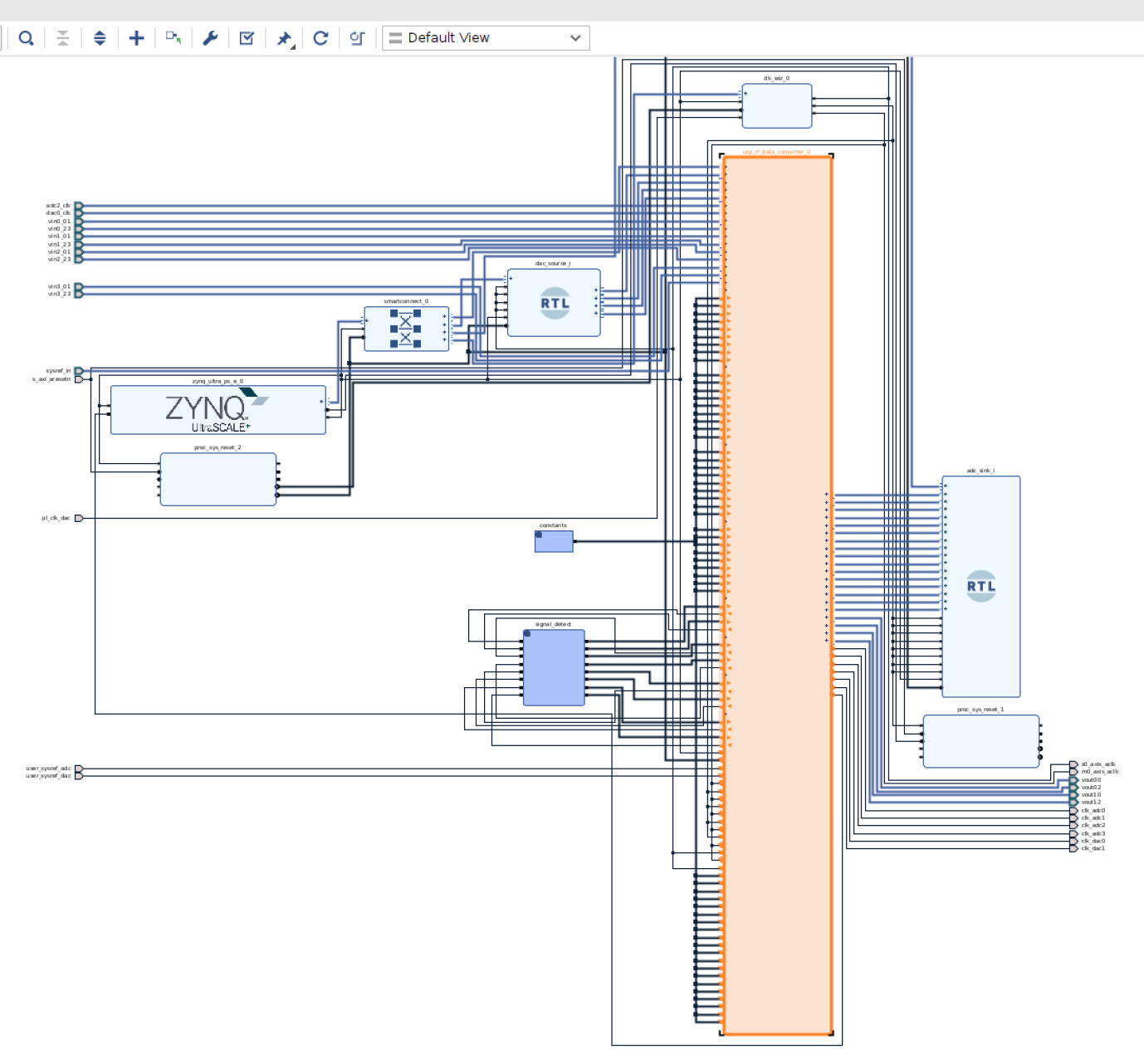

本篇博文中使用的设计以 IP 示例设计为基础。

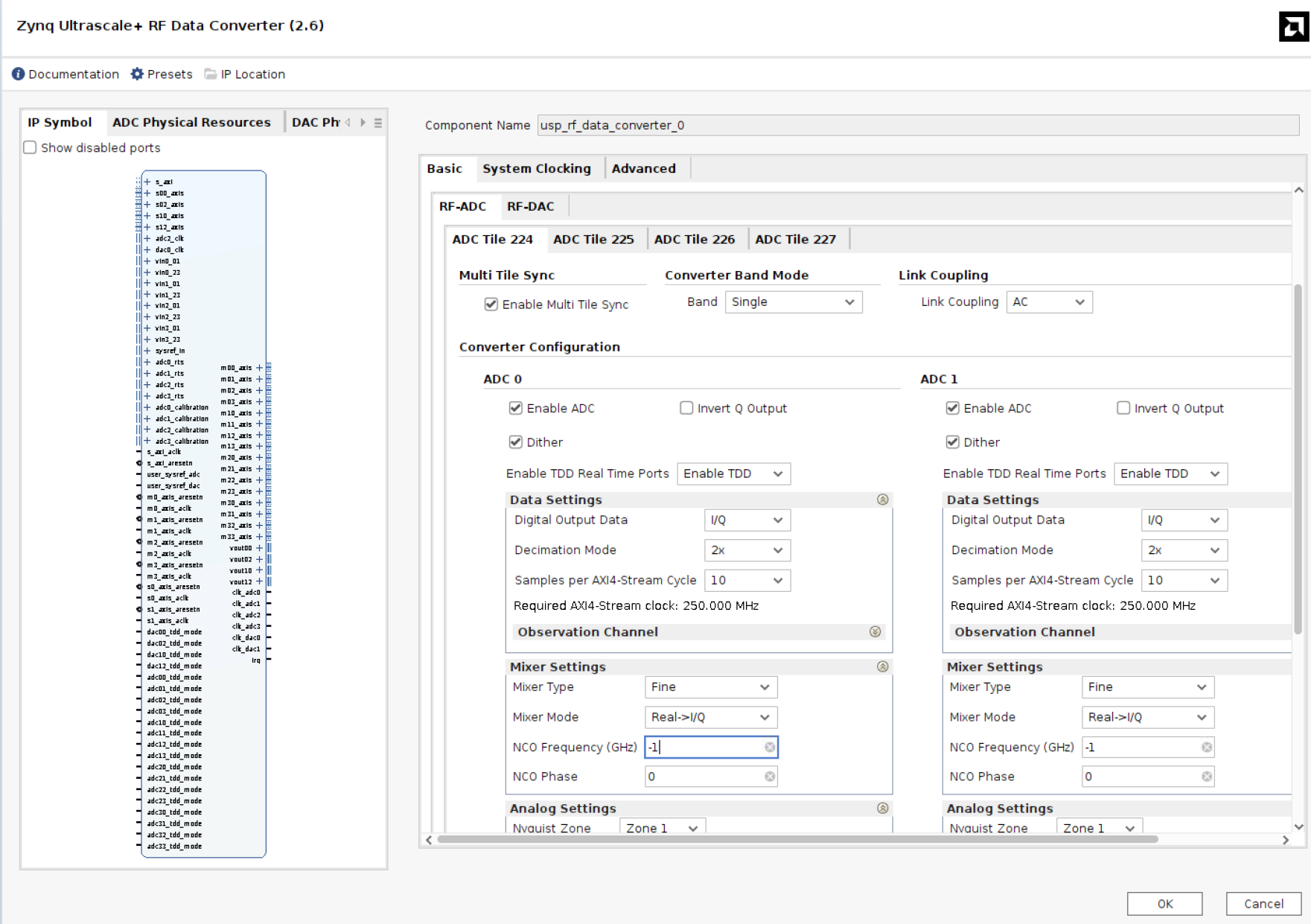

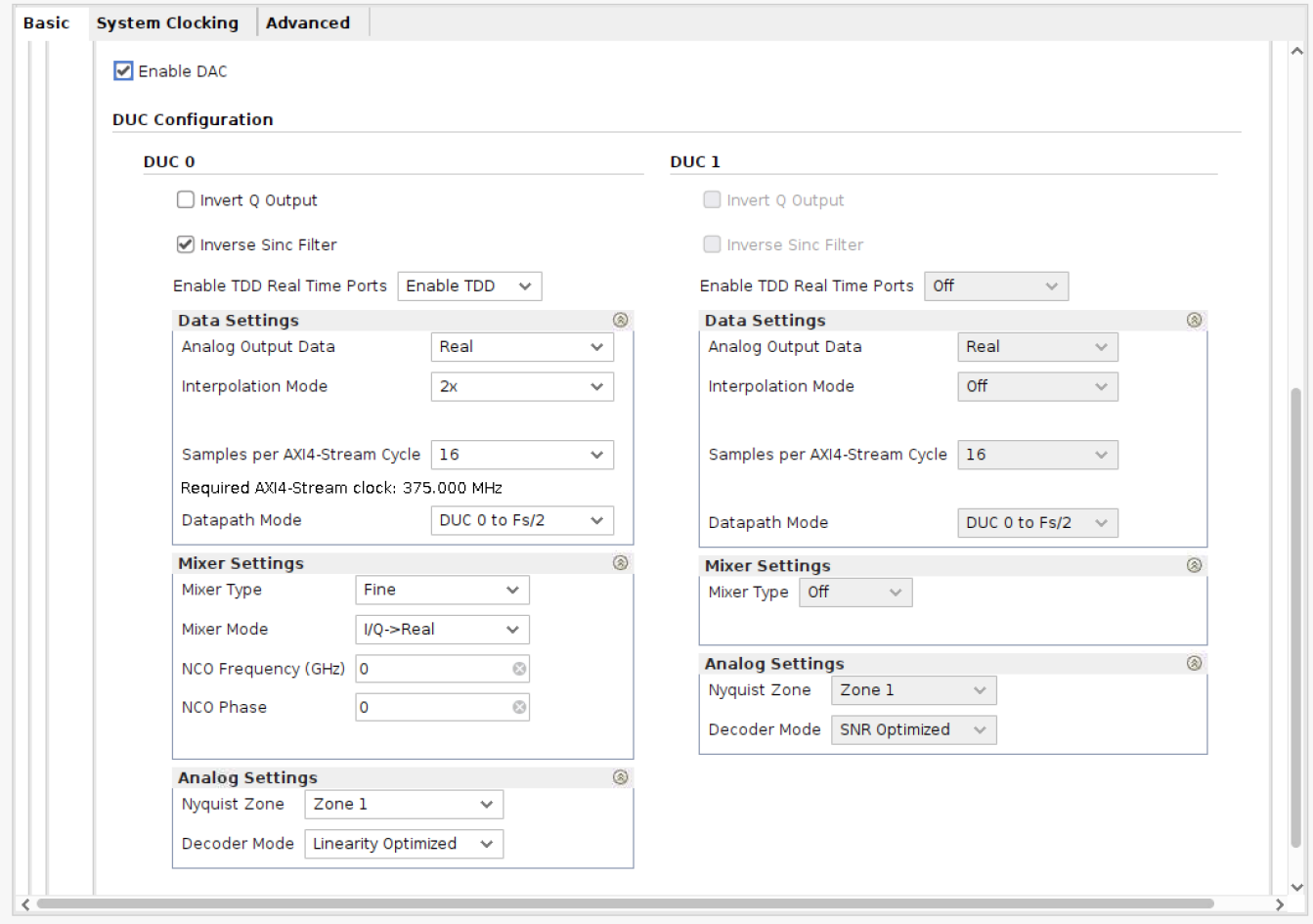

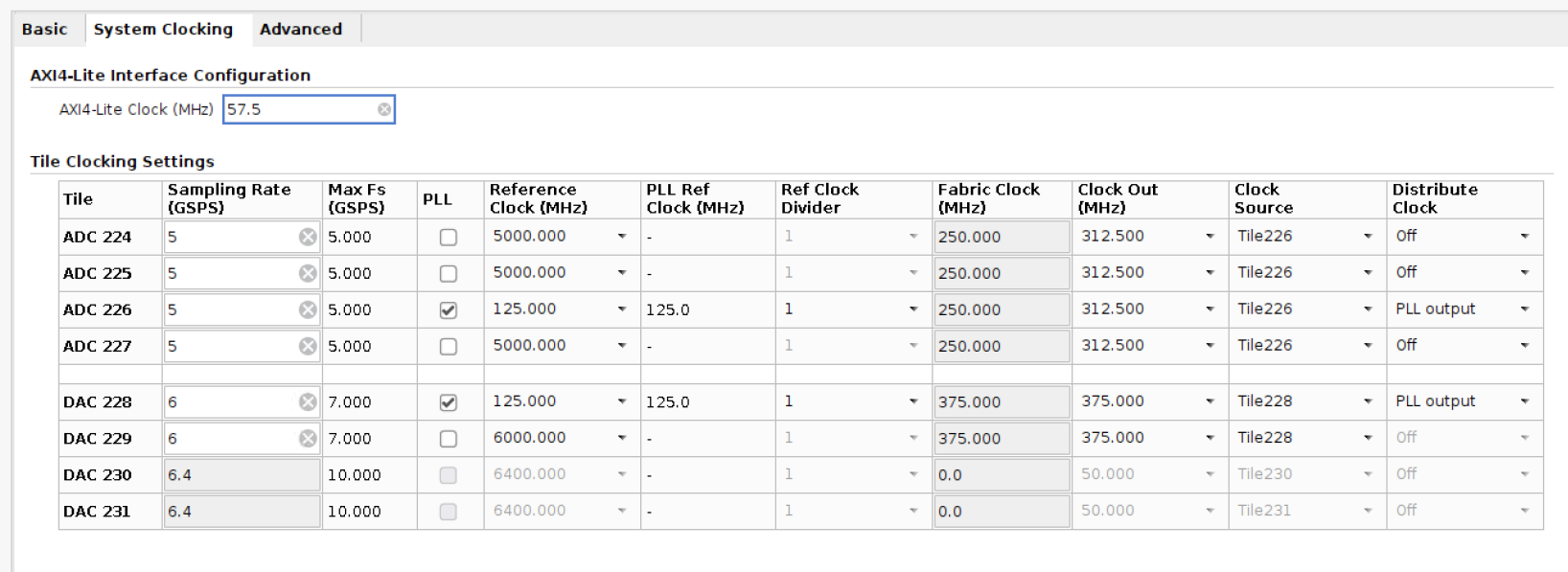

1. IP 配置:采用如下配置,启用 4 个 ADC 拼块和 2 个 DAC 拼块

2. 时钟设置:

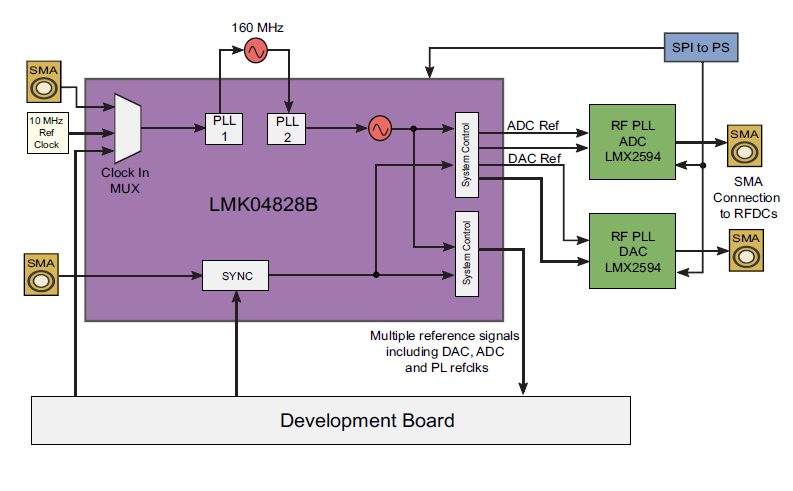

ZCU208 和 ZCU216 评估板与 CLK104 封装在一起。从功能上来看,时钟模块卡通常包含两个阶段。

第一个阶段是“LMK”时钟,其中有两个内部锁相环 (PLL),这两个 PLL 通过组合来提供流畅的无抖动时钟,该时钟是从卡上的参考时钟或者是从通过 SMA 对接的外部时钟来生成的。

第二个阶段由两个 LMX 时钟组成,其中一个用于向 RF-ADC 提供时钟信号,另一个用于向 RF-DAC 提供时钟信号。

这些第二阶段的 LMX 时钟是由 LMK 时钟直接驱动的,为 RFSoC 器件上的关联 RFDC 提供专用 RF PLL。CLK104 卡的高层次概述如下所示:

在 ZCU208 上,LMK 当前向 ADC 拼块 226 和 DAC 228 提供参考时钟。因此,时钟来自这些拼块。

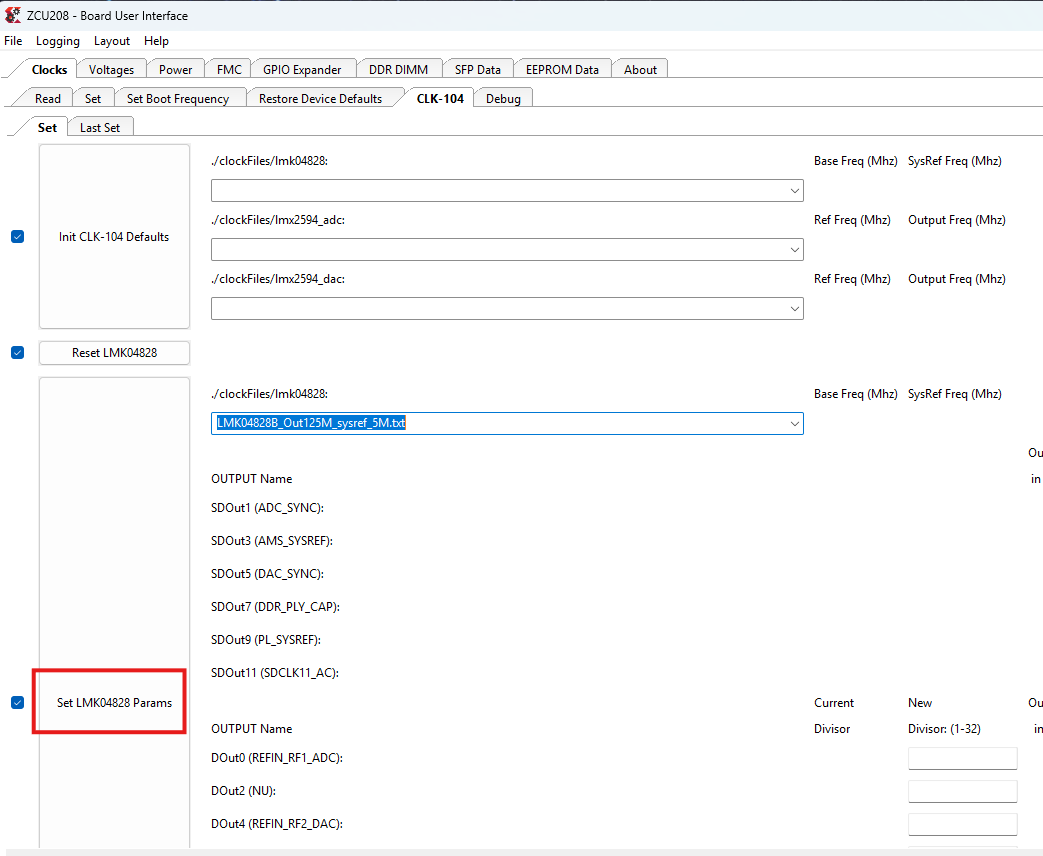

您需要先使用系统控制器来配置 LMK04828 时钟,然后再烧录 FPGA。

本篇博文随附了时钟文件 LMK04828B_Out125M_sysref_5M.txt。请将其复制到 BoardUI 安装路径 \zcu208_bit\BoardUI\tests\ZCU208\clockFiles\lmk04828 下,然后您即可在下拉列表中看到此文件

注释:拼块 228 位于边缘位置,因此无法将该时钟分配到拼块 230 和 231

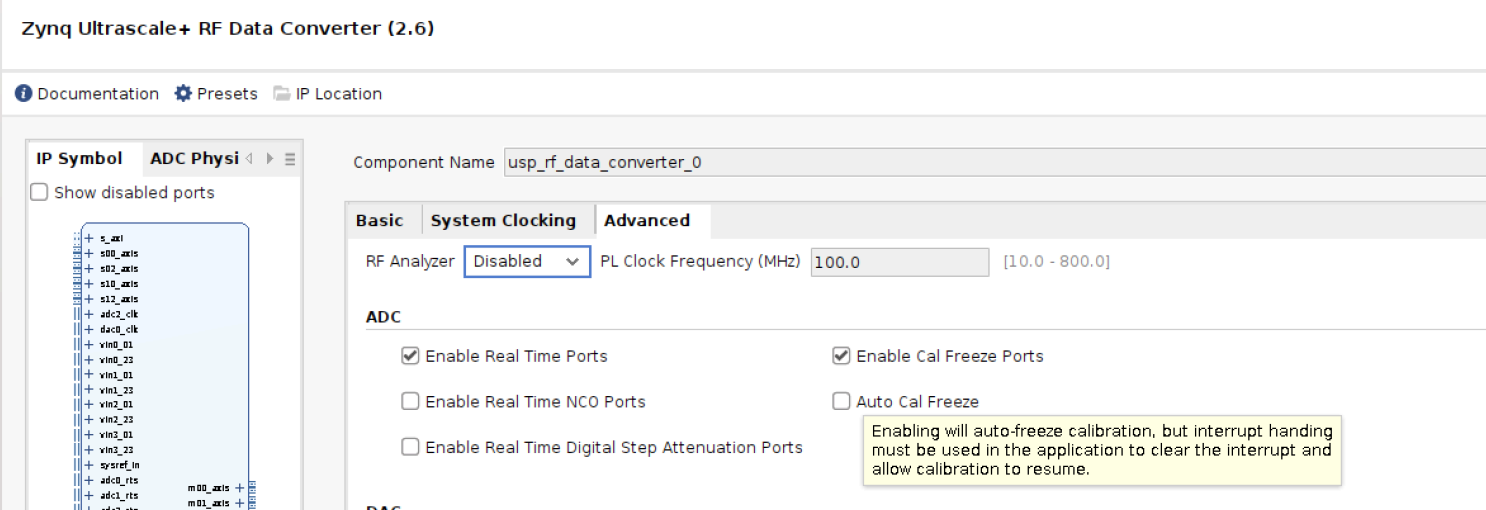

3. RF Analyzer 已禁用。如果将其启用,那么它可添加 MicroBlaze。 本篇博文需要向设计添加 Zynq™ PS,因此禁用该选项。

4. 配置完成所有设置后,请单击“OK”(确定)。然后,打开 IP 示例设计,向生成的设计添加 Zynq PS。

5. 打开 xdc 文件,添加以下约束用于 ZCU208 时钟设置:

set_property IOSTANDARD LVDS_25 [get_ports pl_sysref_p]

set_property IOSTANDARD LVDS_25 [get_ports pl_sysref_n]

set_property PACKAGE_PIN B10 [get_ports pl_sysref_p]

set_property PACKAGE_PIN B8 [get_ports pl_clk_p]

set_property IOSTANDARD LVDS_25 [get_ports pl_clk_p]

set_property IOSTANDARD LVDS_25 [get_ports pl_clk_n]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets pl_clk_BUFG]

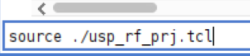

6. 或者,您可以使用 source 命令运行随附的 usp_rf_prj.tcl 来创建工程并导入必要的源文件。

7. 生成比特流,然后将硬件导出为 XSA 文件。

1. 要克服与 XFsbl_Exit 断点错误相关的已知问题,您需要将环境变量 IDE_JTAG_BOOT_MODE_FIX_DISABLE 设置为 true。

export IDE_JTAG_BOOT_MODE_FIX_DISABLE=true

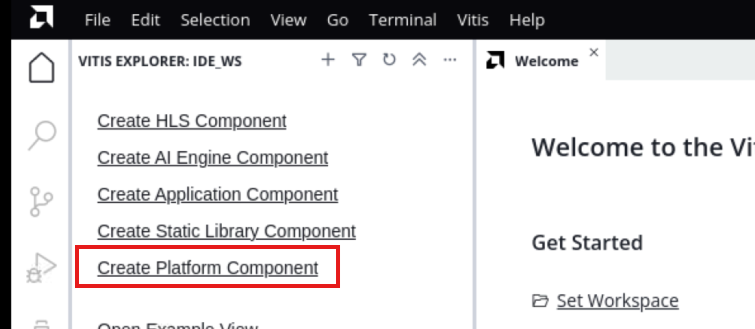

2. 启动 Vitis,设置工作空间,然后创建平台

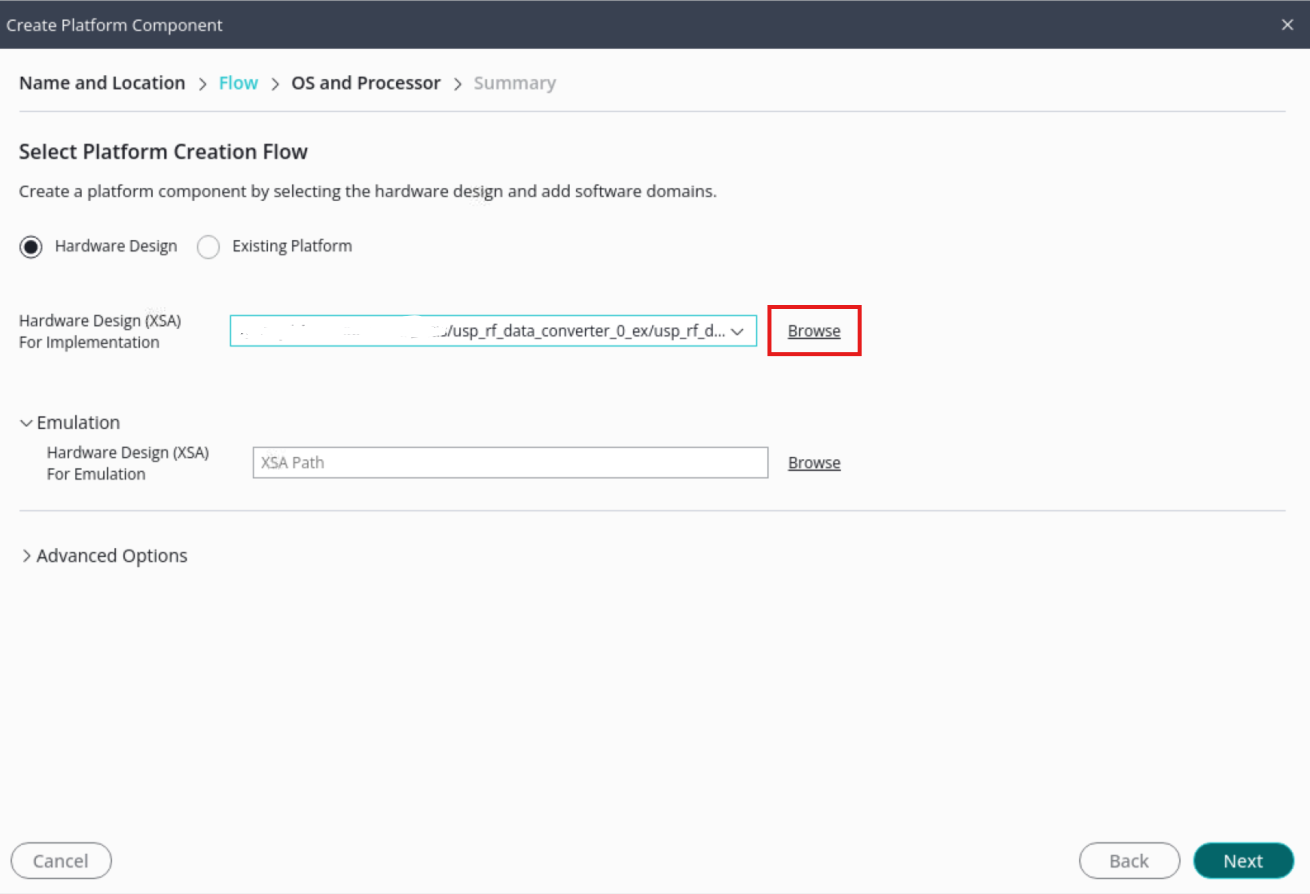

3. 在名称和位置页面中,单击“Next”(下一步),在下一个窗口中,浏览至 usp_rf_data_converter_0_ex 文件夹,然后选择在“硬件设计”部分的最后一步生成的 XSA 文件。

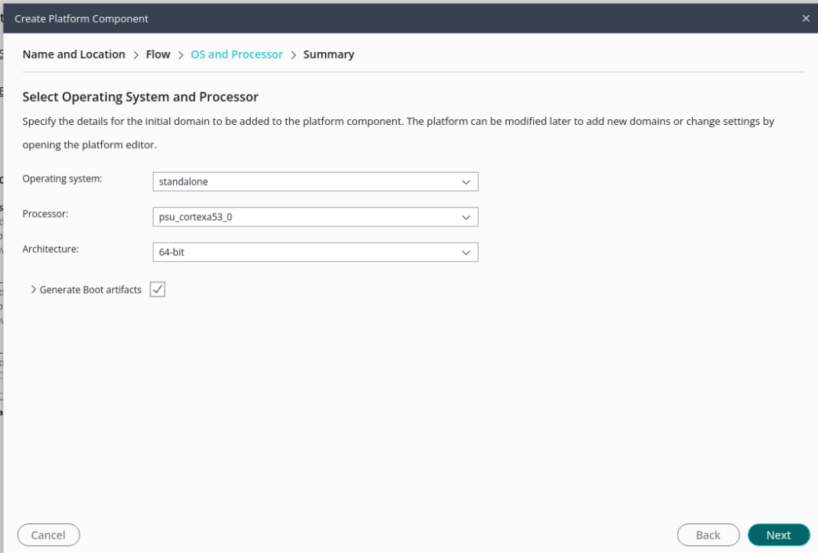

4. 保留默认选择,然后单击“Next”。

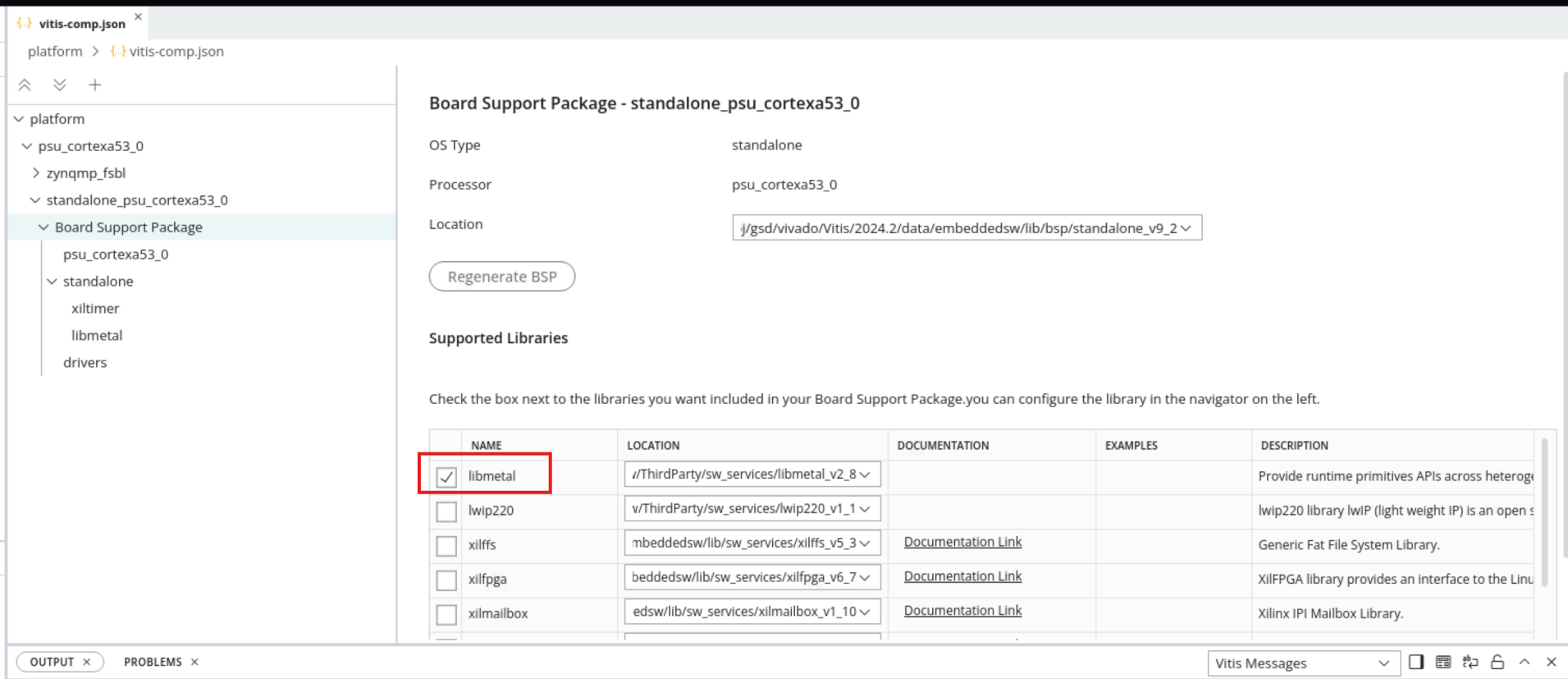

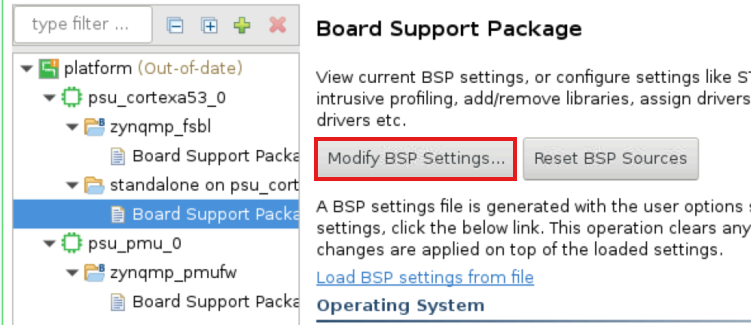

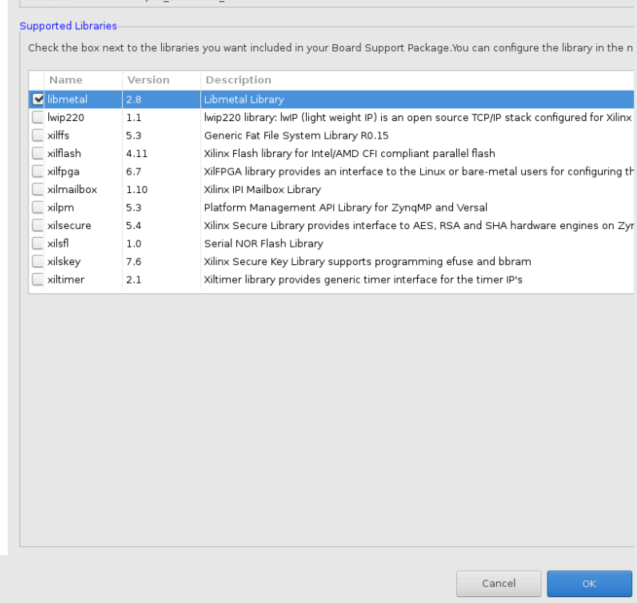

5. 创建平台后,打开 vitis-comp.json,转至板级支持包 (BSP),确保选中 libmetal。

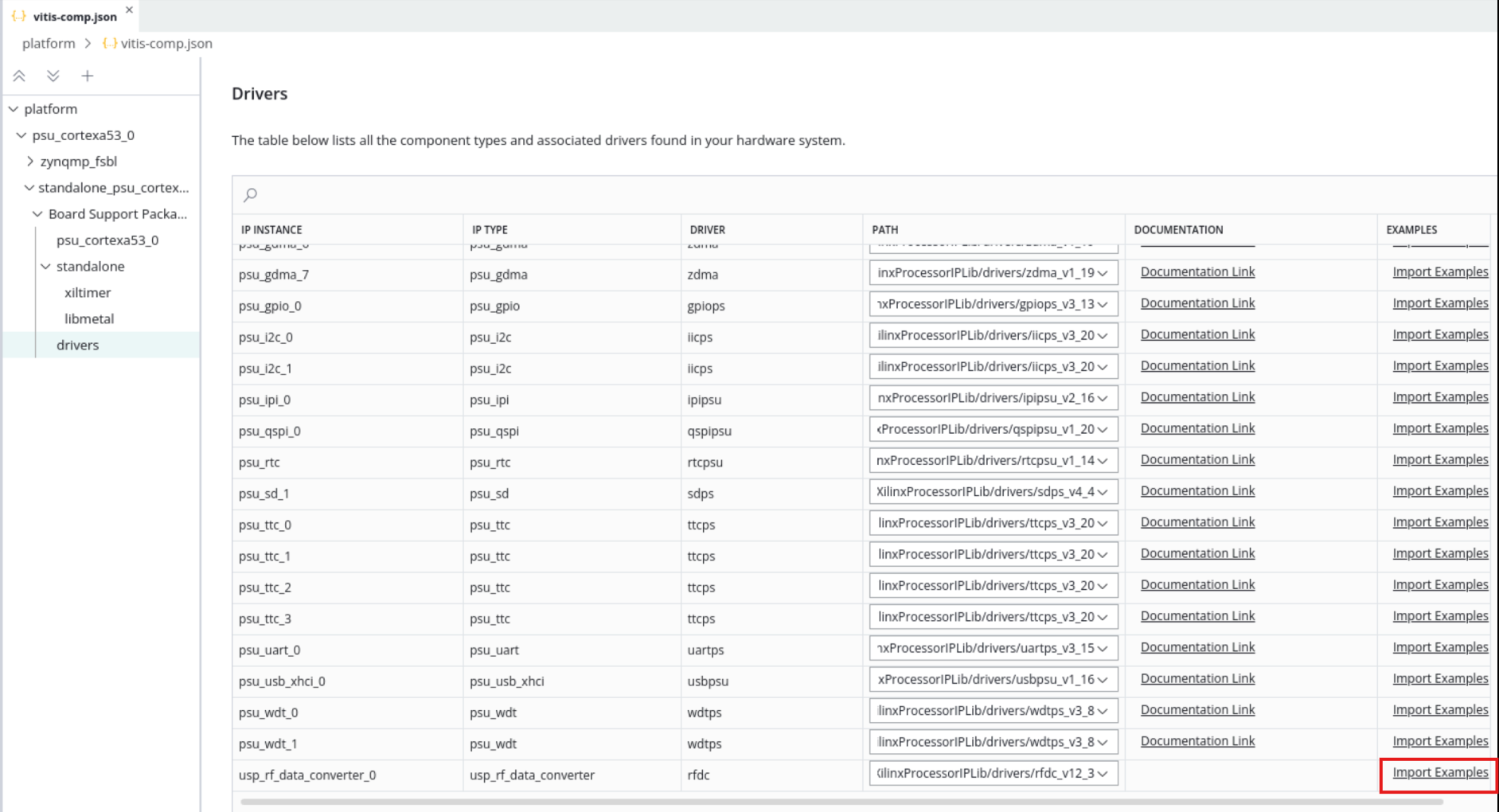

6. 在以上 JSON 文件中,选择驱动程序,然后导入 rf_data_converter 驱动程序示例。

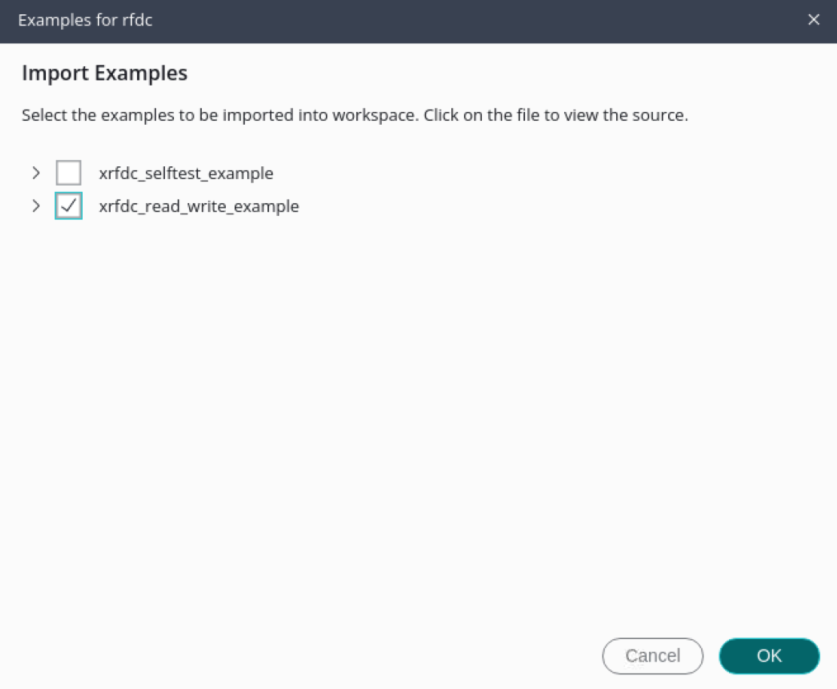

7. 选中 xrfdc_read_write_example,然后单击“OK”。它会创建一个应用工程,其中包含运行 xrfdc_read_write_example 必要的源代码。

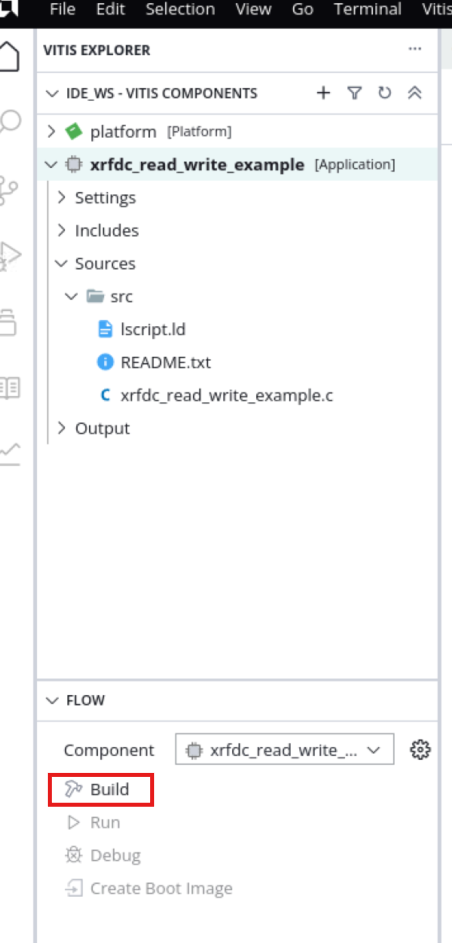

8. 然后,构建该工程,这样即可构建应用工程并生成 ELF 文件。

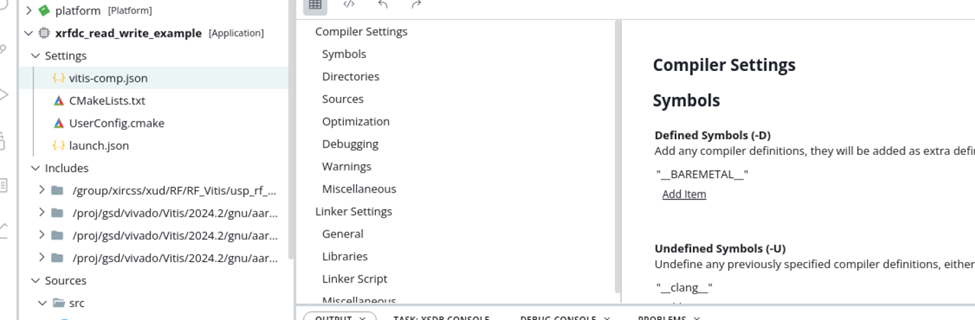

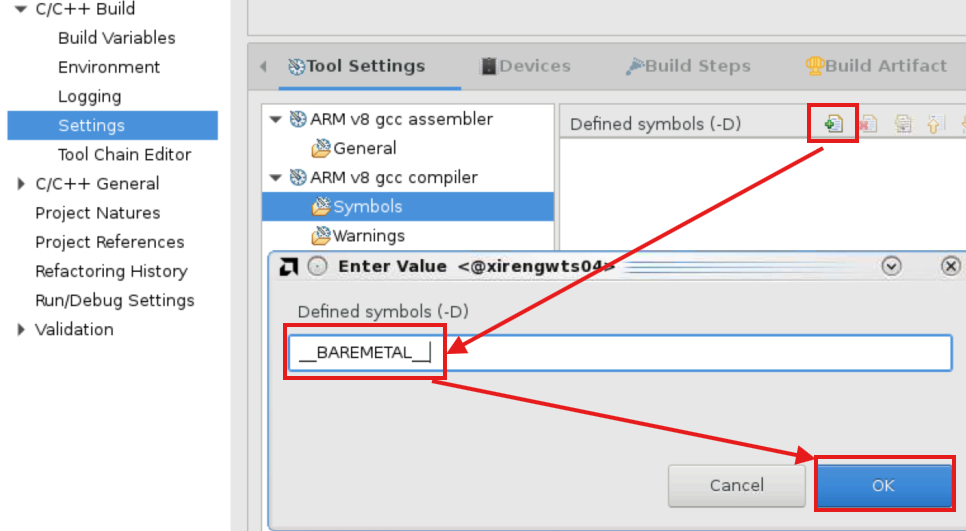

注释:在 Vitis IDE 中不需要显式定义 _BAREMETAL_。以下截屏显示了 Vitis IDE 中的符号配置,如果您想要定义其他符号,可参考此图。

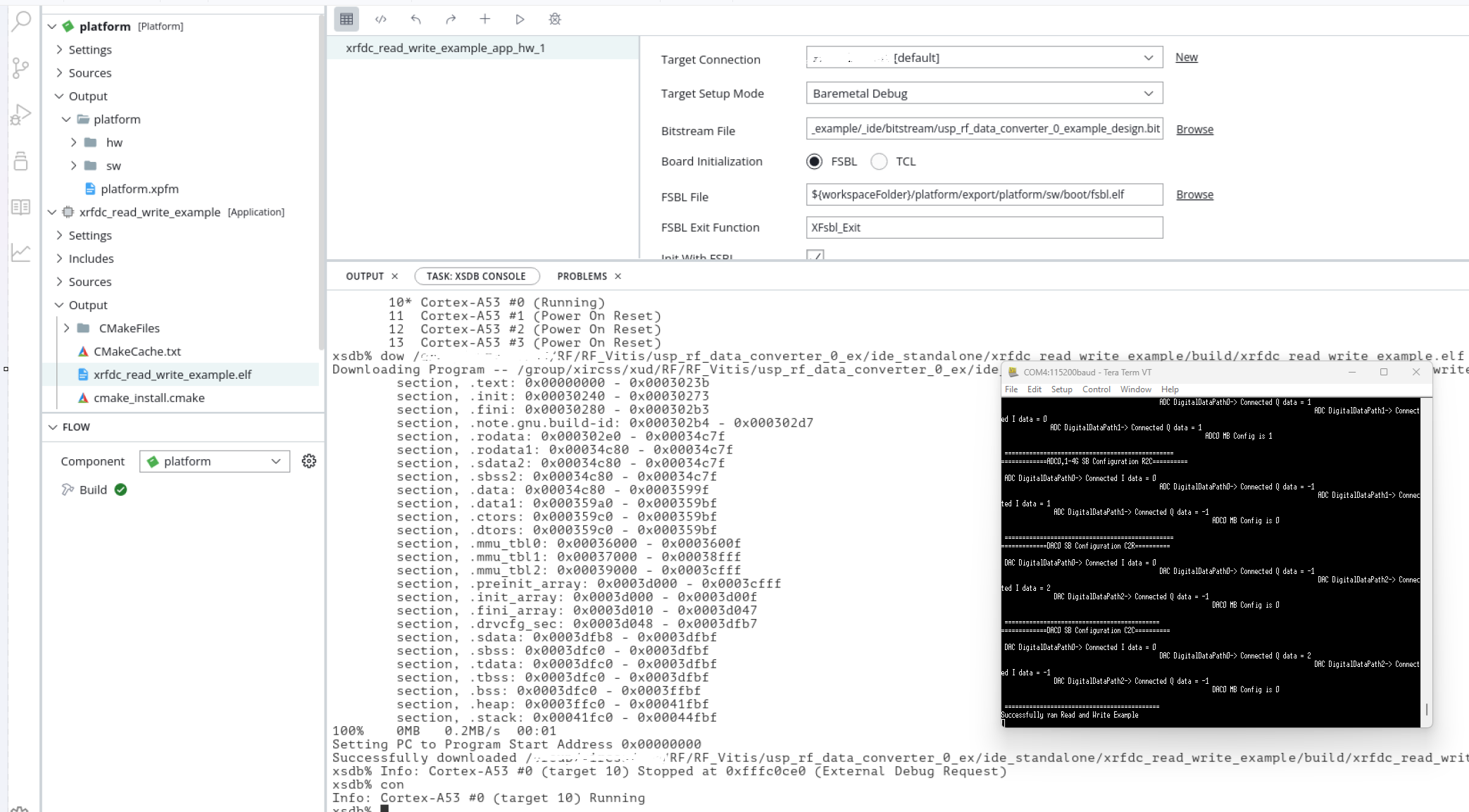

9. 连接 ZCU208 评估板,运行或调试设计。

注释:如无 IDE_JTAG_BOOT_MODE_FIX_DISABLE 变量,您可能会遇到 xFsbl_Exit 错误,您可以手动下载 ELF 文件以测试 xrfdc_read_write_example 应用。

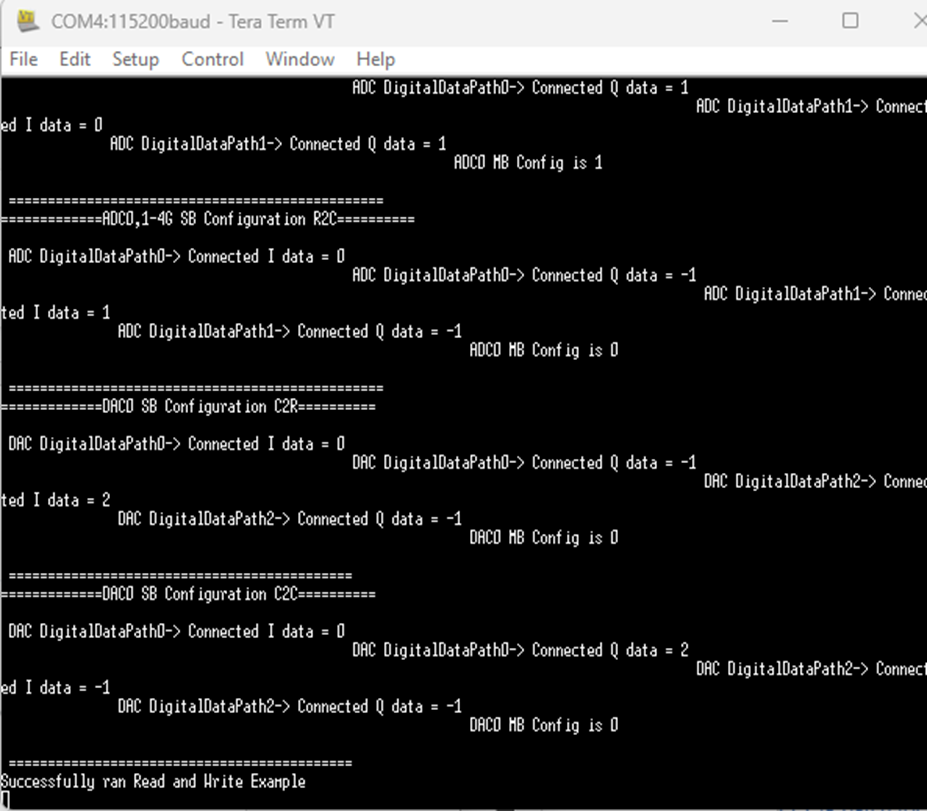

您会在终端 log 日志中看到示例运行成功的消息。

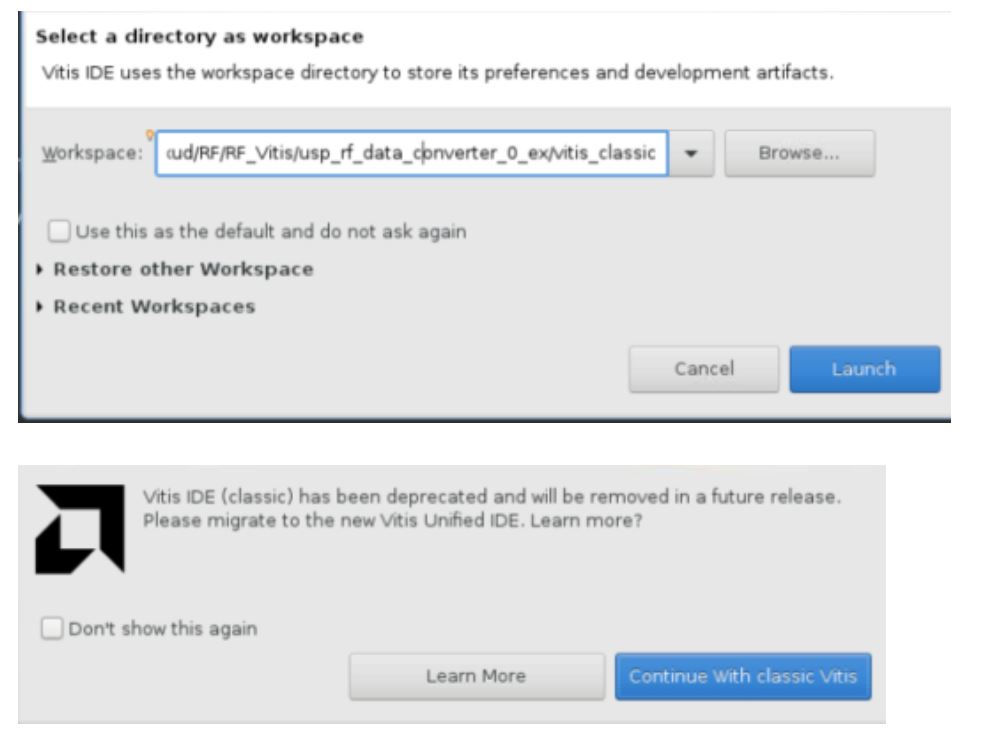

1. 使用“Vitis -classic”命令启动 Vitis,选择工作空间路径,然后继续运行传统 Vitis:

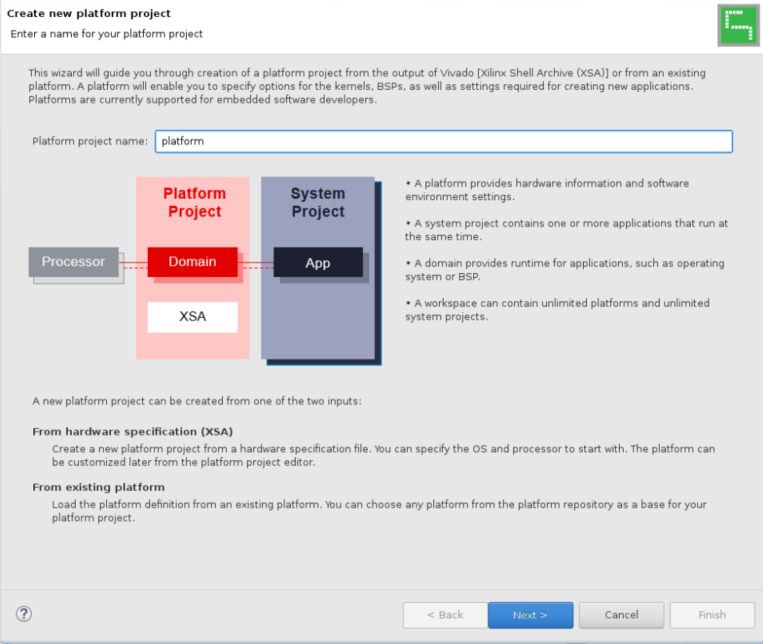

2. 依次选择“File->New->Platform Project”(文件 > 新建 > 平台工程)创建新平台,然后单击“Next”

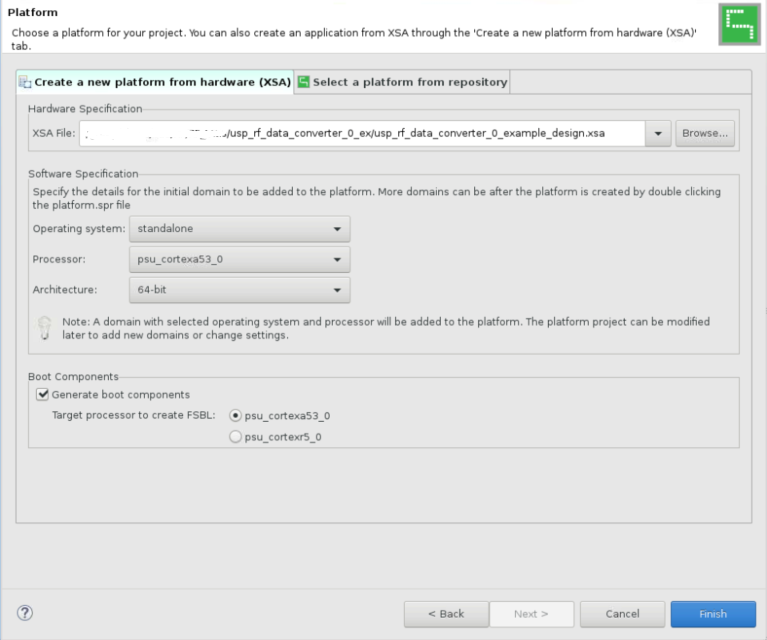

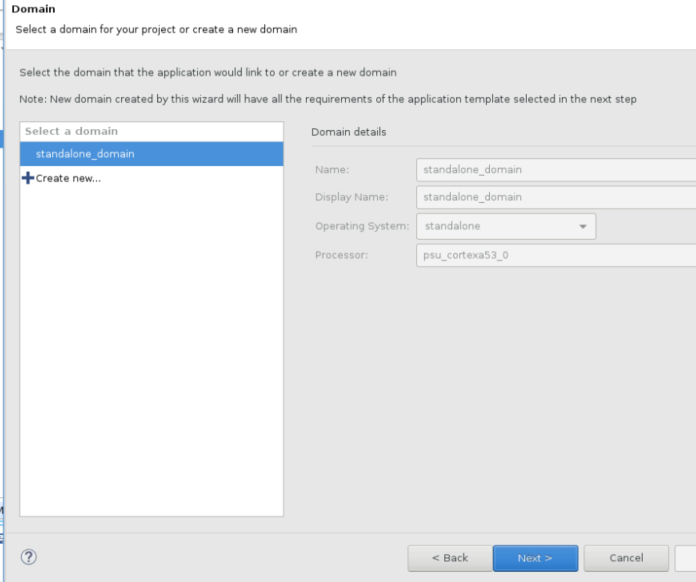

3. 选择从硬件设计生成的 XSA 文件,确保选择独立操作系统,选择 psu_cortexa53 作为处理器,然后单击“Finish”。

4. 修改 BSP 设置,勾选 libmetal,然后选择“OK”。

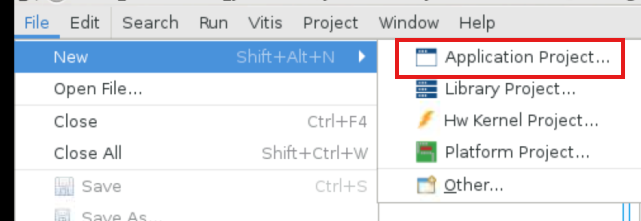

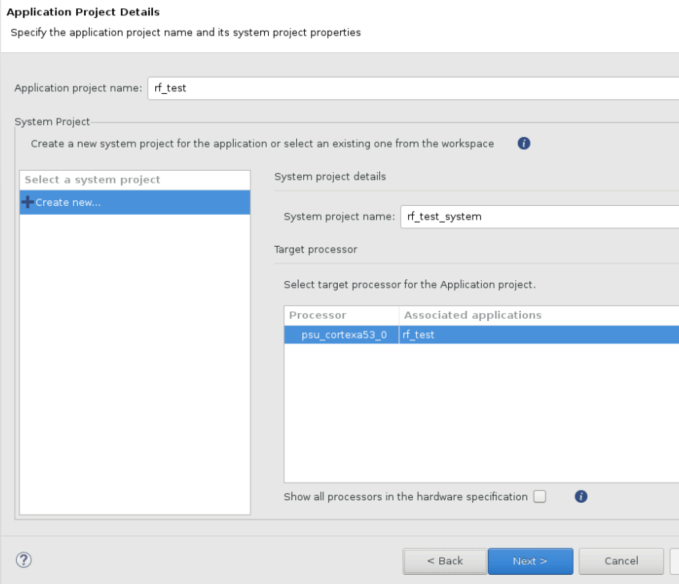

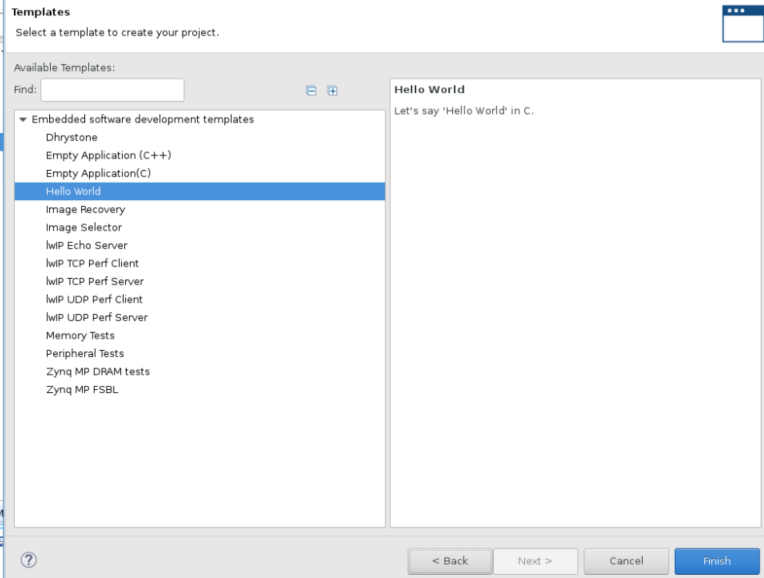

5. 使用独立域搭配“hello world”模板创建新的应用工程,然后单击“Finish”。

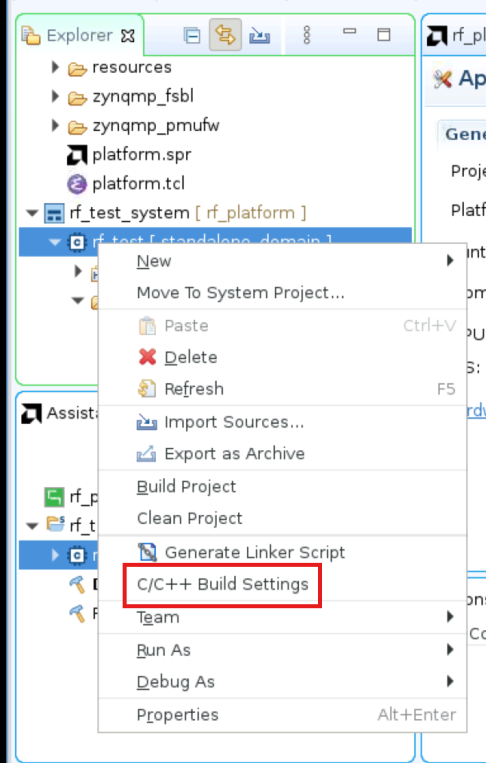

6. 手动添加“__BAREMETAL__”作为“Defined symbols”(已定义的符号)。

7. 从 https://github.com/Xilinx/embeddedsw/blob/master/XilinxProcessorIPLib/drivers/rfdc/examples/xrfdc_read_write_example.c 下载 xrfdc_read_write_example 源文件

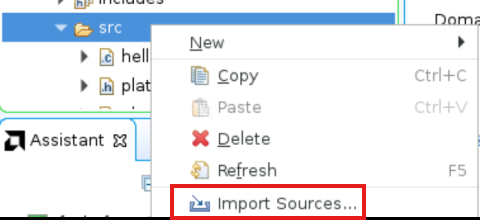

将其导入应用源代码,然后移除 helloworld.c

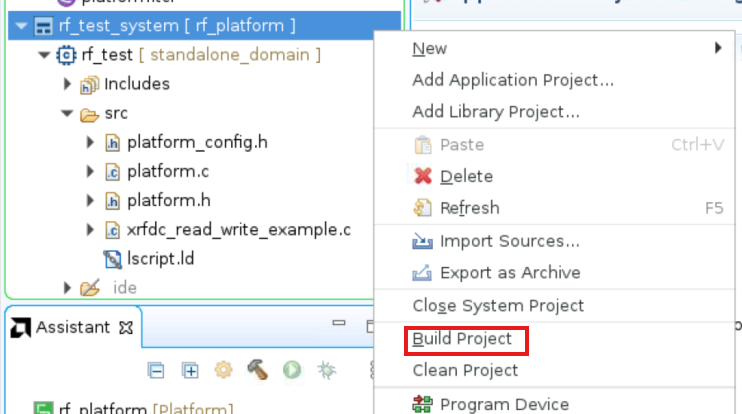

8. 构建工程

9. 连接 ZCU208 评估板,运行或调试设计。 然后,您应该可在终端 log 日志中看到示例运行成功的消息:

结论

Vitis Unified IDE 对用户更友好,它无需用户手动勾选 libmetal 库和定义 BAREMETAL 符号。

在 RFDC 驱动程序中可使用“import example”(导入示例)流程,这样即可使用自测或 xrfdc_read_write_example 来自动创建应用工程。