注意:本文所有内容皆来源于Xilinx工程师,如需转载,请写明出处作者及赛灵思论坛链接并发邮件èï¼æªç»Xilinxåèä½æ人许å¯ï¼ç¦æ¢ç¨ä½åä¸ç¨éã

Video Frame Buffer IP ç®ä»

Video Frame Buffer Read/Write IP æ¯ææ¨å°è§é¢æ°æ®ä»åå¨å¨åï¼AXI4 åå¨å¨æ å°æ¥å£ï¼è¿ç§»å° AXI4-Stream æ¥å£ï¼æåä¹äº¦ç¶ã

ä»æ´é«å±æ¬¡æ¥çï¼å®çä½ç¨ä¸æ们å¨å åè§é¢ç³»åï¼è§é¢ç³»å 24ãè§é¢ç³»å 25ãè§é¢ç³»å 26 çï¼ä¸æ使ç¨è¿ç AXI VDMA IP 并æ å·®å¼ã

é£ä¹ä¸ºä»ä¹è¦ä½¿ç¨ Video Frame Buffer IP æ ¸èä¸æ¯ AXI VDMA IP å¢ï¼

çæ¡å°±è®°å½å¨ï¼èµçµæçå¤è®°å½ 72543ï¼ä¸ãç©¶å ¶æ¬è´¨ï¼AXI VDMA IP ä» AXI4-Stream æ¥å£æååèï¼å¹¶ç´æ¥å°å ¶ç§»æ¤å°åå¨å¨ä¸ï¼æ å ³ä¹è§é¢æ°æ®æ ¼å¼ã

Video Frame Buffer å¿ é¡»å ³æ³¨ä¼ å ¥ä¼ åºåå¨å¨çæ°æ®æ ¼å¼ãæ ¹æ®æéæ ¼å¼ï¼å®è½ä»¥ä¸åæ¹å¼å°æ°æ®åå¨å¨åå¨å¨ä¸ãè¿å¯¹äº Linux åºç¨é常å®ç¨ã

æ¯å¦ï¼V4L2 æ ¼å¼ YUYV å UYVY é½è¡¨ç¤º YUV4:2:2 8 ä½ï¼å¯ä¸å·®å«å°±å¨äºä¸¤è å¨åå¨å¨ä¸çåå¨æ¹å¼ã

å æ¤ï¼å»ºè®®é对æ°è®¾è®¡éç¨ Video Frame Buffer IPã

å¦éäºè§£æå ³ Video Frame Buffer Read/Write IP ç详æ ï¼è¯·åé (PG278)ã

为 Video Frame Buffer IP çæ设计示ä¾

注æï¼ä¸ææ¯åºäº 2019.2 çæ¬ä¸æä¾ç设计示ä¾ç¼åçã

硬件 (Vivado 2019.2) 设计示ä¾

è¦çæåºç¨è®¾è®¡ç¤ºä¾ç硬件é¨å (Vivado Design)ï¼è¯·éµå¾ª (PG278) ç第 5 ç« ä¸çæ¥éª¤è¿è¡æä½ãæ¤å¤è®¾è®¡ç¤ºä¾å¯ç¨äº KC705ãZCU102ãZCU104 å ZCU106 è¯ä¼°æ¿ãå³ä½¿æ¨æ²¡æä¸è¿°ä»»æè¯ä¼°æ¿ï¼æä¹å»ºè®®ä»è®¾è®¡ç¤ºä¾å¼å§å®è·µãè¿å§ç»é½æ¯æä½³çèµ·ç¹ã

注æï¼è¦å©ç¨ Vivado WebPack 许å¯è¯çæ设计示ä¾ï¼è¯·ä½¿ç¨ ZCU104 è¯ä¼°æ¿ä½ä¸ºèµ·ç¹å¼å§æä½ã

设计示ä¾å为两ç§ãä¸ç§ç¨äº Video Frame Buffer Read IPï¼å¦ä¸ç§ç¨äº Video Frame Buffer Write IPã

æ建议使ç¨é¢å Video Frame Buffer Write IP ç设计示ä¾ï¼å 为 Video Frame Buffer Write IP å Video Frame Buffer Read IP é½åæ¬å¨å ¶ä¸ã

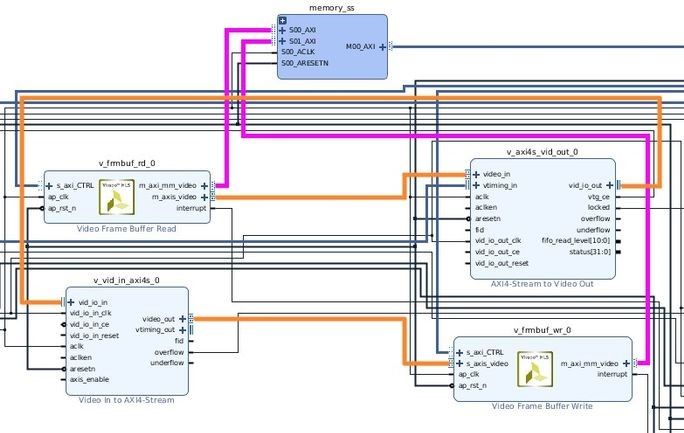

Video Frame Buffer Write IP 设计示ä¾ç硬件设计å±äºé常åºç¡æ§ç设计ã

å®ä½¿ç¨ Video Frame Buffer Read IP å°æ°æ®ä»åå¨å¨è¯»åå° AXI4-Stream æ¥å£ã

éåï¼å°å ¶è½¬æ¢ä¸ºæ¬å°è§é¢ï¼ç¶ååä½¿ç¨ AXI4-Stream to Video Out IP å Video in to AXI4-Stream IP éæ°è½¬æ¢ä¸º AXI4-Streamã

æåä½¿ç¨ Video Frame Buffer Write IP å° AXI4-Stream æ°æ®éæ°åå ¥åå¨å¨ã

æ认为对äºæ¤è®¾è®¡ï¼æ两个å¼å¾æ³¨æçè¦ç¹ï¼

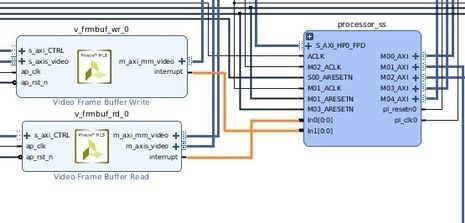

1. ä¸è¿°ä¸¤ä¸ª Video Frame Buffer IPï¼Read å Writeï¼åèªçä¸æè¾åºé½è¿æ¥å°å¤çå¨ãè¿æ¯åææ¡ä»¶ãVideo Frame Buffer æ¯åºäºä¸æç IPã

2. èè¿ä¸¤ä¸ª Video Frame Buffer IP çå¤ä½è¾å ¥åè¿æ¥è³ AXI GPIO IPãè¿ä¸ç¹è³å ³éè¦ï¼å 为å®æ¯ææ¨ä»å¤çå¨æ§è¡ IP 软å¤ä½ãå°±åææ HLS IP ä¸æ ·ï¼åªè¦å辨çæ¹åï¼å°±éè¦å° Video Frame Buffer å¤ä½ã

åºç¨ç¤ºä¾ (Vitis 2019.2)

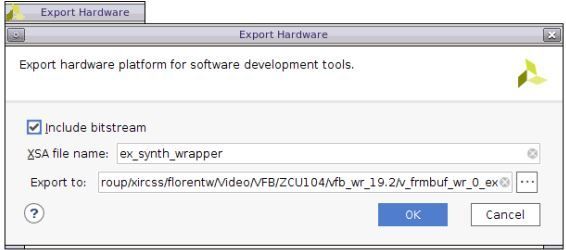

è¦çæåºç¨ç¤ºä¾ï¼å¨ Vivado ä¸ï¼é¦å å°ç¡¬ä»¶å¯¼åºè³èµçµæ Vitisï¼ä¾æ¬¡åå» File > Export > Export Hardware â¦ï¼ã

ç¡®ä¿å¨å¯¼åºç硬件ä¸å å«æ¯ç¹æµãè¿å°å建ä¸ä¸ª XSA æ件ã

å¯å¨èµçµæ Vitis 并éæ©è¦ç¨ä½ä¸ºå·¥ä½ç©ºé´çç®å½ã

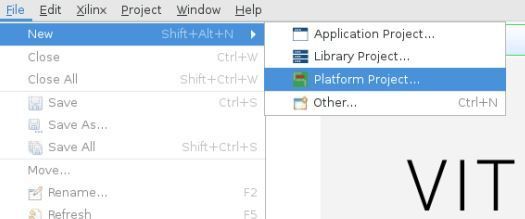

å¨ Vitis ä¸ï¼åå» New > Platform projectã

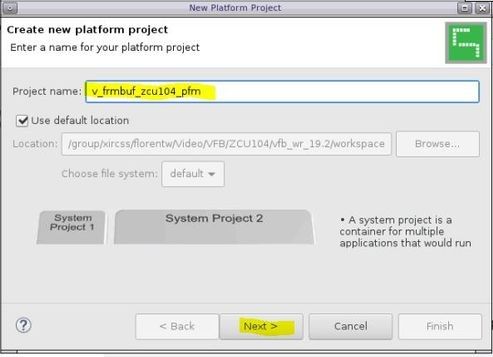

è¾å ¥æ¨æéçå¹³å°å称ï¼ä¾å¦ï¼v_frmbuf_zcu104_pfmï¼ï¼ç¶ååå» Nextã

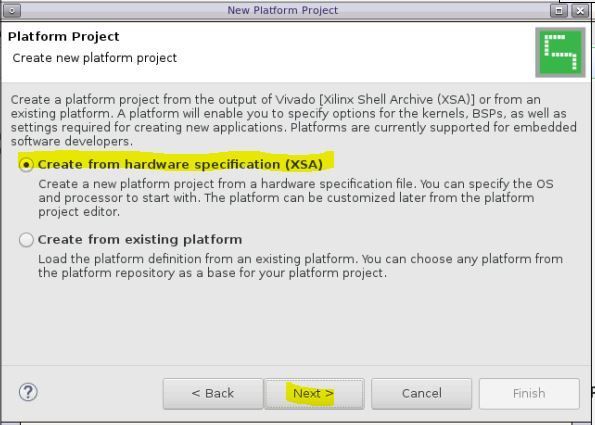

ç¡®ä¿éä¸ Create from hardware specification (XSA)ï¼ç¶ååå» Nextã

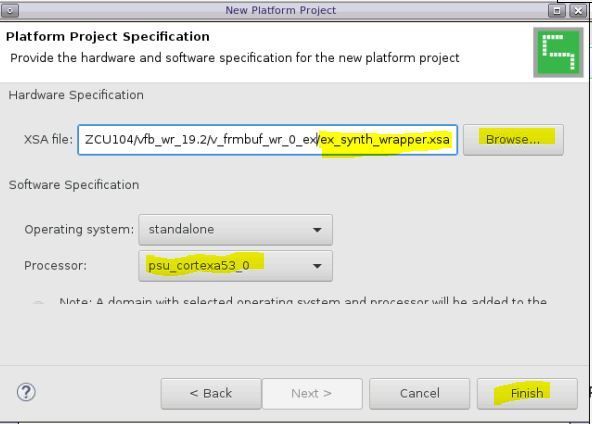

éæ©ä» Vivado 导åºç XSA æ件ï¼ç¡®ä¿å·²éä¸ A53 å¤çå¨ï¼ç¶ååå» Finishã

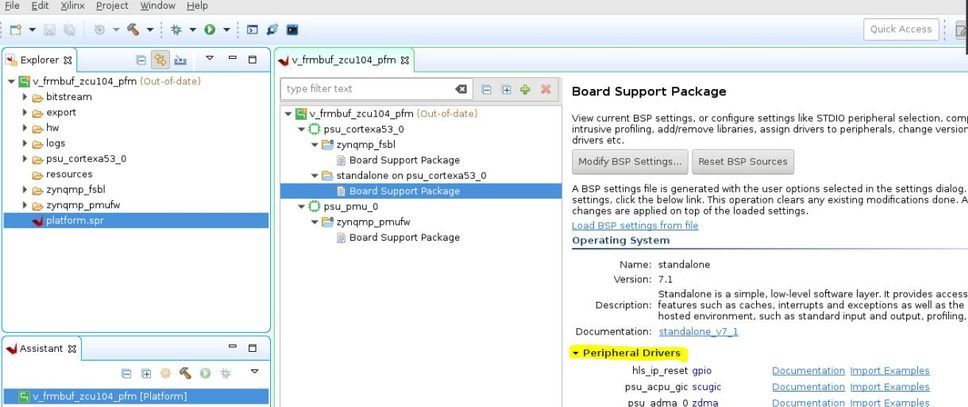

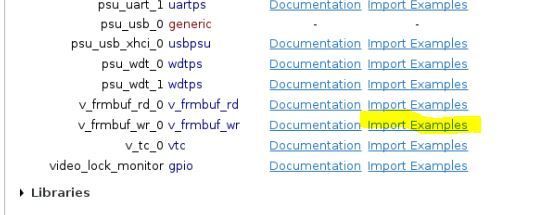

å建平å°åï¼åå» psu_cortexa53_0 > standalone on psu_cortexa53_0 ä¸ç Board Support Packageï¼ç¶åå±å¼ Peripheral Drivers é¨åã

å¨ Peripheral Drivers ä¸ï¼æ¥æ¾å¯¹åºäº Video Frame Buffer Write (v_frmbuf_wr) çè¡ï¼ç¶ååå» Import Examplesã

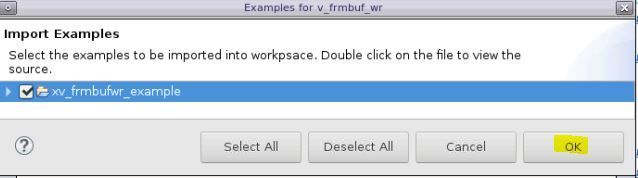

éæ©ç¤ºä¾ (xv_frmbufwr_example)ï¼ç¶ååå» OKã

è¿è¡åºç¨ç¤ºä¾

注æï¼ä»¥ä¸æ¥éª¤åå®è¯ä¼°æ¿å·²ä¸çµå¹¶ä¸å·²éè¿ UART è¿æ¥ï¼BOOT 模å¼å¼å ³å·²è®¾ç½®ä¸º JTAG 模å¼å JTAGï¼å¹¶ä¸å·²æå¼ UART ç»ç«¯ï¼å¦ Tera Termï¼ä¾æ£ç¡®ç COM 端å£ä½¿ç¨ã

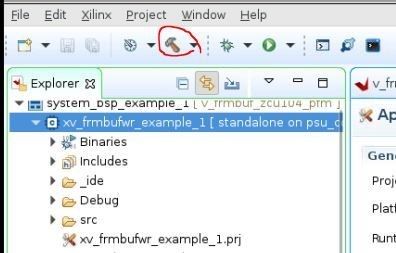

åå»åºç¨å¹¶åå»é¤åå¾æ 以æ建åºç¨ï¼

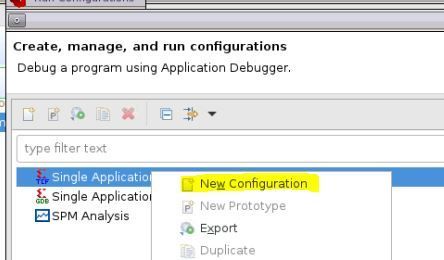

è¦å¨ç¡¬ä»¶ä¸å¯å¨åºç¨ç¤ºä¾ï¼è¯·å³é®åå»è®¾è®¡åºç¨ç¤ºä¾ï¼å¹¶åå» Run As > Run Configurationsâ¦

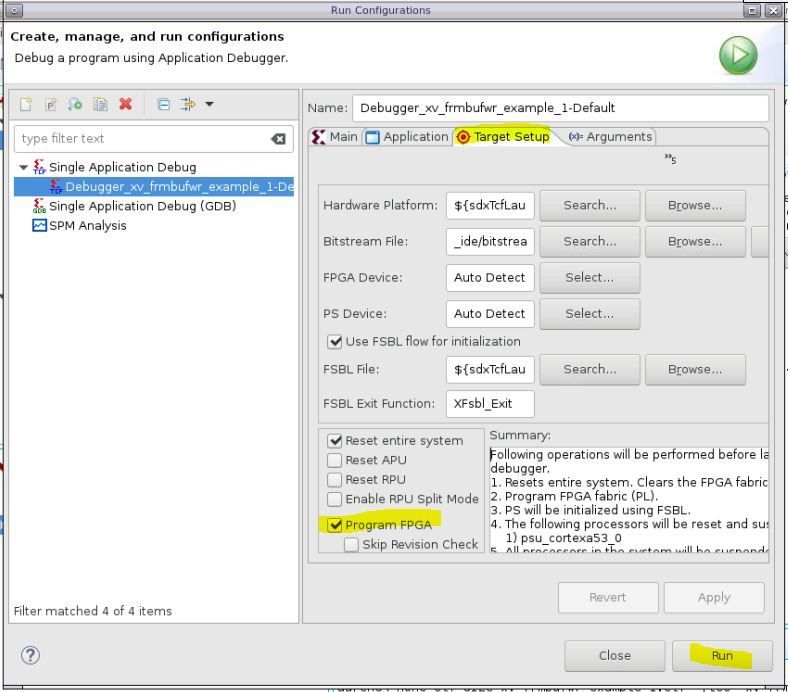

å¨ Create, manage, and run configurations çªå£ä¸ï¼å³é®åå» Single Application Debugï¼ç¶ååå» New Configurationã

å¨é ç½®çªå£ç Target Setup é项å¡ä¸ï¼ç¡®ä¿å·²å¯ç¨ psu_initï¼å¦æå¨ ZCU102ãZCU104 æ ZCU106 è¯ä¼°æ¿ä¸è¿è¡ï¼å Program FPGAï¼ç¶ååå» Runã

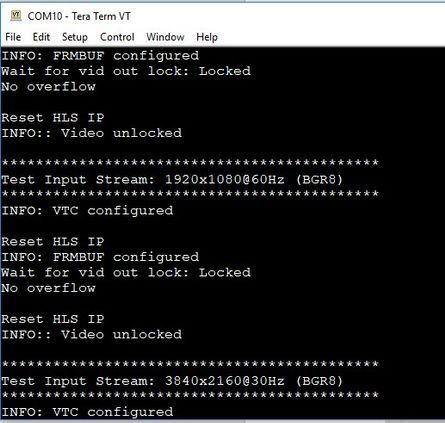

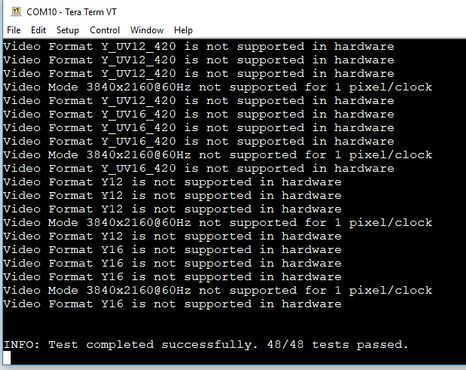

å¨ UART ç»ç«¯ä¸ï¼å¯ä»¥çå°æ¤åºç¨æ£å¨å°è¯ä¸åçè§é¢å辨çåè²å½©ç©ºé´ç»åã

å¨åºç¨è¿è¡ç»ææ¶ï¼å¯è½ä¼æ¾ç¤ºé¨åæµè¯å¤±è´¥çåå ï¼ä¸»è¦åå æ¯ç¡¬ä»¶é ç½®ä¸æ¯æï¼ã

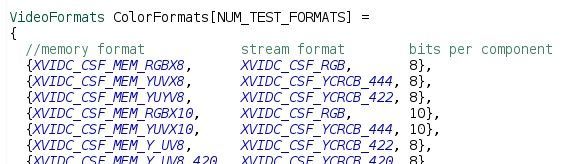

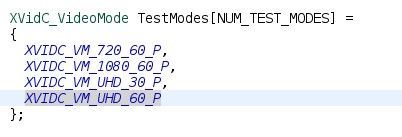

è²å½©ç©ºé´åè§é¢å辨çå¨åºç¨ä¸ä»¥ ColorFormats å TestModes ç»ææ¥å®ä¹ã

å¦æè¦åå°æµè¯çè²å½©æ ¼å¼æ°éï¼æè å¦æè¦æ¹åæµè¯çè§é¢å辨çï¼å¯ä»¥æ´æ¹è¿äºç»æ

æ³ä»è¿ä¸ªè§é¢ç³»åä¸è·å¾æ´å¤ä¿¡æ¯ï¼

å¦éæ¥æ¾ä»¥åçææè§é¢ç³»åï¼è¯·ç¹å»èµçµæè§é¢ç³»å

æ¥æºï¼èµçµæ论å