作者:Yin Chaowen,AMD工程师;来源:AMD开发者社区

1. 关于Clock Phase Shift

1)时钟相移对应于相对于参考时钟的延迟时钟波形,这是由于时钟路径中的特殊硬件而导致的。在 AMD FPGA 中,当 MMCM 或 PLL 原语的输出时钟属性 CLKOUT*_PHASE 非零时,通常会引入时钟相移。

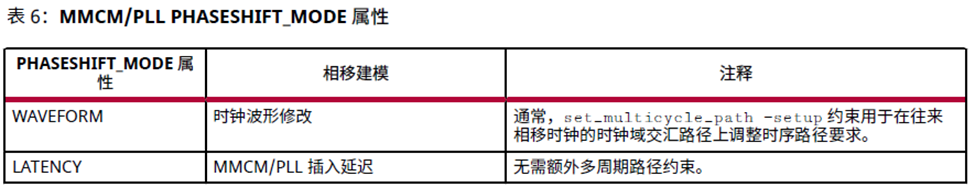

2)MMCM/PLL Phase Shift Modes:

时序分析期间,可通过设置 MMCM/PLL PHASESHIFT_MODE 属性以两种不同方式对时钟相移进行建模,如下表中所述。

各 AMD FPGA 系列所采用的默认 MMCM/PLL 时钟相移模式不尽相同。但用户可基于 PLL/MMCM 覆盖默认模式。

重要提示!MMCM/PLL PHASESHIFT_MODE 属性不影响器件配置。它仅影响静态时序分析引擎的裕量计算。由于在 WAVEFORM/LATENCY 模式间可能需要调整时序约束,由此导致工具 QoR 也会受到影响。

重要提示!在任意 CLKOUTx 管脚上定义管脚相移并有多个时钟到达 MMCM/PLL 的输入管脚时,

PHASESHIFT_MODE=LATENCY 模式无效,并触发“Warning Timing 38-437”警告。在此类情况下,MMCM/PLL 应配置为使用 PHASESHIFT_MODE=WAVEFORM 模式。

2. 示例

1) 示例1:PHASESHIFT_MODE 设置成WAVEFORM模式

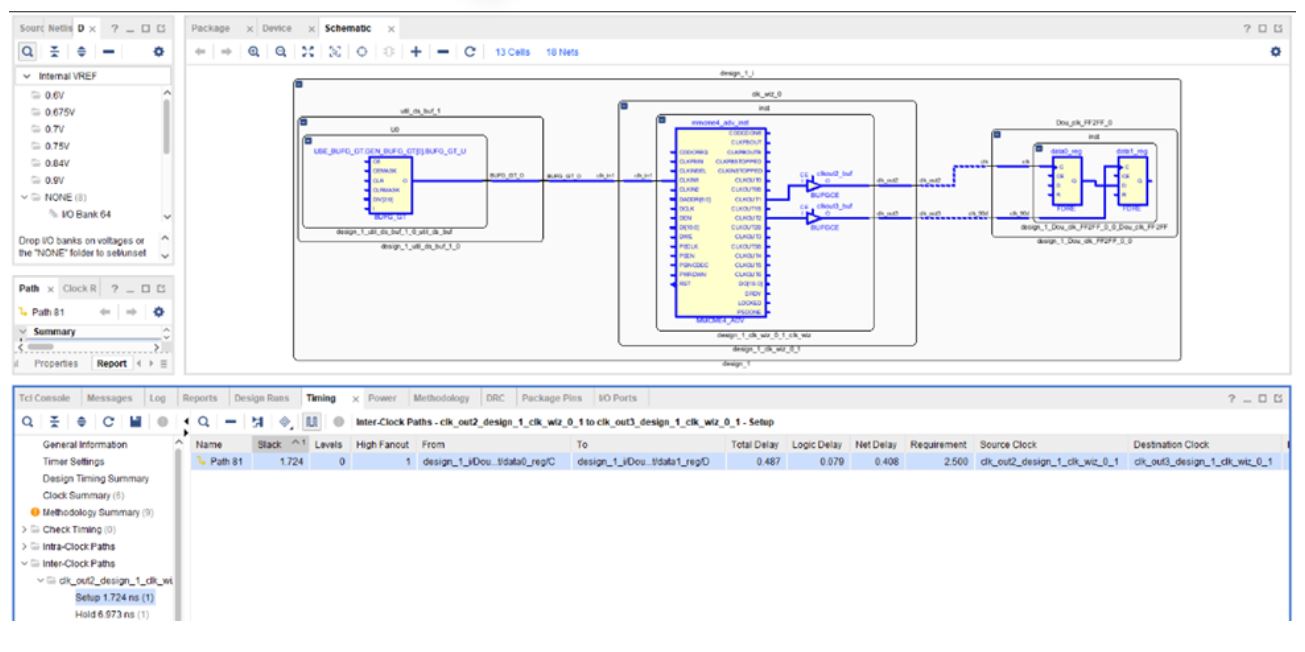

如下图所示,MMCM输出两个时钟clk_out2和clk_out3,同样都是100M,clk_out3落后的90°,也就是2.5ns的延时。

下面展示一个clk_out2到clk_out3的FF->FF的时序路径。

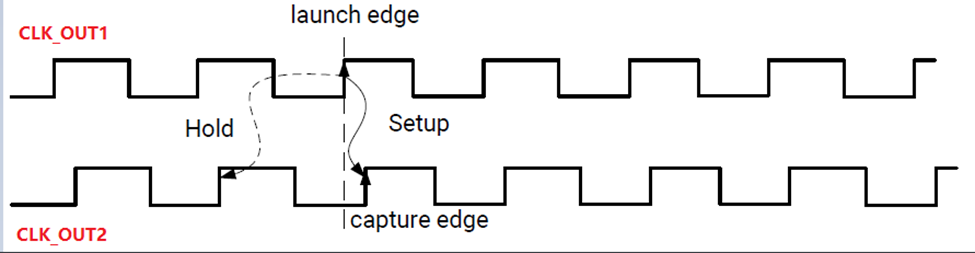

不加multicycle的约束情况下,默认的时序分析关系如下图:

所以默认的状态下整个Hold 的requirement就是特别宽松,而Setup relation就变成了上面的90°移向对应的2.5ns的requirement,这个setup requirement =2.5ns显然给QoR引起了大的挑战。从下图的时序报告中可以看出,Setup的Slack比HOLD小很多,Setup的requirement为2.5ns。这里因为使用了测试工程,整个资源非常小,所以Setup也收敛了,但是资源多或者时钟频率高的情况下很容易因为不合理的Setup Requirement造成不收敛。

这里完全可以使用如下的约束,注意get_pins后面的名称需要根据实际修改:

set_multicycle_path 2 -setup -from [get_pins design_1_i/Dou_clk_FF2FF_0/inst/data0_reg/C] -to [get_pins design_1_i/Dou_clk_FF2FF_0/inst/data1_reg/D]

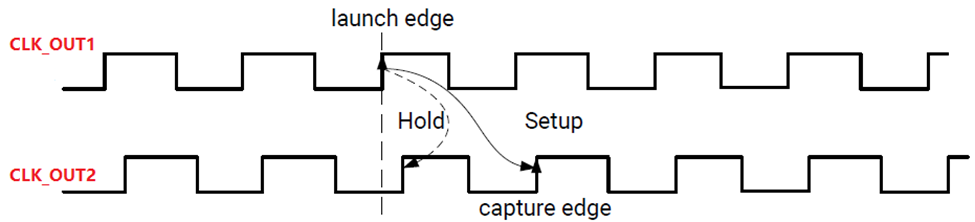

来放宽对Setup 要求的同时HOLD的挑战也不是那么大。设置完成了之后可以看到对应的Setup和Hold 关系如下图,设置好约束重新run后的Timing报告也附在下面:

从Timing报告可以看出,Setup 和Hold的Requirement变成了预设的样子,Requirement变成了12.5ns和2.5ns:

所以如上面的手册说的当MMCM、PLL的 PHASESHIFT_MODE 设置成为WAVEFORM的时候通常需要 设置set_multicycle_path 约束来达到时序收敛的结果。

2) 示例2:PHASESHIFT_MODE 设置成LATENCY模式

通常将MMCM、PLL的Phase Shift Mode修改成LATENCY。就不需要添加额外的set_multicycle_path约束。所以这里把上面的set_multicycle_path约束移除了。

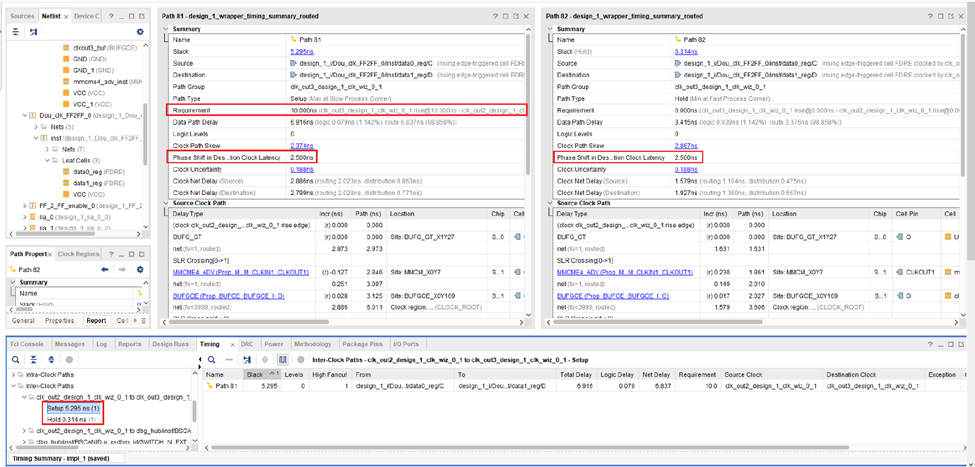

下面我们看下LATENCY模式下默认生成的时序报告:可以看到与WAVEFORM的方式是不一样的,这里把时钟的偏移单独记了一个LATENCY。STA计算的时候额外引入了一个延时值。

3. 小结

在两个时钟之间引入偏差以满足时序时,使用 PHASESHIFT_MODE=LATENCY 尤显便利。将时钟相移设置为负值、空值或正值时,调整时序路径要求无需额外的多周期路径约束。