作者:Duoqiang Liu 来源:FPGA算法工程师

早期的通信系统使用数字信号处理器IC来产生kHz带宽的基带信号,所有的RF调制(以及随后的RF滤波和RF放大等)都是使用离散模拟组件进行的。RFSoC平台可能是最先进的现代无线通信平台,可以使用FPGA可编程逻辑内核生成GHz的带宽信号,这意味着上变频、滤波、数字预失真(DPD)甚至射频载波调制都可以通过数字方式进行。在这种射频直采中,仅剩的模拟级是RF滤波和RF放大。

根据通信系统的发展过程,本文将介绍几种常见的中射频设计方案。

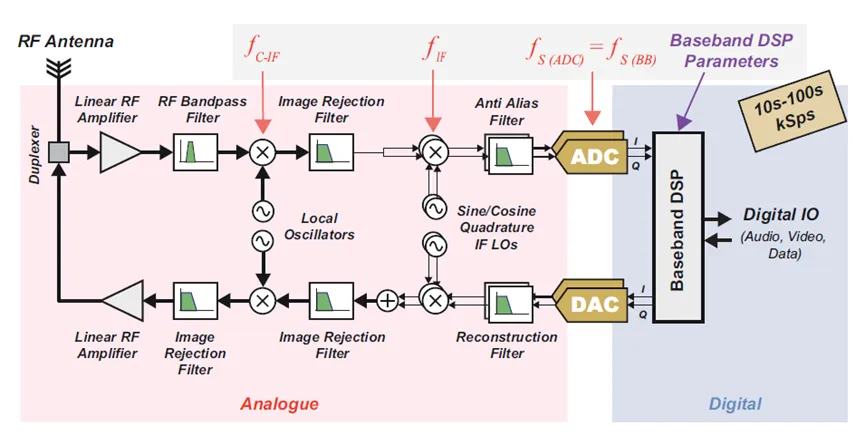

1.基带采样/模拟中频基带采样(1990s)

早在20世纪90年代末,运行在100 ksps的16位分辨率的A/D转换器是最新的(也是相当昂贵的)技术。如图1和2所示,在这些第一代“数字无线电”中,模拟部分使用模拟本振(LO)将来自RF载波的信号分一级或两级进行下变频。如图2所示的两级版本,具有中频(IF)级,并使用第二个模拟LO进一步将中频信号下变频到基带(即Edwin Armstrong为FM Radio开发的超外差架构)。从历史上看,由于DAC和ADC技术的限制(特别是可实现的采样率),这些方法被用于A/D接口的唯一可行位置。

然后对基带信号进行采样并使用ADC进行数字化,并使用DSP操作执行最后的处理阶段以恢复传输的信息。20世纪90年代的第二代移动电话——那些接收GSM信号的——很可能使用了这种架构。

图1:基带采样架构

图2:模拟中频基带采样架构

2.数字中频采样(2000s)

随着A/D接口的采样速度逐渐增加到MSps范围,下一代数字无线电看到采样和数字化过程在中频而不是基带进行。例如,40MHz左右的IF可以由采样频率为125MHz的ADC支持。该架构的第一级DSP涉及使用直接数字下变频器(DDC)通过解调和抽取滤波将中频信号转移到基带,如图3所示。一旦信号到达基带,就进行进一步的DSP处理。在这个架构中,在数字领域实现了更多的功能,为无线通信系统提供了更大的灵活性。

图3:数字中频采样架构

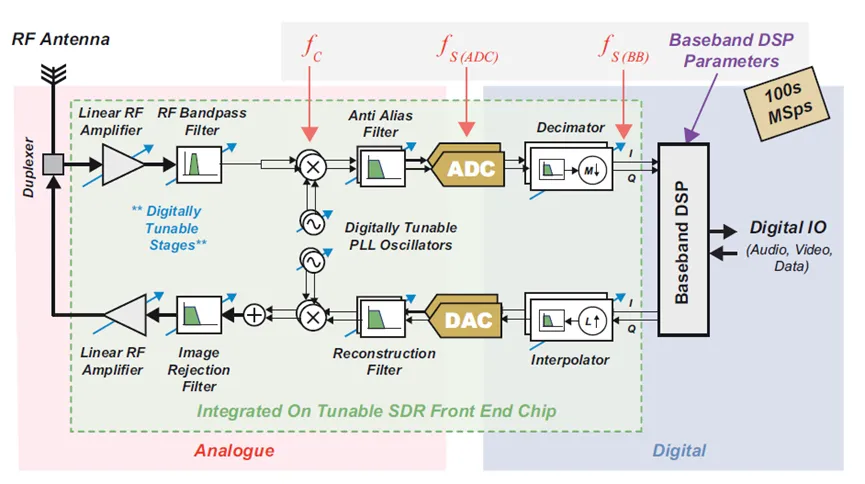

3. 具有可调谐射频的基带采样 (2010)

随着SDR的应用越来越广泛,IC制造商开始开发单芯片SDR前端,将一些模拟和数字阶段结合在一起;为模拟振荡器、滤波和放大器级带来数字/软件可调性,如图4所示。这使得SDR更加灵活,并首次能够在更宽的频率范围内工作。A/D接口现在能够达到100MSps的采样率,将可实现的基带信号带宽增加到10MHz;这意味着SDR可以用于我们日常使用的流行无线电标准的原型设计和实现,比如Wi-Fi和LTE。

图4:具有可调谐射频的基带采样架构

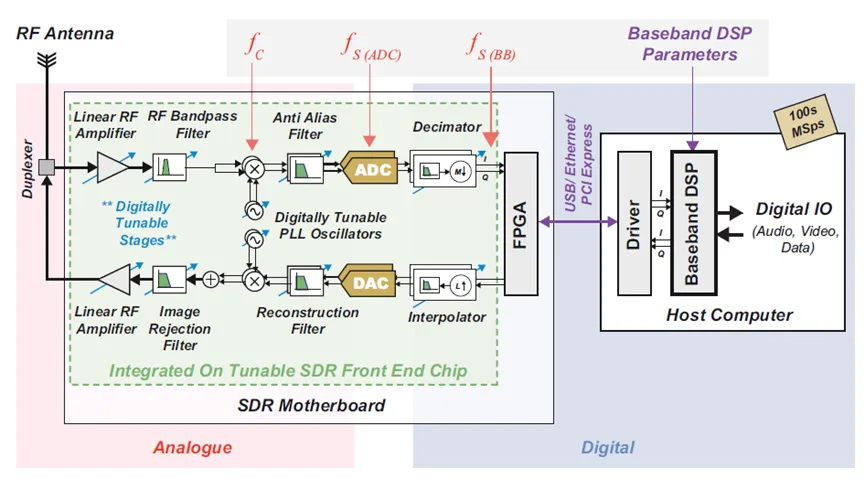

到2010年,通用计算机也变得更加强大,具有更高的CPU时钟速度和更大的RAM。专用DSP或FPGA硬件不再需要实现SDR系统的最终DSP操作。这些可以在主机上的软件(如MATLAB或GNU Radio)中实现。为了将SDR前端芯片与计算机连接,SDR主板上需要USB、Gbit以太网和PCI Express等接口。FPGA作为计算机接口与SDR前端芯片之间的互连集线器,如图5所示。

这两个重大的进步首次将SDR市场向更广泛的社区开放——爱好者、专业消费者和学生研究人员——因为以前SDR解决方案实际上只用于高级研究和军事应用。规模经济将SDR收发器硬件的成本降低到1000美元以下,SDR革命真正开始了。这些无线电类型的例子包括USRP™B210(相当于图5所示的“SDR主板”)和Zynq SDR(基于AMD Zynq的开发板(如ZedBoard™)和第三方SDR前端的组合)。

图5:带可调谐射频的基带采样SDR的系统级实现

我们现在已经达到了可以以多Gsps速率运行A/D转换器的阶段,这意味着几乎全数字无线电可以用于越来越多的频段。最终,已经采取了直接采样RF信号的措施,如图6所示,随后使用DSP在单级中将它们从RF频率下变频到基带。2018年,随着Gen 1 RFSoC的推出,该架构首次以完全集成的形式实现。第三代将于2022年发布,能够以高达10 Gsps的速率进行采样。

几乎全数字的射频直采只需要很少的模拟处理——主要是前端RF滤波器和RF放大器。从SDR的角度来看,几乎所有功能都是数字化实现的这一事实非常重要——这意味着无线电的操作可以被控制,甚至可以在运行时使用软件动态更新,如图6所示。虽然许多(但不是全部)5G网络正在使用直接射频SDR前端,但我们可以预期,在未来的6G实现中,所有无线电都将采用这种形式。

图6:射频直采架构

除上述的SDR平台外,实际上如今的4G、5G等基站设备,普遍采用基带采样或数字中频采样,通过CPRI、JESD204B等接口将基带板与射频板连接起来。

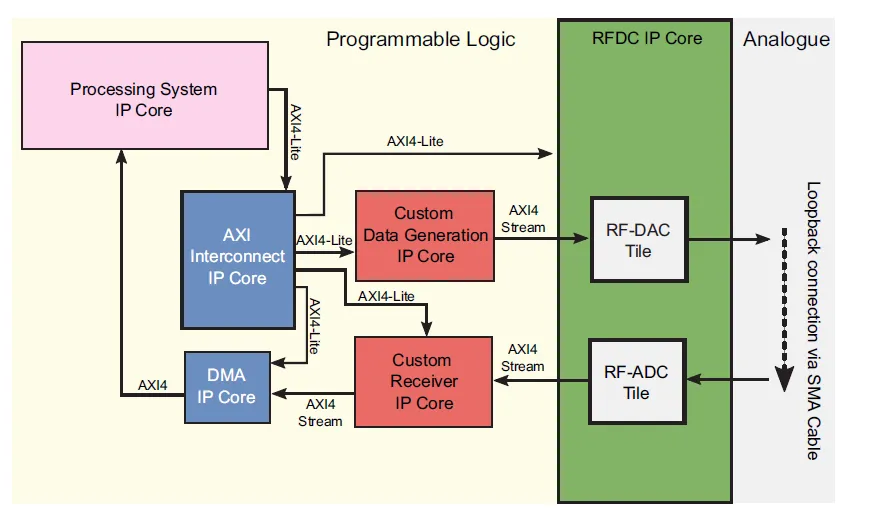

Xilinx推出的RFSoC则通过DFE部件,直接完成射频直采,不再通过JESD204B等接口而是通过AXIS接口进行传输。

图7 :IP集成的SDR设计

对于轻量级SDR设计而言,软件可以完成协议栈和物理层基带部分的处理,中射频部分再通过RFSoC进行硬件设计实现。

需要注意的是,如果是做商用基站产品,这种RFSoC架构却不一定适合实际应用场景。一体化基站当然可以作为一种选择,但板载的PS处理器几乎不可能完成复杂的协议栈处理,以及部分物理层功能的实现。

每一种射频架构都有各自的优劣,需要考虑信号带宽、AD/DA采样率、滤波器、中心频点等具体的设计。