2024年10月18日,无锡亚科鸿禹电子有限公司宣布正式加入甲辰计划,加速推动国产RISC-V生态建设与产业创新。

亚科鸿禹是国产数字前端仿真验证EDA工具研发与应用的先驱者,见证着国产芯片产业的起伏迈进,与RISC-V产业生态演进有着深厚渊源。亚科鸿禹加入甲辰计划旨在进一步发挥团队在芯片前端验证调试EDA领域的技术优势,联合更多RISC-V生态伙伴,加速国产RISC-V调试验证EDA工具链开发应用、积极赋能国产RISC-V技术成果普及落地及应用模式创新。

亚科鸿禹RISC-V产品及解决方案

定制化硬件仿真加速验证方案

硬件仿真加速器兼具大规模验证容量和指数级仿真加速等优势,在架构验证、系统级仿真、回归测试等全场景仿真验证中扮演着重要角色。亚科鸿禹桌面级硬件仿真加速器--HyperSemu Emulator,实现快捷部署、性能优越、流畅易用、成本友好等创新突破,使得众多中小开发项目能够受益于硬件加速验证技术的前沿发展。基于丰富的开发应用实践,HyperSemu为现代SoC设计提供定制化加速验证解决方案,支持RISC-V、ARM内核的CPU验证。

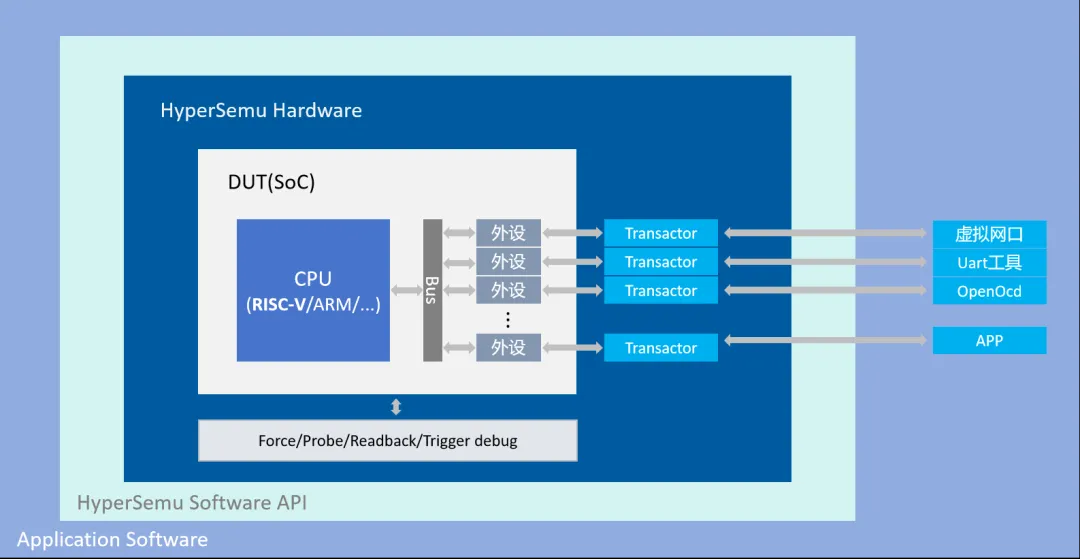

HyperSemu SoC(基于RISC-V、ARM等内核)加速验证解决方案通过使用硬件运行用户SoC设计、SoC内适配互联逻辑、提供外围Transactor等全套方案,实现用户定制化需求及实现数据传输的指数级加速。方案支持“裸机”运行和嵌入式Linux系统运行,方便用户调试CPU核和各外设接口,通过事务级Transactor应用,达到指数倍级仿真加速比,并配备Trigger、Force、Probe、Readback等高度灵活的调试方式,帮助用户快速收敛设计并达成验证目标。

HyperSemu SoC 加速验证解决方案实现框图

成熟高性能的FPGA原型验证

FPGA原型验证工具是高速执行RTL代码的理想平台,不仅可以在RISC-V内核开发阶段提供超高速的功能验证、回归测试等仿真验证能力,同时在系统级开发和软件堆栈的开发调试和全面验证等环节提供高性能RISC-V开发调试环境,并可作为CPU基准测试和性能评估的重要工具,测试RISC-V核及其SoC产品在不同软件负载下的运行。

亚科鸿禹是国内最早扎根FPGA原型验证领域的企业之一,已推出七代成熟产品(VeriTiger系列),单平台提供700万到近2亿ASIC门验证容量、支持跨平台级联扩展,提供全流程编译、运行调试自动化软件,提供丰富子卡资源用于各类接口的实景验证,服务全球500+数字芯片开发用户。在RISC-V开发验证领域,VeriTiger系列原型平台已充分适配香山处理器及多款国内知名RISC-V开发企业的高性能处理器核,为其提供高性能验证调试和系统级开发平台。

VeriTiger原型验证平台启动香山处理器核

专用RISC-V核指令调试器

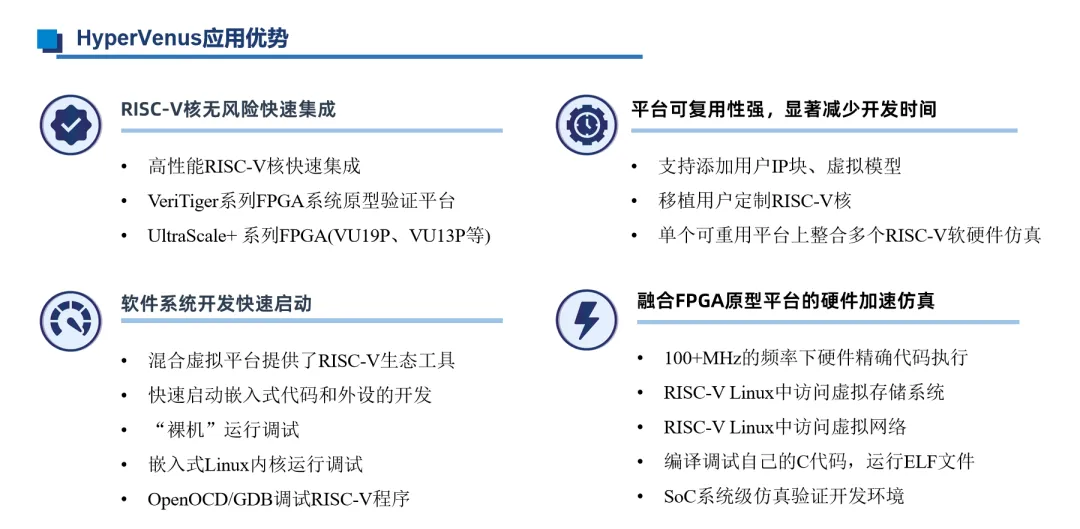

基于在RISC-V领域原型验证和硬件仿真加速应用实践,亚科鸿禹于2023年8月推出专为RISC-V客户定制开发的核指令调试器和SoC软硬件联合仿真开发环境--HyperVenus。基于VeriTiger系列FPGA原型验证硬件平台、融合HyperSemu硬件仿真加速功能,支持各种常见RISC-V型号。RISC-V开发者可以快速将设计部署到HyperVenus,快速运行ISA测试、C程序、启动Linux内核、调试Linux系统应用程序,完成系统级开发。

HyperVenus的关键优势在于其完善的“预构建”能力。HyperVenus原生适配3款亚科鸿禹拥有完整商业经营权的RISC-V核,同时亚科鸿禹团队持续深度开发常见RISC-V型号与HyperVenus平台的适配,提供预构建的Bitfile和系统级虚拟环境,使得HyperVenus不仅能帮助RISC-V内核开发工程师实现高效验证调试,还能帮助裸核和嵌入式应用程序开发工程师、操作系统开发工程师、CPU基准及性能测试工程师等各细分方向开发者快速构建软硬件联合仿真开发环境。

【注】HyperVenus产品理念及技术基础源于亚科鸿禹和原麻省理工学院(MIT)计算机科学与人工智能实验室(CSAIL)荣誉教授Arvind Krishnamurthy及其创立的Bluespec公司的合作交流。Bluespec, Inc. 是RISC-V基金会最早一批联合创始成员之一,对RISC-V技术的发展和推广做出了重要贡献。亚科鸿禹与Bluespec在RISC-V领域已保持十余年技术交流和产品合作。(Bluespec企业官网:https://bluespec.com/)

RISC-V教学课程建设落地方案

人才是产业生态建设的后备力量和创新源泉。亚科鸿禹基于对仿真验证EDA工具的多年研发与应用实践、对3款拥有完整商业经营权的RISC-V核及多款市场主流高性能RISC-V处理器的深度开发,总结梳理出一套面向RISC-V学习者从初学到深入的课程建设落地方案,提纲内容包括:RISC-V指令集基础概念、RISC-V开源社区体系、RISC-V 处理器案例代码解析、RISC-V软件工具链学习、RISC-V硬件加速仿真验证实训等,深入浅出带领学习者入门RISC-V开发。目前方案已经在部分高等教育院校的课程建设中得到应用。随着落地方案的更多应用,亚科鸿禹将持续深耕RISC-V产业人才培养,为产业生态建设注入不竭动力。

人工智能、物联网等前沿应用领域飞速发展驱动底层硬件不断寻求算力创新、功耗管控等性能提升新路径,RISC-V以其高度灵活、高能效及自由开发等优势将迎来应用爆发。然而RISC-V仍然面临应用生态、技术成熟度等诸多挑战。亚科鸿禹加入甲辰计划旨在基于团队在RISC-V领域的长期探索,进一步发挥亚科鸿禹作为“中国开放指令生态(RISC-V)联盟”和“中国RISC-V产业联盟”成员企业的产业联动作用,联合更多RISC-V生态伙伴,加速国产RISC-V EDA工具链开发应用,努力推动国产RISC-V技术成果普及落地及应用模式创新。

【甲辰计划(RISC-V Prosperity 2036)】由ASE实验室、PLCT实验室和算能(Sophgo)联合发起,旨在通过“联合100家以上芯片及方案厂商、500家以上软件企业,在18个以上基础关键行业领域完成面向RISC-V的适配与优化,合作完成超过1000款重要行业及商业软件的移植与部署”等方式,在下一个丙辰年(2036龙年)之前,基于RISC-V实现从数据中心到桌面办公、从移动穿戴到智能物联网全信息产业覆盖的开放标准体系及开源系统软件栈,使RISC-V软硬件生态达到或超过其它主流架构的生态成熟度。

关于亚科鸿禹

无锡亚科鸿禹电子有限公司,成熟的一站式SoC/ASIC仿真验证产品及解决方案供应商,国内最早从事FPGA原型验证和硬件仿真加速器工具研发与应用的团队之一。率先推出国内首款桌面级硬件仿真加速器产品,实现该领域技术破冰。在华大九天的全面支持下,着力部署“FPGA原型验证矩阵”、“企业级硬件仿真加速器”、“ESL高阶设计语言编译和仿真工具”、“逻辑综合器”等多款数字前端核心EDA工具的研发与市场推广,致力于成为“中国领先的数字前端EDA工具供应商”,助力国产数字EDA全流程自主可控。

公司总部位于江苏无锡,在北京、上海、合肥、西安设有研发中心,成都设有办事处,拥有近200人的人才团队,由具有20余年国际仿真验证从业背景的领域专家领衔,核心成员平均超过15年国内外知名EDA企业从业经验。公司与清华大学、合肥工业大学、江南大学等知名高校在EDA技术研发和人才培养方面保持长期产学研合作,共同推动国产EDA产业进程,助力中国半导体产业发展。公司的VeriTiger®系列原型验证产品和HyperSemu®硬件仿真加速器广泛服务于国内外知名集成电路设计企业、院校和研究所,应用于5G、人工智能、自动驾驶、AIoT、存储等前沿领域,全球累计用户超500家。

本文转载自:亚科鸿禹