11. RFSoC SDR的设计工具和工作流程

11.4 PS硬件软件合作设计

11.4.1 作为软硬件协同设计的Vivado工作流

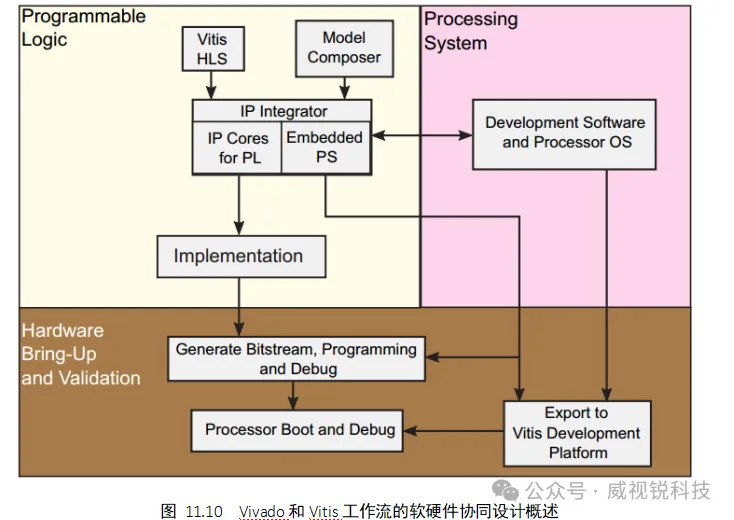

通过重新检查先前考虑的Vivado工作流,可以突出强调协同设计方法。图11.10说明了Vivado和Vitis生态系统中的这种集成设计方法,它包括分区但高度依赖的PL和PS设计、实现和硬件验证。

然后使用Vivado IDE进行合成、实现和比特流生成,从而对设备进行编程。动态函数交换(DFX)元素也可以在这里合并。设计的硬件和软件元素通常一起进行测试,例如,只有在硬件设计成功编程的情况下,才能对基于PS的驱动程序进行全面测试。同样,硬件中的功能通常通过由PS控制的AXI4-Lite接口进行配置、启用和操作。因此,调试和解决错误的过程是硬件软件协同设计方法的一部分——硬件设计中的错误修复需要在PS中进行测试,而PS中的更改需要使用硬件设计进行测试。

11.4.2 可选择的协同设计工具

一些第三方工具提供了硬件软件协同设计的替代方法,这些方法通常允许在单个开发环境中进行PL和PS设计,并有一个链接到“幕后”使用的Vivado版本来执行合成、实现和比特流生成。通常,同一个应用程序提供了一种方法来编程目标硬件设备并控制PS,从而允许完整的硬件软件协同设计。

1.MathWorks SoC Builder

如前面11.2.4节所讨论的,MathWorks HDL Coder工具可以用作抽象HDL和IP核生成的方法。通过额外集成SoC Blockset,可以创建一个完全代表Vivado IP集成商设计的模型设计,包括rfdc、PS控制和通过dma进行的内存管理。

利用额外的MathWorks工具,设计方法可以进一步扩展:如果链接了Vivado版本,则可以使用SoC Builder工具创建支持hdl的设计,生成比特流,然后下载并在目标SoC上执行。该工具提供了一个循序渐进的向导,指导用户通过Vivado工作流,而不离开Simulink IDE。相关的Vivado版本在此过程的后台运行,因此,在完成SoC Builder过程后,可以在Vivado中打开IP Integrator块设计。

假设目标评估板配置正确,并连接到运行SoC Builder的主机PC,则可以通过以太网从向导进行连接。生成的比特流可以加载到设备上,应用程序可以直接从IDE运行。

2.RFNoC for GNU Radio

射频片上网络(RFNoC)项目是SDR制造商Ettus ResearchTM的开源第三方软件工具,旨在简化将IP核集成到其通用软件无线电外设(USRP) SDR单元的信号处理链中。RFNoC可以用作GNU Radio软件的附加包,GNU Radio软件主要是用于系统设计的PS元素的开发环境。

RFNoC包支持硬件设计和GNU Radio一起进行软硬件协同设计。该软件包提供了选定的“RFNoC块”,其中添加了DSP功能,如FIR滤波器和FFT。这些模块可以与Vivado IP目录IP核以及使用AXI4接口的任何自定义IP核一起添加到GNU Radio设计中。与SoC Builder工具一样,RFNoC需要了解已安装的Vivado版本,该版本在后台用于执行合成、实现和比特流生成。

独特的是,RFNoC设计中的所有IP核都通过AXI4 Crossbar连接,这意味着可以在运行时改变处理链中的块顺序,而不会改变比特流。这为设计增加了很大的灵活性。缺点是延迟增加,因为样本必须在每个处理块之间通过这个AXI4 Crossbar,这意味着时间要求变得更大。

11.5 动态函数交换(DFX)

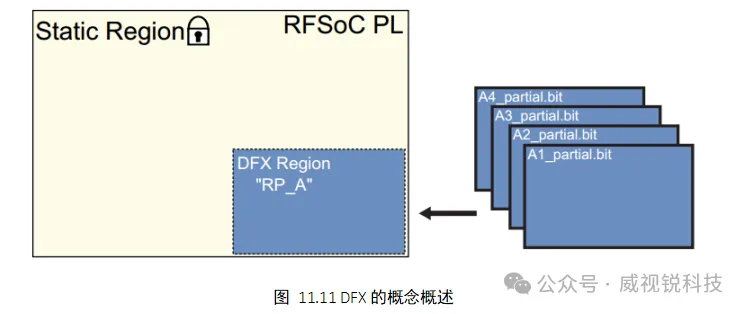

动态功能交换(DFX)是用于FPGA逻辑结构动态部分重构的AMD设计流程。该技术允许应用程序在硬件实现的不同功能块之间进行交换,而无需对整个设备进行重新编程。FPGA的硬件设计分为静态部分和许多可重新配置的分区,称为DFX区域。通过这种方式,生成一个比特流来实现FPGA的静态部分,同时创建几个单独的“部分”比特流,以用称为可重构模块(RMs)的子设计填充DFX区域。

由于RFSoC的PL部分相当于FPGA,因此可以将DFX方法应用于RFSoC上的SDR系统设计。RFSoC和DFX结合起来,提供了极其灵活的无线电实现的潜力。

11.5.1 DFX操作

DFX区域的概念如图11.11所示。黄色区域表示PL设计中的静态逻辑-这是保持功能的部分,并且不受通过加载部分比特流重新配置DFX区域的影响。

PL的DFX区域(由PL内的蓝色框限定)是可重新配置的分区。主比特流实现静态设计,包括在DFX区域外部放置和路由资源。每个部分比特流可以单独加载到设计中,以便在设计运行时重新配置DFX区域内的PL。由于围绕DFX区域的设计是静态的,因此对于所有配置,静态设计和DFX区域边界处的接口必须保持一致。通过在运行时替换PL子集,可以在资源和功率预算方面更有效地实现设计。例如,如果任意两组独立的功能不需要同时使用,则仅在需要时将它们加载到设计中。这可以显著节省功耗和实现整个系统所需的硬件资源。

11.5.2 安全及IP保护

DFX还可以用于增强专有设计的安全性。特别是,DFX支持使用非对称密钥加密(AKE)。该技术使用公钥和私钥对,其中RFSoC的静态部分在PL中存放私钥。可以随时生成可以与私钥配对的新公钥,但私钥受到保护。如果攻击者拦截传输并获得公钥,则在不知道私钥的情况下无法解密消息。

使用AKE方案进行PL设备配置,大部分设计都保存在加密的部分比特流中,将加密与DFX区域相结合以保护配置文件。静态区域仅包含用于解密的逻辑,并保护专有设计的其余部分。该系统确保即使RFSoC在通电时受到硬件攻击,私钥也很难访问,因为它驻留在PL中。此外,当设备未通电时,私钥不存在并且无法访问。这个用例与前面描述的在设计中交换由DFX区域实现的功能的用例不同,因为DFX区域可能只有一个部分比特流,而DFX区域可能包含大部分PL。

11.5.3 DFX的优势

除了前面概述的灵活性、资源和能源效率的好处外,DFX还提供了持续系统支持的好处。生成新的rm与现有静态设计合作的能力意味着可以使用相对较小的比特流文件将更新交付到已经部署的系统。这可能包括新特性和错误修复,以及更全面的新功能。

从Vivado 2021.1开始,DFX区域可以使用块设计容器在IP Integrator块设计中引入。通过应用这种方法,可重构模块可以作为子块设计包含在系统中。因此,SoC硬件设计(包括RFSoC器件)可以包括DFX功能,而不会偏离第11.4节介绍的Vivado协同设计方法。

SDR系统可以支持更大的DSP信号链、通信协议和硬件加速算法集,通过利用DFX技术根据需要交换功能,从而大大提高了无线电设计的灵活性。这有助于使RFSoC成为SDR应用的独特强大平台。

11.6 时钟,定时和采样率

11.6.1 AXI4协议时钟

正如本章前面所讨论的,IPI设计中的大多数IP核都是通过AXI4协议接口连接的,三种类型的AXI4总线(AXI4、AXI4- lite和AXI4 Stream)通常需要不同类型的时钟。如果使用这些接口类型的IP核包含在IPI设计中,则在IPI框图中的IP块上可以使用每个从机和主机接口的时钟端口。

这些时钟端口中的每一个都需要一个相应的复位信号,该信号由处理器系统复位IP核的一个实例驱动(时钟来自驱动各自的AXI4链路的同一源)。

11.6.2 射频数据转换器时钟和采样率

回想一下,RFDC本质上是分层的,大多数RFSoC器件都具有许多RF-ADC和RF-DAC片。每个片包含一个、两个或四个RF-DAC或RF-ADC,单个RF-DAC或RF-ADC称为块。

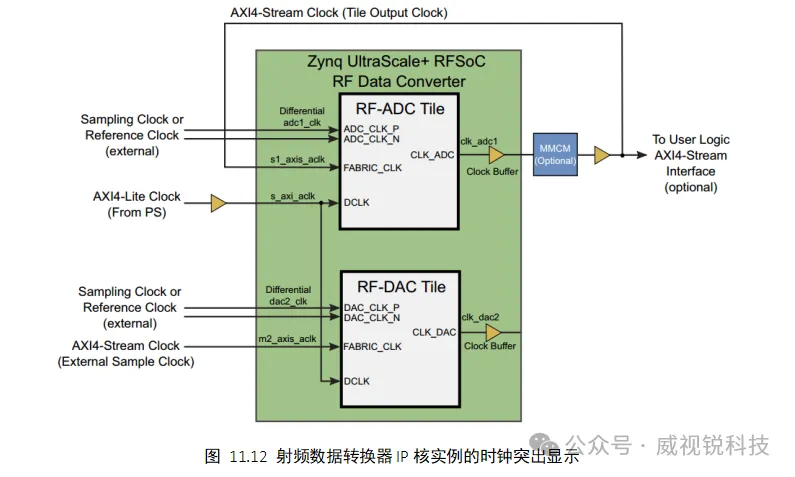

射频数据转换器IP核的高级概述如图11.12所示。

1.RFDC AXI4 -流接口时钟

AXI4-Stream接口通常用于在处理块之间传输数据,其中数据通过多个处理阶段连续传输,并且在一个IP核块的输出和下一个IP核块的输入之间传输。因此,通常需要将驱动该总线的时钟频率与通过IP核的数据的所需采样率相匹配。

对于具有RFDC的RFSoC设计,可以从外部fabric时钟或已启用的RF-ADC和RF-DAC模块的输出时钟提供AXI4-Stream接口时钟。

片的输出时钟频率可以从采样率的选定部分中选择。通过使用时钟向导IP核,可以在PL结构中进一步定制此频率,该IP核可以实现混合模式时钟管理器(MMCM)模块。通过这种方式,IP核可以生成与输入时钟具有定义的相位和频率关系的多个输出时钟。

示例:在图11.12中可以看到两个AXI4-Stream时钟。启用的RF-ADC片提供了一个输出时钟,它驱动相同片的AXI4-Stream输入,以及设计中以相同频率工作的其他IP的AXI4-Stream接口。另一方面,启用的RF-DAC块具有外部源提供的AXI4-Stream时钟。可以假设,在RF-DAC传输之前对数据进行操作的任何信号处理IP核也将由该外部源进行时钟处理。

2.RFDC AXI4和AXI4- Lite接口时钟

图11.12还提供了一个AXI4 - Lite时钟s_axi_aclk,它被输入到RFDC中所有已启用的块中,并允许基于PS的驱动程序重新配置RFDC。内存映射接口(如AXI4和AXI4Lite)提供PL和PS之间的连接,因此,这些接口类型通常从PL附加的引脚进行时钟处理。

3.平滑参考时钟

如图11.12所示,RFDC内的每个磁都有自己的差分输入时钟,该时钟可以来自采样时钟(时钟速率等于采样速率),也可以来自较低频率的参考时钟,该参考时钟可以使用内部磁片锁相环将其放大到采样速率。作为后者的参考时钟该方法包括一个额外的锁相环级,它提供了减少时钟抖动,创建一个“更平滑”的时钟。因此,这通常是对RFDC块进行计时的首选方法。

频率规划应该在rfdc设计之前考虑,因为频率规划将告知合适的采样率和锁相环参考时钟频率的选择。参考时钟可以选择为采样率的任意整数除法,由参考锁相环时钟(LMK)和射频锁相环时钟(LMX)提供。

LMK和LMX时钟必须在操作前使用寄存器进行编程。这可以使用主板的时钟编程连接器手动完成,也可以通过C或PYNQ Python驱动程序从PS控制。LMK和LMX时钟所需的寄存器编程配置可以从TICS Pro软件导出。编程的LMX输出频率应与RFDC瓦参考频率匹配。对于某些支持的评估板,包括ZCU111和RFSoC4x2,选择的LMX频率与PYNQ RFDC时钟驱动程序一起提供,以减少所需的设计工作量。在IP Integrator设计中,RFDC通过外部IO连接到LMX参考时钟。在图13.12中可以看到两个这样的接口,标记为差分adc1_clk和dac2_clk。

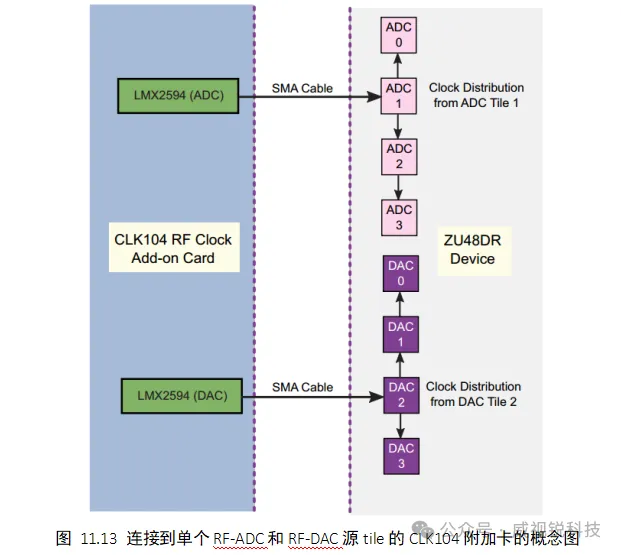

某些评估板,特别是那些具有第3代设备的评估板,只向某些块提供这种外部LMX时钟,并且需要时钟分配功能来使用其他块。例如,ZCU208评估板的LMK和LMX时钟通过CLK104附加卡9提供。该板上的ZU48DR器件包含4个RF-DAC和4个RF-ADC片,但是LMX时钟仅通过SMA电缆输出到DAC片2和ADC片1。要使用电路板上的其他DAC或ADC,必须在设计中启用这些模块,并将时钟分配到其他所需模块。图13.13进一步说明了这种时钟分配方法。

同步时钟

RFDC IP核也可以选择将系统参考时钟sysref作为输入。该输入信号对RFDC中的所有磁片都是通用的,并为多磁片和多设备同步提供时钟(如果在设计的系统中需要)。对于多磁片设计,sysref信号是连接到RFDC内的主磁片的外部输入。然后,这个tile充当其他tile同步的引用。

11.6.3 最大PL时钟速率

在RFSoC器件的PL部分(或一般在FPGA逻辑中)开发硬件设计时,设计人员应该了解两个最大时钟速率:

(i)器件的潜在最大时钟速率;

(ii)由用户设计产生的(通常略低的)最大时钟速率。

第一个是芯片的物理限制,通常在产品数据表中公布,并取决于已开发的硬件,以及设计师所做的选择;在DSP系统中,诸如算术字长规格和流水线的使用等因素可以影响可实现的时钟速率,以及PL的利用率百分比(PL使用得越充分,路由所有信号的任务就越具有挑战性,最大时钟频率可能越低)。

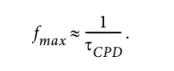

设计很少会实现接近设备最大值的时钟速率,因此,设计特定的时间指标通常是设计师更关心的问题。在简单的层面上,最大时钟频率受到关键路径延迟的限制,关键路径延迟是信号沿最长路径传播所花费的时间设计中两个时钟元件之间的组合逻辑路径(称为关键路径)。设计特定的最大时钟频率约为:

这种关系意味着设计中的所有信号必须在一个时钟周期内到达下一个时钟输入,否则,似乎在不需要的地方插入了一个1时钟周期的延迟,从而改变了实现的算法并可能导致不可预测的行为。为了防止亚稳态问题,也必须避免在触发器设置和保持周期内改变信号值。认识到设计中级联组合逻辑元素的数量和类型对其定时性能有重大影响,设计师通常可以通过识别关键路径并进行设计修改来缩短其时间来改善已实现的定时结果。

时间报告由Vivado生成,作为实现阶段的输出。时序报告详细描述了开发的硬件在目标设备上的时序性能,由以下因素决定:

时钟偏差和不确定性:时钟实现的效率,受时钟约束和输入时钟属性的影响。

逻辑延迟:信号在一个时钟周期内通过的逻辑元件(即组合硬件)相关的延迟。

网络或路由延迟:信号经过PL路由资源时产生的延迟。这取决于设计的位置和路由(由Vivado使用可选的用户指令执行的过程)。

当设计的时序性能至关重要时,可以优化这些因素中的一个或多个。

在进行任何优化时序性能的尝试之后,对于特定设计,持续失败的“满足时序”意味着所需的时钟速率高于PL可以支持的速率。这意味着必须降低时钟速率。

在期望的采样率非常高的情况下,例如靠近PL和RFDC之间的接口,这可能会促使设计更改,例如增加RFDC中进行的抽取或插值的数量,以允许在PL中使用较低的采样率。在数据速率必须保持高的情况下,可以使用SSR接口来增加数据宽度。通过这种方式,可以在保持所需数据速率的同时降低时钟速率。

11.6.4 超采样率(SSR)

超级采样率(SSR)技术涉及使用复制硬件并行处理连续样品块,而不是传统的逐个样品处理。当采用SSR时,可以在较低的时钟频率下支持所需的采样率。例如,SSR值为8意味着时钟频率降低了8倍(与传统的逐样本架构相比),而不会降低总体采样率。因此,实现硬件的资源成本增加了大约8倍。

示例:RFSoC设计具有RF-ADC tile到PL AXI4-Stream接口。希望以500 MHz的速率通过特定的自定义IP核传递数据,但是可实现的最大时钟速率为410 MHz。为了满足这些设计要求,可以采用SSR 2实现。通过每个时钟周期并行传递两个数据样本,所需的时钟速率可以从500 MHz减半到250 MHz,从而轻松满足适用的时间限制。这两种设计如图11.14所示,SSR将在下一节进一步讨论。

SSR接口在系统的常规部分和SSR部分之间进行转换。SSR可能最有可能在RFDC和PL之间的接口上用于RFSoC。这里,它可以通过RFDC IP核引入设计:通过将“每个AXI4-Stream周期的样本”参数增加到大于1的整数值,在RFDC和PL之间创建SSR接口。

许多常用的内核,包括FIR Compiler IP内核,都提供了对SSR的支持。此外,Model Composer库包含一个完整的SSR块集(通过System Generator DSP支持),允许使用SSR接口生成自定义IP核。通过精心设计,整个设计中的AXI4-Stream接口可以与SSR实现集成,大大降低了所需的时钟速率。

文章来源:威视锐科技