作者:Sandy Macnamara,AMD工程师;来源:AMD开发者社区

我们将使用 Clocking Wizard 文档 PG321 中的“通过 AXI4-Lite 进行动态重配置的示例”章节作为参考。

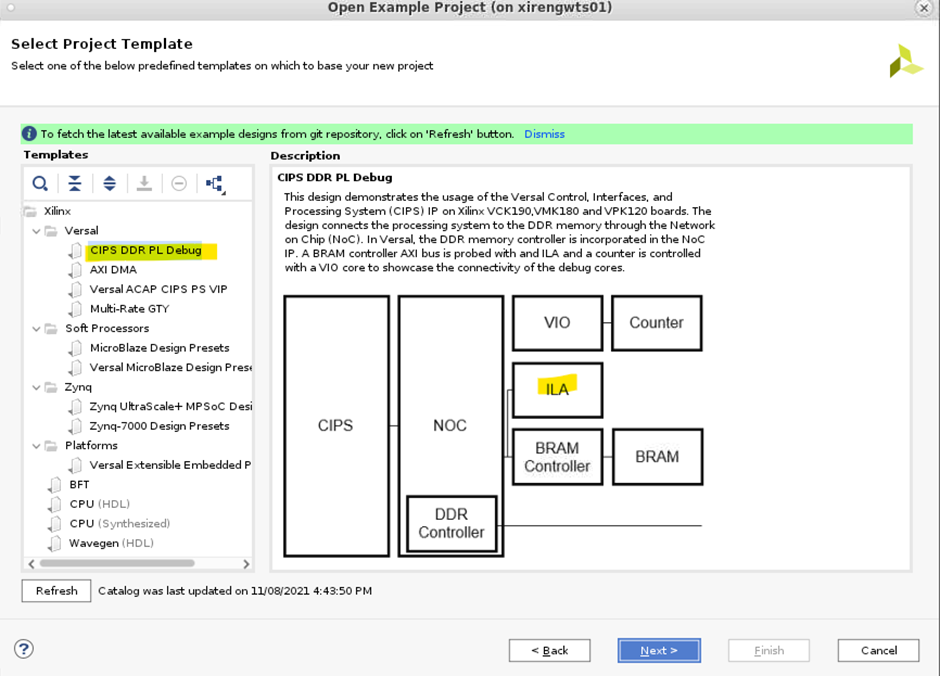

首先在 Vivado 中构建工程。我将使用 VCK190 评估板。

您可使用 Vivado 中的实用设计示例作为起点。选择 CIPS DDR PL 调试示例,其中 CIPS 已为您设置完成。

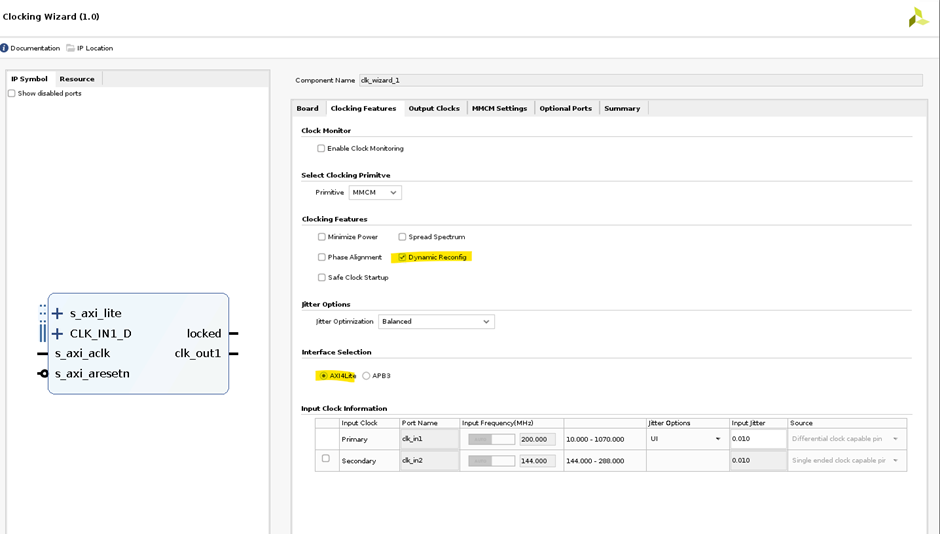

在块设计中,将 Clocking Wizard 添加到图形界面中。鉴于我们使用的是 VCK190,因此设置 CLK_IN1 = LPDDR4 SMA CLK2。

在“Clocking Features”(时钟特性)选项卡上,选中“Dynamic Reconfiguration”(动态重配置)选项卡,保留“Interface Selection”(接口选择)的设置“AXI4Lite”不变。

在“Output Clocks”(输出时钟)选项卡上,选择两个输出时钟:100 MHz 和 50 MHz。

Clocking Wizard 将生成 _drp_address_map (MIF) 文件,其中包含地址和值列表,与 Wizard 中请求的值相对应。

您也能使用要重新配置的值来创建第二个 Clocking Wizard,以便生成重配置时要写入的地址和数据。

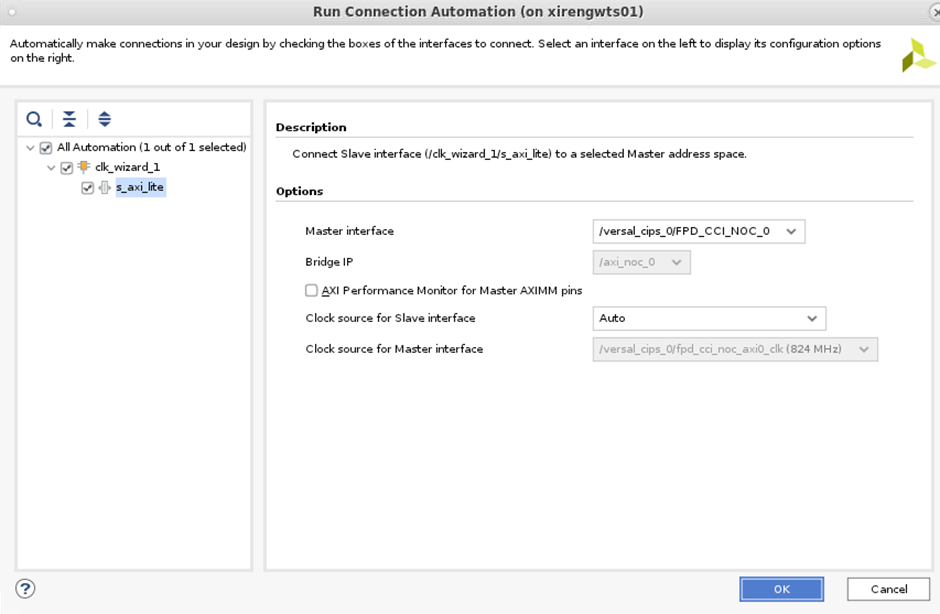

您可选择“Connection Automation”(自动连接),这样将设置 Bridge IP 以将 AXI4-Lite 转化为 NOC/CIPS 上的 AXI 接口。

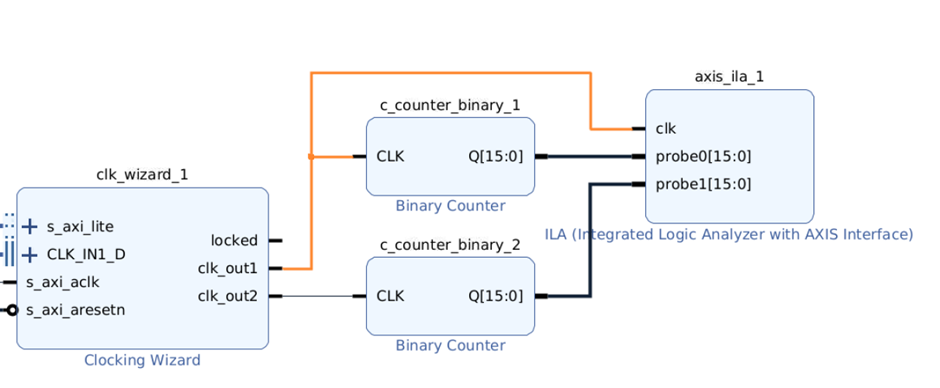

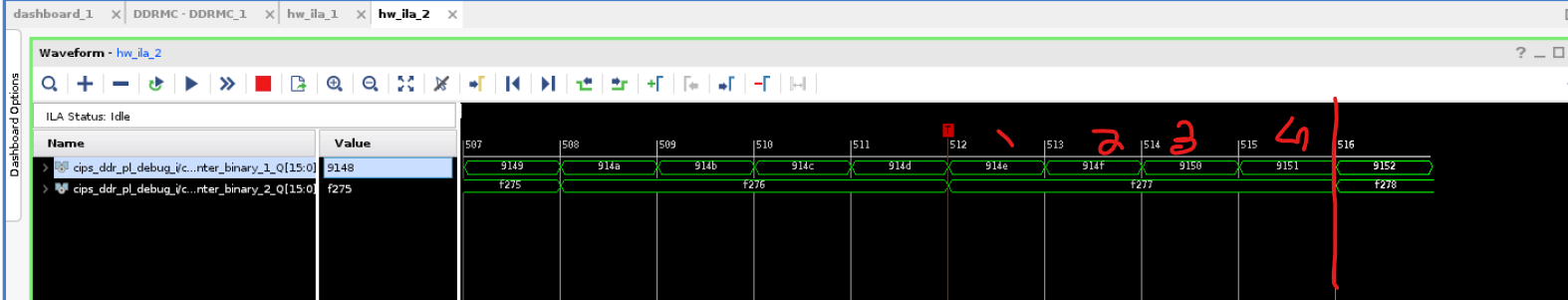

在此示例中,我输出了 2 个时钟。这些是 ILA 捕获的 100 MHz 和 50 MHz 时钟计数器,我们可以比较这 2 个计数器来直观显示相对频率。

此处随附了 BD Tcl 供您参考:

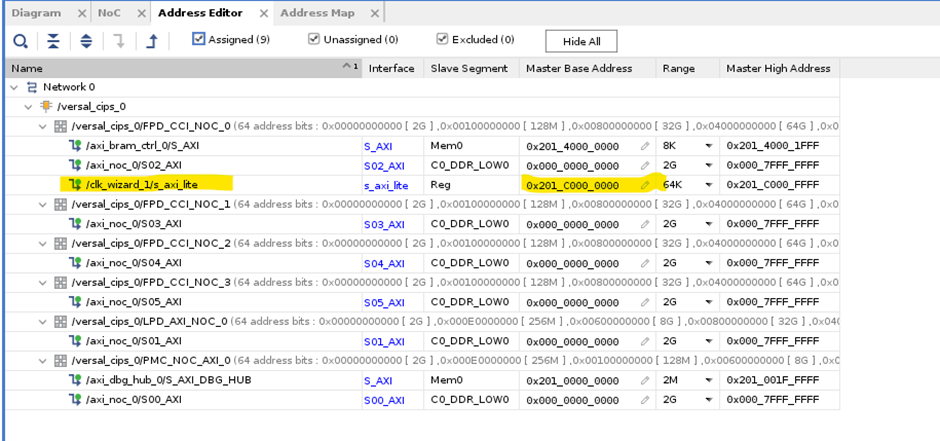

在“Address Editor”(地址编辑器)中,您可看到 Clock Wizard 的“Base Address”(基地址)。在我的 Clock Wizard 实例中,“Base Address”为 0x201C0000000。

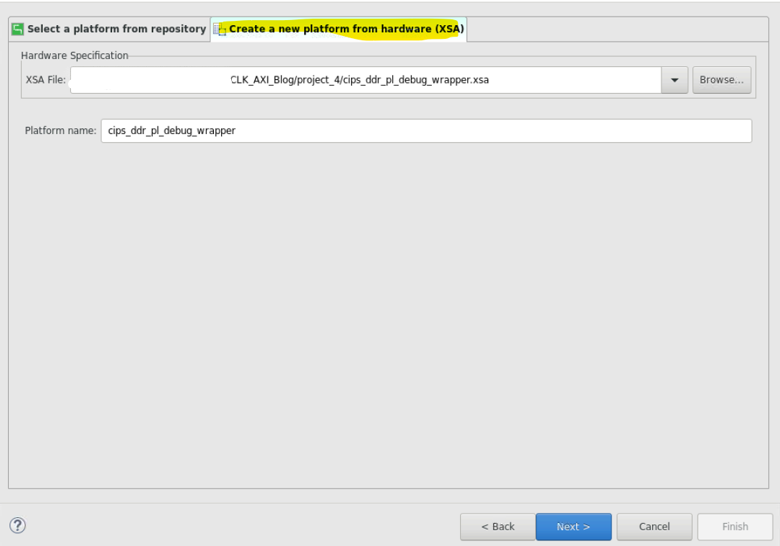

运行实现,并写入器件镜像。然后选择“Export -> Export Hardware”(导出 > 导出硬件)并选择“Include device image”(包含器件镜像)。这样会生成包含 Clock Wizard 的 XSA 文件。

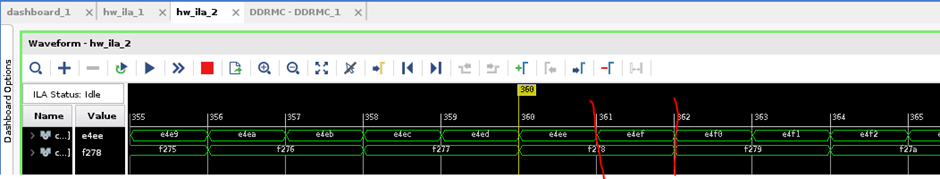

在此阶段,您也可以下载 PDI 并进行检查。您会看到其中一个计数器的速率是另一个计数器的两倍。

CLK_OUT1 工作频率为 100 MHz,时钟设置为 c_counter_binary_1。CLK_OUT2 工作频率为 50 MHz,时钟设置为 c_counter_binary_2。

因此,c_counter_binary_1 的工作频率是 c_counter_binary_2 的两倍。

要启动 Vitis,请转至“Tools -> Launch Vitis IDE”(工具 > 启动 Vitis IDE),并选择或创建工作空间。

选择“Create Application Project”(创建应用工程),在“Platform”(平台)选项卡上,选中“Create a new platform from hardware (XSA)”(基于硬件创建新平台 (XSA))

为您的应用工程命名。“Domain”(域)保留默认设置。

对于“Templates”(模板),如果您的 XSA 中有 UART(对于 VCK190,UART 包含在 CIPS 中),那么您可以选择“Hello World”,否则,您可以选择“Empty Application”(空应用)。

我们已知 Clock Wizard 基地址为 0x201C0000000。在 Clocking Wizard 中,使用 PG 读取 LOCKED 状态,OFFSET 为 0x4。

您可利用 Xil_In32 和 Xil_Out32 通过 AXI 直接读取和写入地址。

// C_BASEADDR + 0x04 Status Register (SR)

Lock_reg =Xil_In32(0x201c0000004);

xil_printf("Locked %x", Lock_reg);

在示例中,我将把 CLKOUT2 从 50 MHz 重配置为 25 MHz。

以下是第二个 Clocking Wizard 的 drp_address_map (MIF),其中 CLKOUT2 设为 25 MHz(而不是 50 MHz)。

在地址 0x201c0000344 处,写入数据 0x1e1e。

// C_BASEADDR + 0x00000344 write 0x1e1e

Xil_Out32(0x201c0000344, 0x1e1e);

下一步是写入并应用该 DRP 值以配置地址:C_BASEADDR + 0x014,搭配 0x00000003 以设置 LOAD 位和 SEN 位

// C_BASEADDR + 0x014 with 0x00000003 to set the LOAD and SEN

Xil_Out32(0x201c0000014, 0x3);

Finally check that Lock has reasserted.

Lock_reg =Xil_In32(0x201c0000004);

xil_printf("Locked %x", Lock_reg);

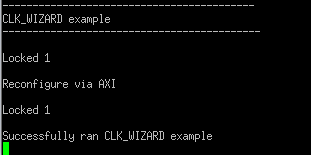

在终端上您会看到:

返回到 ILA 并观察 c_counter_binary_1 的计数结果是否是 c_counter_binary_2 的 4 倍。

Clocking Wizard 包含软件驱动程序,其中包含的示例在使用 AXI DRP 时也很有帮助。

https://github.com/Xilinx/embeddedsw/tree/master/XilinxProcessorIPLib/drivers/clk_wiz