AI Engine 架构

1. AI Engine 架构

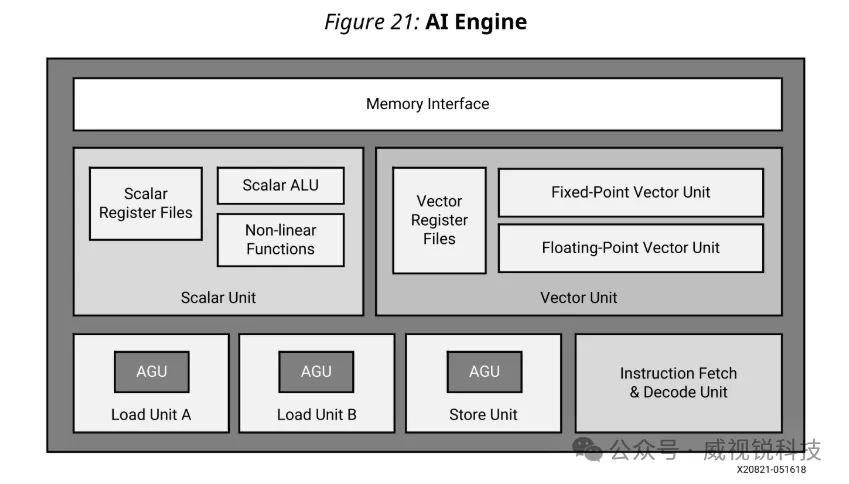

AI Engine是一款高度优化的处理器,具有单指令多数据(SIMD)和超长指令字(VLIW)处理器,支持定点和浮点精度。如下图所示,AI Engine 有一个内存接口,一个标量单元,一个向量单元,两个加载单元,一个存储单元,以及一个指令提取和解码单元。

AI Engine的特性包括:

32位标量RISC处理器○通用指针和配置寄存器文件

支持非线性函数(例如:sqrt、Sin/Cos和InvSqrt)

标量ALU,包括32 x 32位标量乘法器

支持标量定点和标量浮点之间的数据类型转换

三个地址生成器单元(AGU)

支持多种寻址模式:固定、间接、后增量或循环

支持快速傅立叶变换(FFT)地址生成

两个AGU专用于两个加载单元

一个AGU专用于存储单元

矢量定点/整数单元

多个矢量通道上的并发操作

矢量定点/整数单元

多个矢量通道上的并发操作

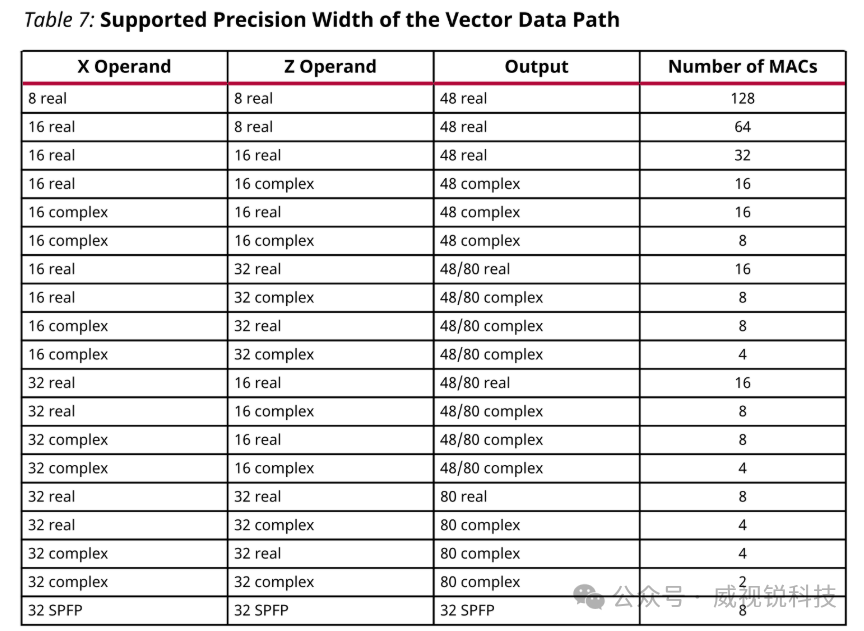

为复数和真实的操作数提供多个精度(见表7)。

注意:虽然cfloat是向量数据类型,但AI Engine向量处理器不直接支持它。必须发出两个指令。

可配置为执行8个复杂的16位乘法

具有32位粒度的全置换单元

具有多种舍入和饱和模式的移位、舍入和饱和

两步后加沿着768位中间结果

X操作数为1024位宽,Z操作数为256位宽。在组件使用方面,考虑表7中的第一行。乘法器操作数来自相同的1024位和256位输入寄存器,但某些值会广播到多个乘法器。有128个8位单乘法器,结果被后加并累加到16或8个累加器通道中,每个累加器通道为48位。

单精度浮点(SPFP)向量单元○使用与定点向量单元相同的置换

多个向量通道的并发操作

每个周期八个单精度乘法器(MAC)

平衡流水线

每个功能单元上的不同流水线(最多8级)

加载和存储单元管理数据存储器的5周期延迟

三个数据存储器端口

两个加载端口和一个存储端口

每个端口以256位/128位矢量寄存器模式或32位/16位/8位标量寄存器模式工作。8位和16位存储器以读-修改-写指令的形式实现

所有三个端口的并发操作

任何端口上的存储体冲突使整个数据路径停顿

超长指令字(VLIW)功能

向所有功能单元并发发布操作

支持多种指令格式和可变长度指令

使用一个VLIW字可以并行发布多达七个操作

直接流接口

两个输入流和两个输出流

每个流可以配置为32位宽或128位宽

一个级联流输入,一个级联流输出(384位)

与以下模块的接口

锁定模块

失速模块

延迟和跟踪模块

事件接口是来自AI引擎的16位宽输出接口

2. 寄存器文件

AI引擎有几种类型的寄存器。一些寄存器用于不同的功能单元。本节介绍各种类型的寄存器。

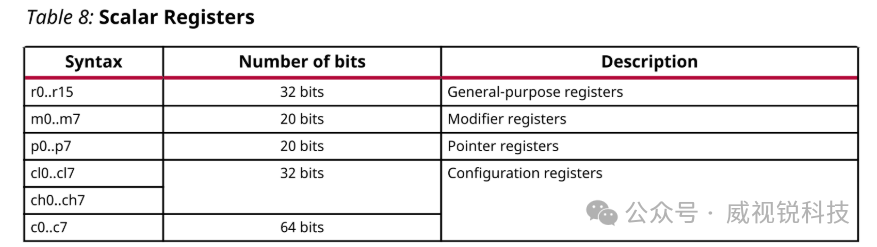

(1)标量寄存器

标量寄存器包括配置寄存器。寄存器描述见下表。

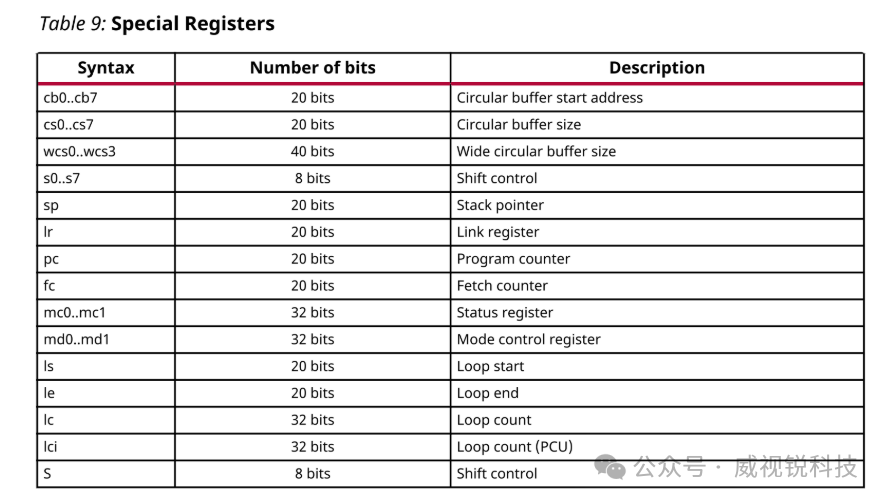

(2)特殊寄存器

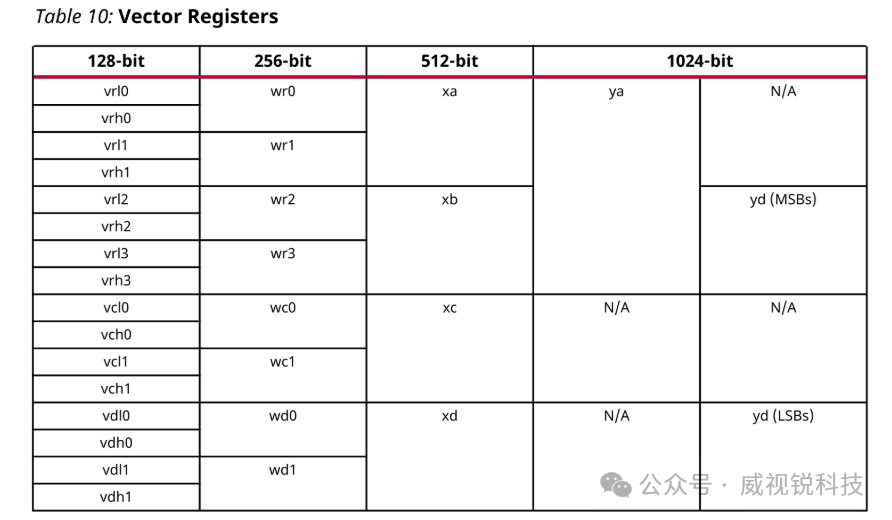

(3)向量寄存器

向量寄存器是允许SIMD指令的高宽度寄存器。底层基本硬1件寄存器为128位宽,前缀为字母V。两个V寄存器可以组合成一个前缀为W的256位寄存器。WR、WC和WD寄存器成对分组,形成512位寄存器(XA、XB、XC和XD)。XA和XB构成1024位宽的YA寄存器。对于除YD之外的所有寄存器,顺序为从表顶部的LSB到表底部的MSB。对于YD,LSB来自XD,MSB来自XB。

即:YD = VDL0::VDH0::VDL1::VDH1::VRL2::VRH2::VRL3::VRH3

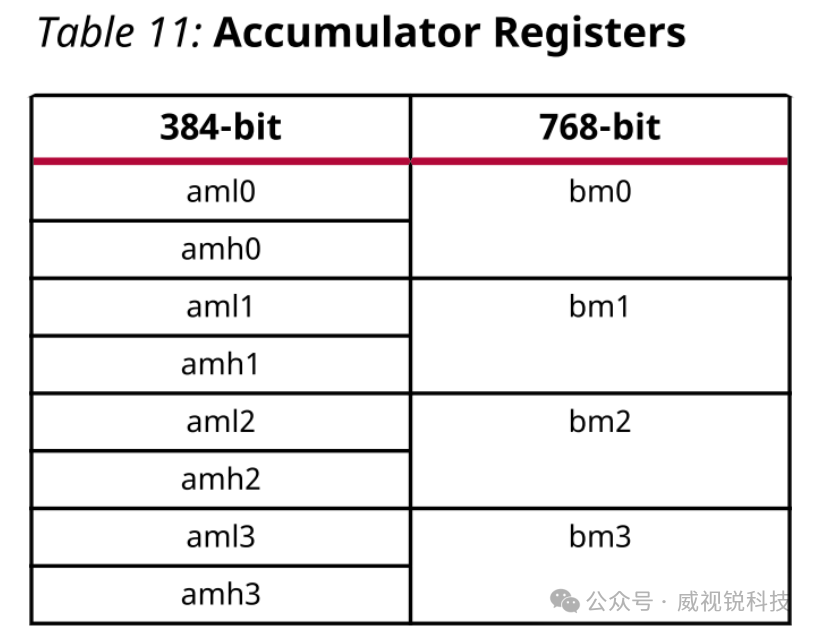

(4)ccumulator Registers

累加器寄存器用于存储向量数据路径的结果。它们是384位宽的,可以看作是8个48位的向量通道。这个想法是有32位乘法结果,并在没有位溢出的情况下对这些结果进行累加。16个保护位允许最多216次累加。累加器寄存器的前缀是字母AM。其中两个被别名化以形成以BM为前缀的768位寄存器。注:有两种操作模式。在第一模式中,在累加之前,使用16次后加法将乘法结果后加到8次加法中。在第二模式中,在累加之前,使用8次后加法将乘法结果后加到16次加法中。

3. 指令提取和译码单元

指令提取和解码单元将当前程序计数器(PC)寄存器值作为地址发送到程序存储器。程序存储器返回所提取的128位宽指令值。然后对指令值进行解码,并将所有控制信号转发到AI引擎的功能单元。AI引擎上的程序内存大小为16 KB,允许存储1024条128位的指令。

AI引擎指令为128位宽,支持多种指令格式和可变长度指令,以减少程序内存大小。在大多数情况下,当使用所有VLIW插槽时,需要完整的128位。然而,对于外循环、主程序、控制代码中的许多指令,或者偶尔的内循环的前置码和后置码,较短格式的指令就足够了,并且可以用于存储具有小指令缓冲器的更压缩的指令。

4. 装载和存储单元

AI引擎有两个加载单元和一个用于访问数据存储器的存储单元。数据加载或存储在数据存储器中。每个加载或存储单元具有地址生成单元(AGU)。AGUA和AGUB是加载单元,存储单元是AGUS。

每个AGU具有来自P寄存器文件的20位输入和来自M寄存器文件的20位输入(参考寄存器文件中的指针寄存器和修改器寄存器)。AGU具有一个周期延迟。

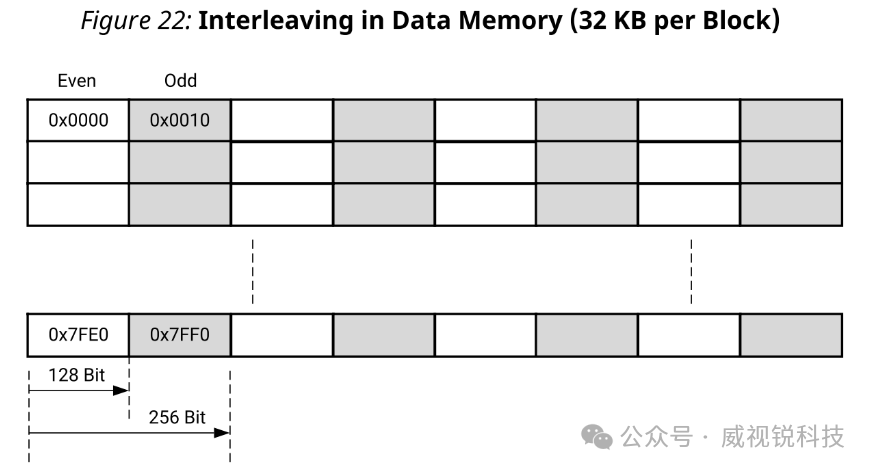

单个数据存储块为32 KB。AI引擎访问四个32 KB数据存储块以创建一个128 KB单元。这四个内存块位于AI引擎的每一侧,并被划分和交错为奇数和偶数组(见下图)。

文章来源:威视锐科技