作者:Embedded Computing Design 编辑团队,文章来源:Embedded网站

在过去十年中,电子设计领域的核心关键词之一就是“效率”。在设计流程中寻找效率,不仅能加快产品上市速度,还能通过在数据、能量与热量传输路径上的创新,实现更低的运营成本、更长的产品生命周期以及更小的环境影响。

如今备受关注的是:提升效率的重要性本身正在迅速上升。曾经只是“超前思维”的理念,如今已成为企业成功与产品在市场中长期存续的关键因素。

从最基本的层面来看,芯片设计成功的最高标准就是“效率”。随着芯片集成度的不断提高,制造商必须依赖更先进的热管理方案,并探索降低功耗的新方法。这一点在高端 FPGA 和 SoC 中尤为重要——它们常被部署在远远超出消费级电子产品标准的高热、高电压或高物理应力环境中。

在本文中,笔者将探讨 AMD 在芯片架构和热管理方面的一些创新,并说明这些创新如何帮助开发者打造更加高效、紧凑的产品。

热管理方案(Thermal Solutions)

芯片正变得日益复杂,同时,随着每一代工艺节点的推进,芯片面积却在缩小。现代应用对性能的需求也在持续提升,芯片运行频率越来越高。所有这些因素导致的结果就是:功率密度不断上升,热量必须更高效地被传导出去。

AMD 最近发布了一篇白皮书,介绍了其在无盖封装技术(lidless packaging technology)方面的最新进展。这一创新大幅提升了散热效率,从而降低了功耗、成本、体积与重量。这也意味着开发者能够将其设计部署到更广泛的环境温度范围中,而在某些应用中,温度适应性正是热性能的最关键指标。

在无盖封装中,芯片顶部的封装盖和一层导热界面材料(TIM)被移除,使芯片裸露面可以直接与客户定制的散热方案相接触。这种结构带来多项优势,其中之一是:开发者可以以更灵活的方式优化其热管理设计,这是传统带盖封装所无法做到的。除去封装盖减少了热传导层数,裸露芯片面还允许开发者根据实际应用选择最合适的导热材料(TIM)。此外,在预生产阶段乃至产品其他生命周期阶段,开发者都可以移除散热器,对 TIM 的覆盖情况进行检查和优化。对于那些追求极高可靠性的应用,这一能力至关重要。

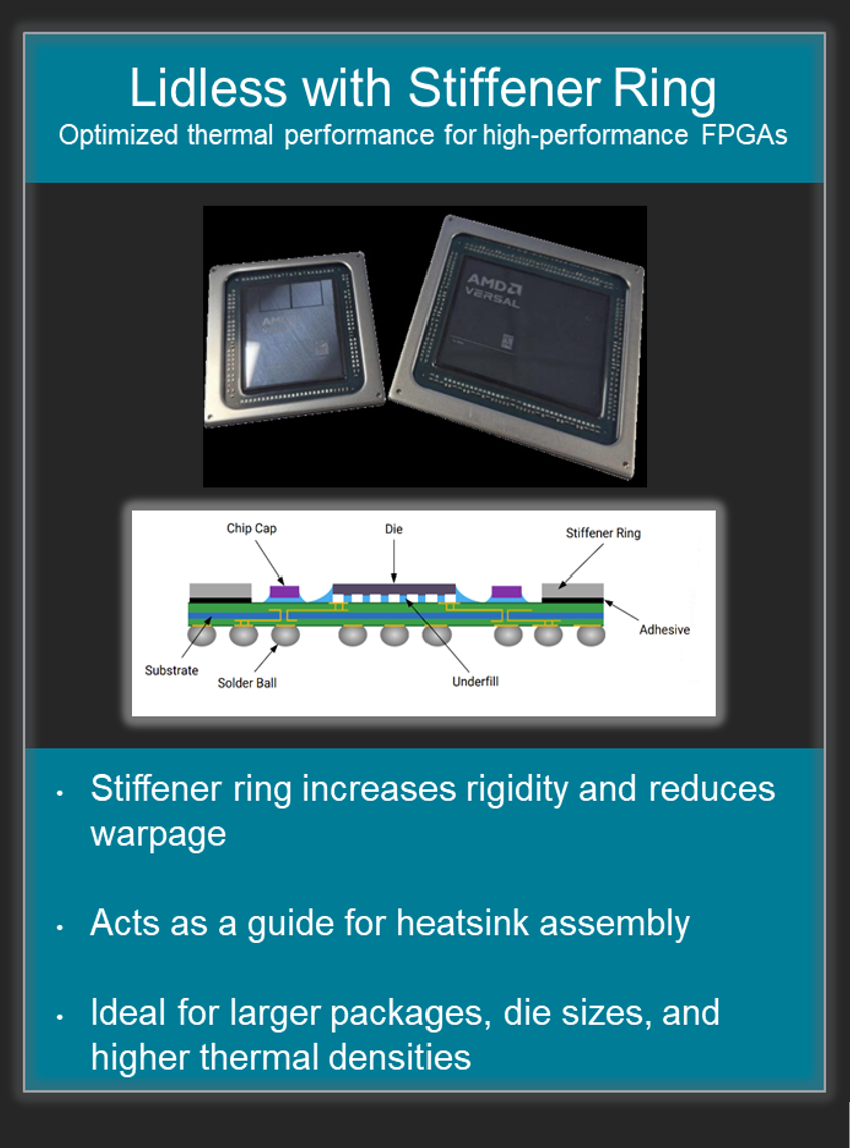

然而,正如所有由不同热膨胀系数材料构成的结构一样,芯片在极端温度下也会发生翘曲(warpage)。芯片与封装尺寸越大,这种翘曲现象就越明显。对于那些成本优化型的小尺寸 FPGA 或 SoC,这并非大问题;但对高端 FPGA 来说,由翘曲引发的水平偏移更加严重,问题又因其工作环境更为严苛而进一步放大。而传统带盖封装因为封装盖具有一定刚性,能增强整体结构,因此翘曲影响相对较小。

为了解决无盖封装的结构变形问题,AMD 推出了 “无盖加强环(lidless with stiffener ring)封装”。这种封装在芯片顶部外围集成一圈不锈钢加强环(呈方形或矩形),同时保持芯片核心区域裸露。这样即模拟了封装盖的结构支撑功能,又保留了裸片散热的优势。

下面的图像展示了这两种封装类型的对比:

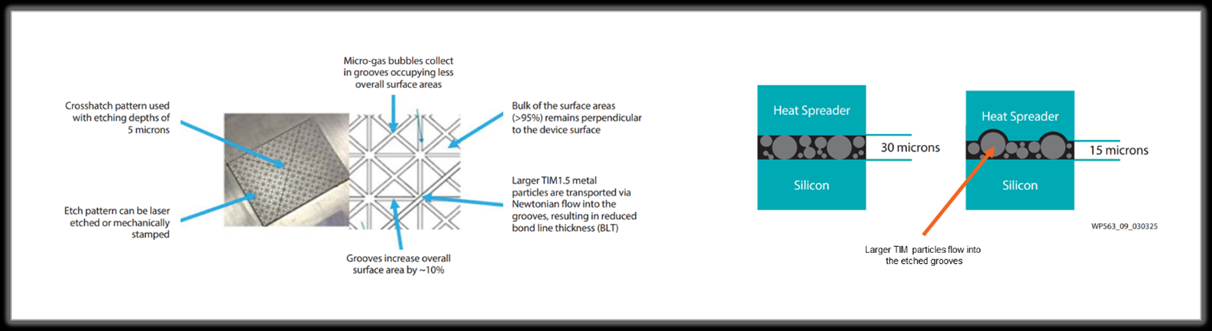

此外,AMD 还为无盖封装与相变材料(PCM)导热层开发并专利了一种散热器蚀刻图案。通过在散热器底面蚀刻交叉纹理图案,可减薄 TIM 厚度,提升热传导效率。AMD 提供该图案的机械设计图,并授权客户在 AMD FPGA 与 SoC 上使用该图案。

AMD 高级技术市场经理 John Heslip 表示,经过验证的 AMD 无盖封装设计在散热方面表现出色,在某个实际案例中实现了 24°C 的温度下降 和 约 50% 的静态功耗降低(详见白皮书)。这样的功耗与热性能提升,是很难仅通过半导体工艺改进或 RTL 设计优化来实现的。

硬核 IP 与可编程片上网络(NoC)

AMD 持续创新的另一重要方向是 硬核 IP(Hard IP)集成。你可能已经读过我之前关于 AMD Versal RF 系列(自适应 SoC)的文章,我曾提到硬核 IP 集成在尺寸、重量和功耗(SWaP)方面所带来的显著优势。而在本文中,我们聚焦于其中一项特别的硬核 IP 创新 —— 可编程片上网络(NoC),它为芯片内所有主要模块提供互联能力。

与一些 FPGA 厂商仅在特定器件、产品系列或芯片某一轴向实现 NoC 硬化不同,AMD 的可编程 NoC 覆盖所有 Versal 自适应 SoC,且支持芯片横向与纵向的数据通信。它构成了一条芯片内部的数据“高速公路”。由于该 NoC 专为封装并传输 AXI 总线协议流量而设计,而几乎所有现代 FPGA 设计都使用 AXI,总线通信硬化成 IP 模块便成为一个巨大的优势。

AMD 可编程 NoC 将处理系统、可编程逻辑、DDR 内存控制器及其他硬核 IP 互联起来。根据 AMD NoC 白皮书的数据,这一设计显著增强了整个芯片内的数据流。此外,AMD 在白皮书中还指出,可编程 NoC 有助于开发者降低通信延迟、减少逻辑资源占用、缩短设计构建时间并降低系统级功耗。白皮书还提到,若设计中大量使用该可编程 NoC,还可能带来额外收益 —— 减少所需自适应 SoC 的资源密度。

尽管片上网络技术已经较为成熟,AMD 最近仍推出了 “模块化 NoC 流程(Modular NoC Flow)”。简而言之,这项工作流程支持在 RTL 设计中直接集成 NoC。AMD 技术市场经理 Anthony Eid 表示,客户强烈希望能在 RTL 流程中灵活调用 NoC。通过模块化流程,开发者现在可以在 RTL 中实例化端点,并为 NoC 设定约束。Anthony 还指出,这项功能是很多习惯使用 VHDL 或 Verilog 的传统 RTL 工程师长期呼吁的。

NoC 的另一个关键优势在于它对设计构建时间的影响,这直接决定了开发者每天可完成的迭代次数。若充分利用 NoC,AMD 白皮书中的基准数据表明,构建时间最多可减少 50%。这显著提升了开发效率,加快产品上市速度——这是任何项目成功与否的关键效率指标。

尽管这与 NoC 无直接关系,AMD 也已针对 Versal 自适应 SoC 推出了“高级流程(Advanced Flows)”,同样以缩短构建时间为目标。由此可见,AMD 在提升开发者生产力方面确实投入巨大。

效率提升固然能带来更好成果,但真正的挑战往往来自物理极限。而 AMD 推出的 无盖+加强环封装、散热蚀刻图案、可编程硬核 NoC 等创新,证明了即使面对物理限制,依然可以实现令人瞩目的进步。

让我们共同期待下一次技术演进的到来!