AMD即将推出成本优化型 Spartan UltraScale+ 系列

judy 在 周三, 07/05/2023 - 17:02 提交

该新系列非常适合需要低功耗和高 I/O 的成本敏感型应用,其面向广泛的行业

该新系列非常适合需要低功耗和高 I/O 的成本敏感型应用,其面向广泛的行业

Vitis高层次综合可通过在选定的 AMD 器件上将 C/C++ 代码综合为可编程逻辑的 RTL 代码

时钟是每个 FPGA 设计的核心。如果我们正确地设计时钟架构

作为一名刚入坑的新手小白,我将分享自己的一些建议

PetaLinux编译Microblaze的U-Boot时,遇到下列错误

内存的稳定性,离不开RAS功能。提起RAS,熟悉DDR的小伙伴们一定记得行地址选通信号

本文讲一下随路时钟,什么是随路的时钟呢?

本文介绍Xilinx所有FPGA芯片型号IDCODE的获取方法

展示了基于领先的 AMD FPGA、自适应 SoC 以及 AMD EPYC™ 处理器的通信领域解决方案

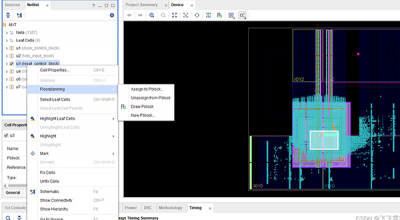

本小节对时序约束做最终的总结